作者:MOHAMMED TAWFIK ABDELHAFEZ

曾幾何時,您學習了電路理論,并學到了許多分析電路的技術。兩個著名且類似的技術是節點電壓分析和網格分析。在節點電壓分析中,首先選擇一個成為參考節點的節點。假定該節點具有絕對零電勢,我們通常將其稱為“接地”節點。

只要您不關心電路與其他對象之間的電壓關系,就不會發現此假設有害。許多子電路之間共有的節點通常是數學上簡化電路分析的一個很好的選擇。

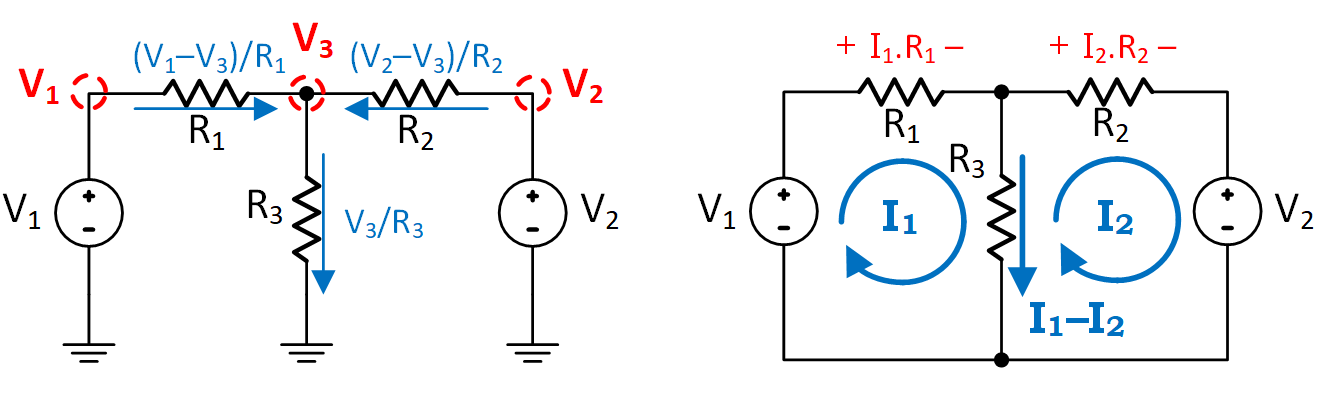

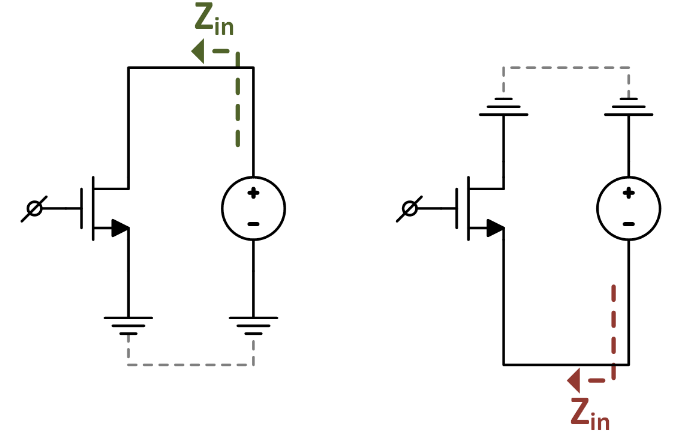

當我們學習電子電路專業課程時,通常會忘記許多電路分析技術,例如疊加,戴維南等效項,諾頓等效項和網格分析。我們主要關注一種技術,即節點電壓分析(圖1)。

圖1節點電壓分析通常簡化了電子電路的分析。左側是節點電壓分析的示例,右側是同一電路的網格分析。

經過多年作為學生和工程師的專注之后,您可能會忘記電路理論中的一些基本概念。這是致命的錯誤觀念滲入我們的思想的時候。

常見誤解

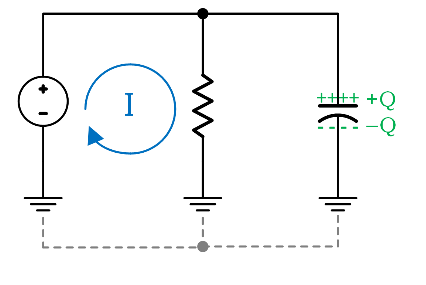

地面節點通常被認為是所有電荷的物理墓地,但事實并非如此。地面節點僅僅是我們個人選擇的節點。除了通常與許多子電路通用外,它沒有什么其他的特殊之處。成為公共節點不會增加特殊的物理屬性。接地節點上唯一存儲的電荷是電容器的負極板電荷,電容器的一個端子接地。所有其他電荷在電路中循環,并且永不停止(圖2)。請記住,所有電流都在一個回路中流動,電荷返回其源極。

圖2電流電荷循環循環。接地節點上唯一存儲的電荷(–Q)是屬于接地電容器的電荷。

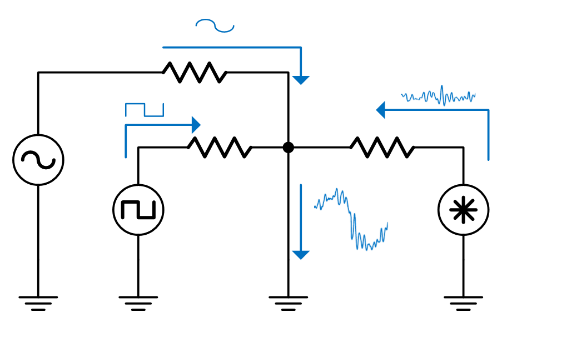

地面節點是避開噪音的避風港。但是,大多數不同的噪聲電流都通過接地節點(圖3)。然而,僅對于設計良好的接地軌而言,軌的阻抗可忽略不計,從而使整個軌上的噪聲電勢差幾乎為零。

圖3不同的信號電流和不同的噪聲電流通過接地節點。至少在直流電路分析中,接地軌的低阻抗是保證軌中任何兩個物理點之間的電勢差可以忽略的唯一保證。

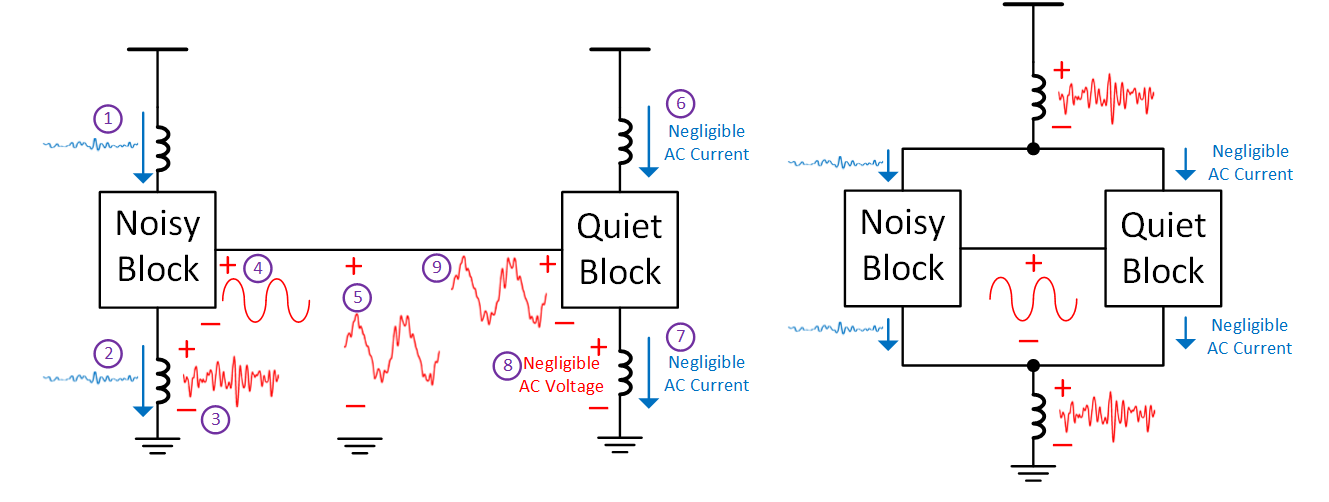

人們普遍認為,將兩個相互影響的域的接地墊分開可以保護安靜的域免受嘈雜的域的影響。這可能是RF工程師可能在不知情的情況下犯下的最嚴重的罪行之一。接地焊盤的分離在許多情況下可能會導致從噪聲域輸出到安靜域輸入的嚴重噪聲耦合。您可能會發現這種反常理,但是當使用鍵合線繪制完整的電路(直至PCB層)時,這一點變得很清楚,如圖4所示。當所有MOS體連接器都連接到專用接地焊盤時,也會發生類似的動作。

圖4當接地焊盤如左圖所示分開時,從一個域傳輸到另一個域的信號可能會變得非常嘈雜。分析步驟以紫色圓圈標記。另一方面,如右圖所示,合并域后,信號將安全傳輸。但是,如果靜音塊的PSRR較差,則可能會受到影響。

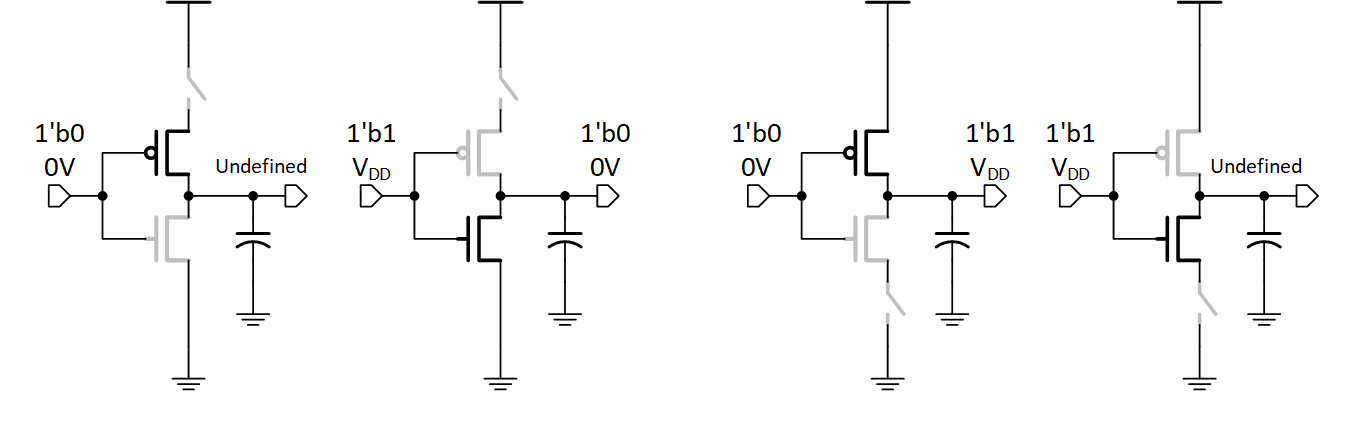

在具有功耗意識的數字設計中,浮動輸出不僅與斷開接地路徑相關,而且還與斷開電源路徑相關聯(圖5)。物理設計偏好通常傾向于切換接地路徑。這是因為在相同的導通電阻下,將使用面積小于PMOS器件的NMOS器件。

圖5當電源或接地關閉時,不可避免的情況會導致輸出電壓不確定。不確定的輸出電壓取決于存儲在負載電容器上的最后一個工作輸出狀態,電源與地的截止電阻之間的比率以及不同結的泄漏電流。

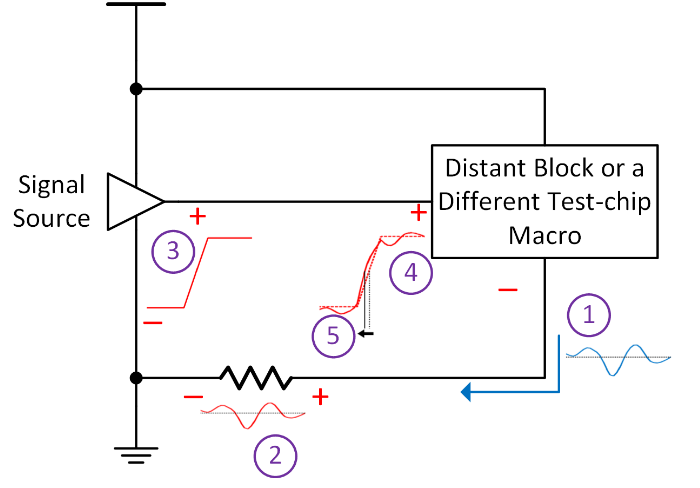

接地軌和電源軌似乎與時序收斂無關。定時關閉與不同的信元延遲和不同的信號沿有關。當接地軌具有相對較高的阻抗時,在電源軌和接地軌之間會產生相當大的IR降,這會降低有效電源電壓,從而增加CMOS單元的延遲。此外,即使電源線上的平均IR降微不足道,開關噪聲電流也會在接地電源線上產生明顯的瞬態噪聲電壓。因此,如圖6所示,到達距信號源較遠的門的信號沿可以有效地“移動”時間[1]。時移取決于瞬態噪聲的大小和極性。對于高上升/下降時間信號,這種影響變得更加明顯。

圖6按照紫色圓圈中的索引分析步驟,瞬態電源/接地電流曲線在接地點會產生相似的電壓曲線,這會影響信號沿的有效到達時間。大量增加本地去耦電容器以吸收交流電流曲線并降低電源/接地軌的阻抗可以緩解該問題。

分開還是不分開?

這是一個棘手的問題。需要詳細說明的一個重要項目是接地墊的分離。上一節可能給人的印象是,接地焊盤分離是一種不良的設計實踐,盡管在許多芯片中這可能是常見的實踐。通常,設計具有低電阻和低電感的單個統一接地連接要好于設計多個接地軌,而這些接地軌具有相互影響的相互作用域之間復雜的返回電流路徑以及載有高頻電流的大面積環路的磁耦合的麻煩。

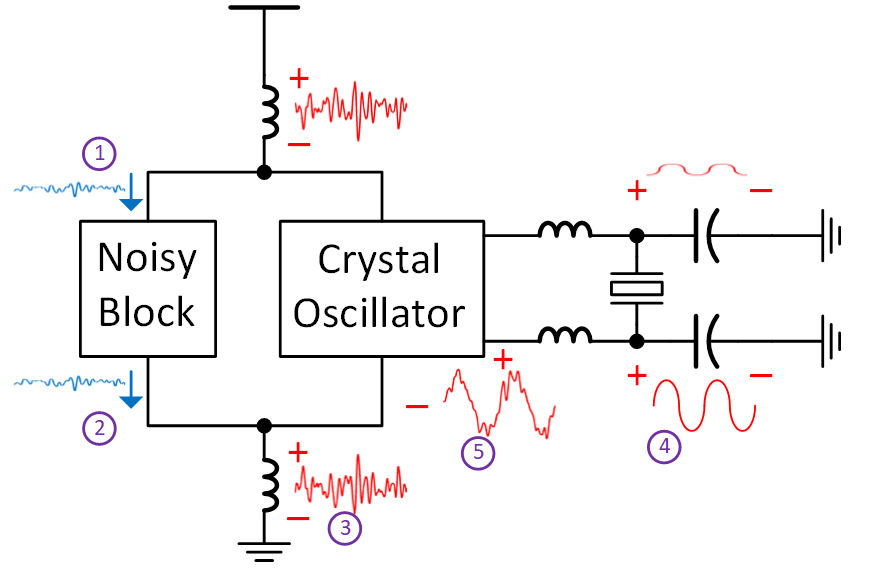

但是,在特殊情況下,您不能避免接地墊分離。例如,假設您有一個晶體振蕩器和一個嘈雜的數字模塊,它們都共享一個接地焊盤,如圖7所示。數字模塊從電源汲取噪聲電流,該噪聲電流通過接地軌和接合線返回。因此,接地鍵合線上存在明顯的電壓毛刺。由于該鍵合線與晶體振蕩器的接地點共用,因此噪聲電壓毛刺將有效地添加到晶體振蕩器內部節點處的晶體純正弦電壓。

圖7按照紫色圓圈中的索引進行的分析步驟,帶噪塊會間接在接地線兩端生成噪聲電壓。由于晶體實際上是一個非常尖銳的帶通濾波器,因此在振蕩期間,其每個端子上都存在純正弦電壓。但是,晶體振蕩器的內部節點會感測到接地線兩端的純電壓和噪聲電壓的疊加。

在需要分離的情況下,請執行以下操作:

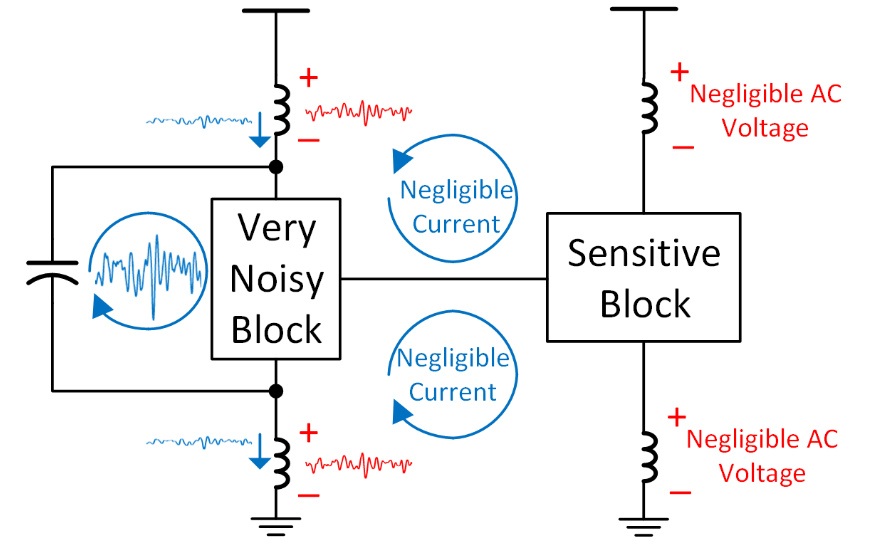

盡可能在噪聲塊周圍放置多個去耦電容器(圖8)。這減少了有噪聲的電源電流在硅外部的傳遞,從而最小化了在塊狀導軌及其輸出上產生的噪聲電壓。

最小化噪聲塊與其他塊之間的電氣交互作用,或僅使傳遞的電流最小化。為此,請在噪聲域中使用具有較高輸出阻抗的驅動器,而在安靜域中使用具有高輸入阻抗緩沖器的驅動器。

圖8噪聲塊處的去耦電容器吸收了流經電源和地的大部分AC電流曲線。從噪聲域到敏感域的傳輸電流最小化,可確保噪聲的傳輸最小化。

接地節點僅僅是定義的節點,僅有助于電路分析。所有電流均以環路傳播,并且不會在接地節點處停止。

要預見并解決與地面相關的問題,只需簡單地描繪出具有所有物理連接的完整電路,而無需定義接地節點。可視化不同的電流回路和公共路徑。

在做出統一或分離不同區域的接地墊的設計決定之前,請仔細研究預期的增益和潛在影響。

這是一個練習。圖9的左側顯示了一個具有有限漏極阻抗的簡單NMOS電流源。電源電壓源看到的低頻交流阻抗是多少?

圖9接地節點的定義是否會影響輸入阻抗值?

答案很簡單。現在,讓我們在電路上保持物理上相同,但是選擇NMOS漏極作為接地節點,而不是NMOS源極,如圖9的右側所示。阻抗會保持不變嗎?永遠不要讓地面躲避您。

參考

Maxim Integrated Application Note#4345,“接地良好,數字為模擬”

Mohammed Tawfik AbdelHafez是Si-Vision技術團隊的高級首席工程師。

編輯:hfy

-

節點電壓

+關注

關注

1文章

20瀏覽量

1902

發布評論請先 登錄

相關推薦

電路分析技術之節點電壓分析

電路分析技術之節點電壓分析

評論