首先看一個真實的故事:H公司的某網絡產品,PCB一直在A板廠生產,產品測試一直沒有什么問題。量產的時候,由于供應鏈需要雙供應商備份,就嘗試找了B板廠進行生產。結果產品測試的時候,發現B板廠的有部分板子調試不正常。

A板廠的板子一直沒有問題,產品的其他條件也都沒有變化,B板廠的板子有部分調試不通。這個證據簡直是太充分了,B板廠百口莫辯,賠償損失,并被打入冷宮……

直到有一天,A板廠的某批次板子也出現了部分調試有問題。H公司的研發人員才重視起來,進行了認真的排查。最后發現一個最有可能的原因:

A板廠對這個產品的阻抗管控,在進行補償的時候,一直以來都是負補償,也就是說最終的阻抗偏向于負公差,阻抗值偏低。而最近這一批次,阻抗管控的時候偏向了正公差,阻抗值偏高。A板廠想著反正都是在10%的誤差范圍以內,都是符合要求的。再對產品的信號質量進行嚴格測試發現,產品的裕量本身就非常小。就像下圖的男子,稍有偏差,可能就要掉進水里。

我們設計的目標,是要提高產品的裕量,從而保證產品的可靠性。就像在康莊大道上開車,安全可靠。

看一個阻抗偏差的例子:

DDR4地址信號

最差顆粒結果

這個案例的整體裕量很大,10mV的眼高差異,不到40ps的眼寬差異,相對裕量來說都是很小的偏差。但是想想第一張圖片的那個“一葦渡江”,如果項目本身裕量不足,或許小小的偏差就掉進河里了。設計要保證足夠的強壯性,才能抵御生產所必須的偏差。

凡是生產、必有偏差

我們經常會聽到產品公司的設計人員對生產提出很多要求,比如以下都是本人親歷的問題:

1、 我的板子,能不能按阻抗偏差+-5%來進行管控?(我聽到過最嚴格的要求是+-2.5%)

2、 線寬的蝕刻公差,能做到1mil嗎?不是正負哦,是總共的偏差1mil

3、 總板厚的偏差,能不能做到+0,-2.5%?

4、 ……

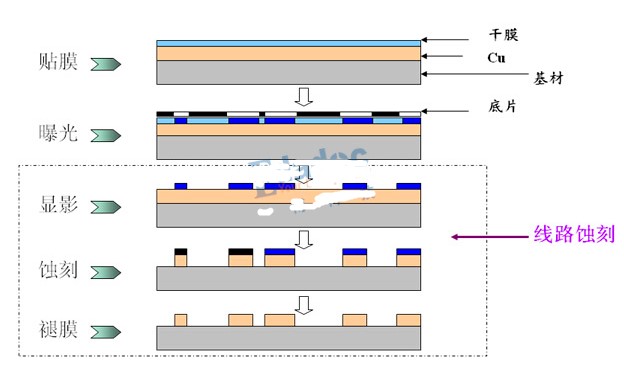

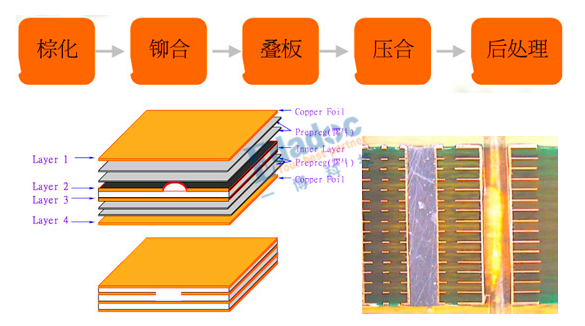

每次我都要不厭其煩的解釋,板廠制板,是物理和化學的過程,制板工藝這幾十年來并沒有本質的變化,還是蝕刻,壓合,鉆孔,電鍍……這些機械的過程都會有偏差。還記得我們去年的話題嗎?為什么常規阻抗控制只能是10%的偏差?這是有很多其他偏差累積在一起的結果:

1、 板材來料本身的偏差

2、 PCB加工過程的蝕刻偏差

3、 PCB加工過程層壓帶來的流膠率等偏差

4、 高速的時候,銅箔的表面粗造度,PP的玻纖效應,介質的DF頻變效應等

大家應該也還記得那張著名的偏差正態分布圖:

按照10%來進行阻抗偏差的管控,最符合正態分布的智慧,在成本和性能之間取得最佳的平衡點。

當然高速先生的觀點是:

1、當設計裕量足夠的時候,我們要盡可能考慮滿足生產的要求,這個就叫DFM。

2、設計遇到瓶頸的時候,生產就要來幫忙,盡可能攻克難關,這叫制造升級

3、當設計和生產都遇到天花板的時候,這就是產業升級的驅動力了

比如數字信號相對比較低速的時候,我們設計要給生產留出充足的空間,可以走很寬的線,很大的間距。隨著高速設計的到來,我們開始管控阻抗。由于板厚,層數的限制,阻抗線有時候需要走得很細,驅動板廠提升工藝。隨著串行總線的速率提升,損耗成為管控的對象,板廠也開始引進DeltaL等技術來評估損耗,對阻抗的管控要求開始來到7%,未來或許會到5%。隨著速率突破25G28G,來到56G的時候,生產的小偏差,都會帶來性能的大變化,于是整個產業都來到升級換代的邊緣。

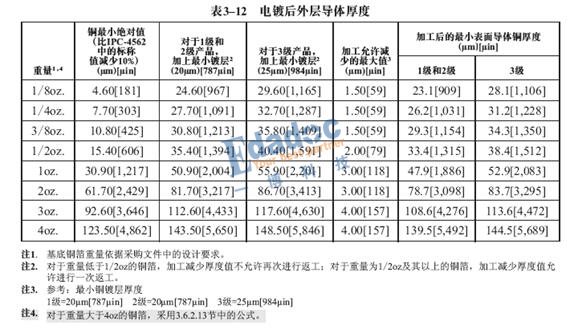

下面是我拋磚引玉,放上一些生產加工偏差規范:

編輯:hfy

-

阻抗

+關注

關注

17文章

941瀏覽量

45834 -

數字信號

+關注

關注

2文章

958瀏覽量

47519 -

DDR4

+關注

關注

12文章

320瀏覽量

40699

發布評論請先 登錄

相關推薦

為什么常規阻抗控制只能是10%的偏差?

為什么常規阻抗控制只能是10%的偏差?

評論