每年拿到DesignCon的文章后,弱水三千,我們不會只取一瓢,習(xí)慣上就會過一遍每一篇slides(為什么先是看PPT?也沒什么,主要因為快……)

但好像你去商場買東西一樣,會發(fā)現(xiàn)琳瑯滿目的商品,不一定每一款都適合你。同樣文章也是各個小領(lǐng)域都有涉及,我們主要還是關(guān)注和我們相關(guān)的。之前我們bruce也發(fā)過觀后感啦,在我們熟悉的PCB的大領(lǐng)域里有高速方面的56/112G的發(fā)展,有PCIE的,有DDR方面的,有對銅箔粗糙度,材料方面的研究。

除此之后,作為高速先生的我,很驚訝的發(fā)現(xiàn)了居然還有不少關(guān)于仿真的文章。實際上在短暫的驚訝之后,又感覺一切也是順其自然,我們以前老是說仿真的意義是在于你不能憑經(jīng)驗和理論去預(yù)測信號的趨勢和走向的時候需要去做的。

我們也在很多場合里說過,很多信號其實是不需要進(jìn)行仿真的,因為我們可以預(yù)測到它最終的設(shè)計是能夠滿足要求。然而去到了25G,56G以上這個范疇后,我們也很難去拍腦袋就說這對走線一定OK。細(xì)微的設(shè)計忽視和加工誤差都會是成功與失敗的臨界點,因此仿真技術(shù)的發(fā)展就變得不那么意外了。本期我先和大家分享一篇仿真的文章,個人認(rèn)為是比較經(jīng)典和實用的。本人也盡量為大家把這篇有點燒腦的文章解讀得通俗易懂一點哈!

這篇文章的名字就如下圖所示啦!應(yīng)該可以翻譯為一步步(手把手)教你學(xué)會如何進(jìn)行仿真測試校準(zhǔn),提高我們的仿真精度。

其實它的下面還有一個小標(biāo)題,可能更能說明這篇文章要講的是什么。

主要研究如何進(jìn)行25G-NRZ/56G-PAM4高速鏈路的仿真測試的校準(zhǔn)擬合。

首先看看它要進(jìn)行仿真測試的東東是什么?如下所示:

鏈路包括了從主芯片的pin到PCB走線到連接器的footprint再接上連接器,然后再經(jīng)過cable在遠(yuǎn)端的SMA頭,劃分開來就是如下圖所示的幾部分:對于傳輸線和BGA,連接器結(jié)構(gòu),其實我們需要用不同精度的仿真工具和建模方法去執(zhí)行,如下圖。

其中連接器的模型和cable的參數(shù)都是通過廠商拿到,我們主要做的部分是前面的BGA,走線和連接器footprint的仿真。

大家覺得難度如何,頻域校準(zhǔn)時域校準(zhǔn)哪個比較難?頻域的插損,回?fù)p,模態(tài)轉(zhuǎn)換呢?

首先本文也有做一些仿真前各項校準(zhǔn)難度預(yù)期,如下圖,看看和大家想的是不是一樣哈。

的確,頻域和時域各有不同的難度系數(shù),頻域的插損和時域的TDT總體來說容易點,頻域的回?fù)p和時域的TDR(也就是阻抗)稍難,最難的是頻域和時域模態(tài)?get到了嗎??沒get到也沒關(guān)系,下面會詳細(xì)解釋為什么難度不一樣。

我們先說結(jié)構(gòu)相對簡單的傳輸線,加工因素方面會把PCB走線變成梯形的樣子,我們稱為蝕刻因子,這個對于我們?nèi)ソS幸欢ǖ碾y度,不太容易得到等效的線寬。同時加工還存在流膠的影響,介質(zhì)厚度會和設(shè)計值不同,我們?nèi)绾稳サ刃В?/p>

至于傳輸線的建模仿真,我們是用單極點模型(容易建模,但高頻精度差)還是多極點模型(建模復(fù)雜)?對銅箔粗糙度我們是使用huray模型還是hammerstad模型也是很困擾的事情。

那回?fù)p方面呢?為什么會比插損難校準(zhǔn)呢,主要就是因為BGA和連接器的過孔,我們知道加工有鉆孔公差和背鉆的stub公差,8mil的孔加工完不會就是8mil,你設(shè)計時是想讓過孔沒有stub,但是加工出來會有2-12mil。另外走線的蝕刻因子也不好估計。

加上前面說的傳輸線的蝕刻因子和介質(zhì)厚度的流膠,可能你的測試結(jié)果會像下面這樣。

這樣的情況,你的仿真又應(yīng)該怎樣去校準(zhǔn)呢?

另外下面這一點,我們很少去關(guān)注,那就是器件輸出的工藝溫度的不同也會影響阻抗。

所以,可能不同批次生產(chǎn)出來的這條鏈路,它們的TDR測試可能會是下面的曲線:

另外模態(tài)轉(zhuǎn)換的校準(zhǔn)為什么最難,看下圖框框你就會明白,走線的拐彎,繞線補償,地過孔的對稱都不容易百分百去模擬,因此很難把共模和差模轉(zhuǎn)換校準(zhǔn)好。

所以很明顯我們要解決的問題是下面這樣:

那我們要做些什么去實現(xiàn)這一切呢?

我們可能需要去調(diào)節(jié)我們粗糙度的模型參數(shù):

也可能需要根據(jù)PCB廠家反饋或者切片去得到實際的疊層來確保加工后的傳輸線的阻抗:

也可能需要根據(jù)實際的測試方法去修正我們建模端口的添加方法:

甚至我們還需要判斷下廠家提供的連接器和cable的模型是不是就真的和測試情況一樣:

然后完成上面的一切之后,你會發(fā)現(xiàn)你的校準(zhǔn)精度可以做到非常高:

好,大概把這篇文章的精華分享完了,可能有部分人還沒想明白,到底做這么一個仿真測試校準(zhǔn)意義在哪呢?我們都喜歡舉一反三,實際上每款設(shè)計,高速鏈路都不會是一樣的,而且速率越高,設(shè)計對信號影響越大。如果我們先把這個“一”做出來了,以后大家想去搞自己產(chǎn)品的“三”就會很容易,同時我們這個“一”是得到測試的驗證,精度是非常高的,那么對于你們在前期如何規(guī)劃自己的“三”也會有極大的信心。

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396424 -

連接器

+關(guān)注

關(guān)注

98文章

14345瀏覽量

136202 -

走線

+關(guān)注

關(guān)注

3文章

113瀏覽量

23864 -

仿真測試

+關(guān)注

關(guān)注

0文章

75瀏覽量

11289

發(fā)布評論請先 登錄

相關(guān)推薦

AMD Versal自適應(yīng)SoC GTM如何用XSIM仿真和觀察PAM4信號

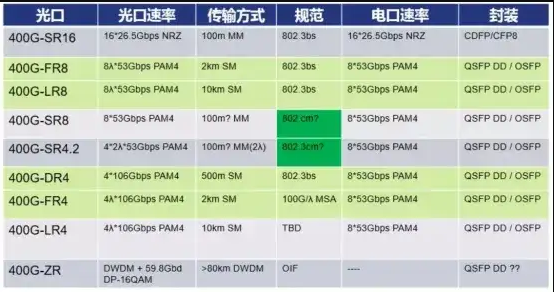

400G光模塊有哪些分類

400G QSFP-DD ER4 光模塊概述

明明我說的是25G信號,你卻讓我看12.5G的損耗?

設(shè)計仿真 基于VTD的AR-HUD仿真測試解決方案

了解高速56G PAM-4串行鏈路的時鐘需求

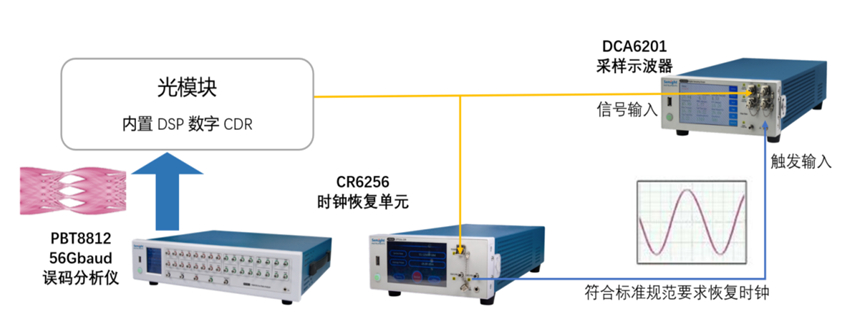

56Gbaud CR6256!400G/800G單多模光模塊及接口的時鐘提取

古希臘掌管224G 的神 | Samtec 224G PAM4 高速互連大合集!

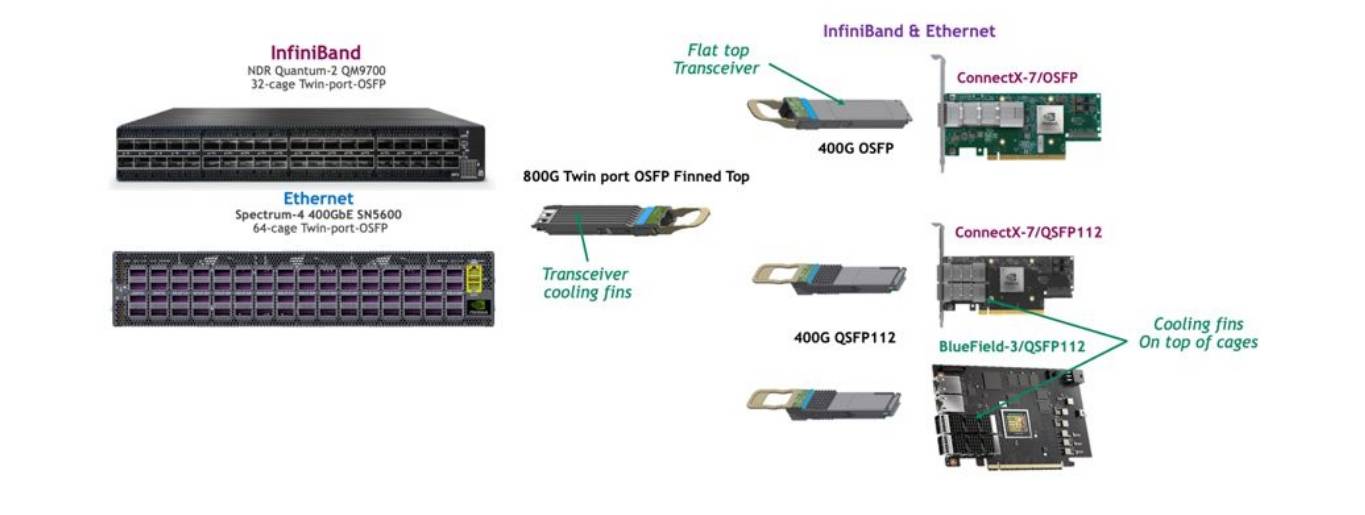

英偉達(dá)400G 100G-PAM4 OSFP和QSFP112光模塊在交換機上的驗證與優(yōu)化

SG3225EEN在PAM4光模塊和400G,QSFP-DD光模塊中的應(yīng)用

AMD硅芯片設(shè)計中112G PAM4串?dāng)_優(yōu)化分析

淺談下一代數(shù)據(jù)中心中的224G PAM-4架構(gòu)

三星將展示16Gb GDDR7技術(shù),重點關(guān)注PAM3優(yōu)化TRX均衡和ZQ校準(zhǔn)

如何克服PAM4調(diào)制的仿真挑戰(zhàn)呢?

25G-NRZ/56G-PAM4高速鏈路的仿真測試的校準(zhǔn)擬合方案

25G-NRZ/56G-PAM4高速鏈路的仿真測試的校準(zhǔn)擬合方案

評論