我們知道濾波電容被放在電源和地之間,主要有兩個(gè)作用:(1)為處于快速開關(guān)狀態(tài)下的IC供電;(2)減小電源和地之間的噪聲 。所有濾波電容選擇的策略都會(huì)采用梯次電容值配置,大電容有足量電量儲(chǔ)備,而小電容自身電感較小,可以滿足IC的快速充放電要求。

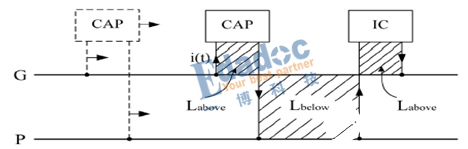

在我們常規(guī)設(shè)計(jì)中對濾波電容fanout時(shí),要從pin拉出一小段粗引出線,然后通過過孔和電源平面連接,接地端也是同樣。fanout過孔的基本原則就是讓這一環(huán)路面積最小,進(jìn)而使總的寄生電感最小。濾波電容的常見fanout方式如下圖所示,濾波電容靠近電源pin放置。

濾波電容的作用為電源網(wǎng)絡(luò)提供低阻抗的通路,從而抑制噪聲。如下圖所示(Lbelow主要是兩個(gè)過孔的自感和互感,當(dāng)電容的位置離IC器件更近時(shí),如下圖虛線所示,Lbelow的互感增大,因互感的作用與自感的作用相反,導(dǎo)致其整體電感減小,充放電速度更快; Labove包括電容的ESL和安裝電感)

由于濾波電容的寄生電感使得電容在高頻的阻抗增大從而噪聲抑制能力減弱甚至失去效果。一般的表貼封裝退耦電容的去耦范圍通常在100MHZ以內(nèi)。

某日我們的市場人員聯(lián)絡(luò)我,有一個(gè)新客戶的消費(fèi)類HDI項(xiàng)目有點(diǎn)問題,希望我們做一下Debug。根據(jù)客戶反饋,他們的SOC相關(guān)模塊原理圖和布局布線全部安照demo板設(shè)計(jì),但是產(chǎn)品測試時(shí)很多功能不滿足要求。而demo板都是ok的;他們找芯片原廠的FAE幫忙檢查原理圖也沒有發(fā)現(xiàn)問題,只是他們用10層3階HDI設(shè)計(jì),demo板用任意階HDI設(shè)計(jì)。FAE要求他們完全參考demo板或者修改的部分需要仿真。客戶感覺由于他們公司不是很有名氣芯片原廠的FAE對他們不積極,同時(shí)他們的PCB是由“比較專業(yè)且資深”的PCB工程師設(shè)計(jì),他們在PCB檢查時(shí)并沒有發(fā)現(xiàn)異常,所以最后只好找我們來定位一下問題,看看是否能通過優(yōu)化設(shè)計(jì),滿足性能要求。

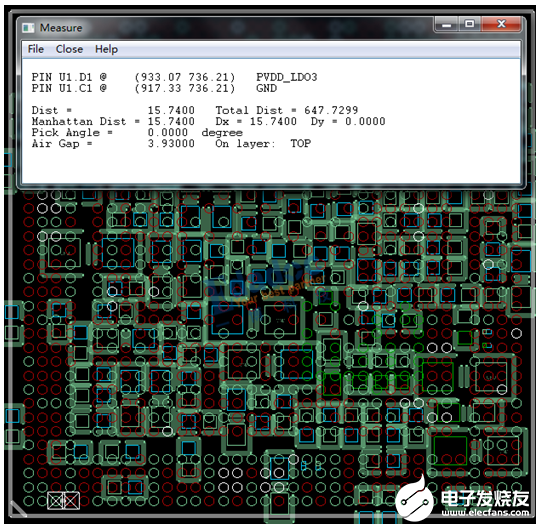

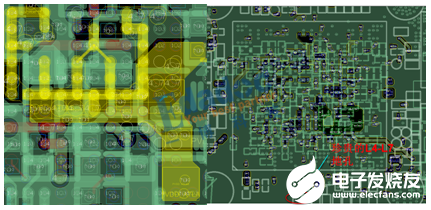

由于該SOC我們先前有相關(guān)設(shè)計(jì)經(jīng)驗(yàn),所以我打開PCB的時(shí)候還是有心理準(zhǔn)備的,密度肯定會(huì)比較大,當(dāng)然能對應(yīng)高階HDI設(shè)計(jì)的工程師,能力肯定也不錯(cuò)的。SOC部分布局如下所示(0.4BGA封裝從信號(hào)pin定義來看至少是三階HDI才能完成設(shè)計(jì))。

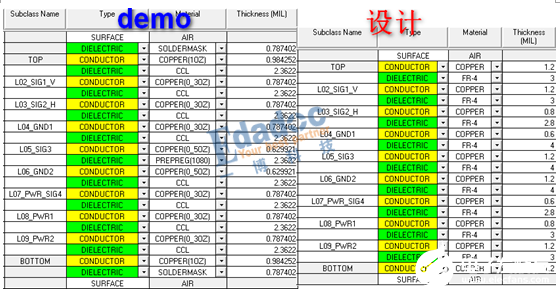

信號(hào)/電源通道和demo 基本一致,層疊厚度存在部分差異如下所示:(demo 板0.78MM,本設(shè)計(jì)1.05MM)

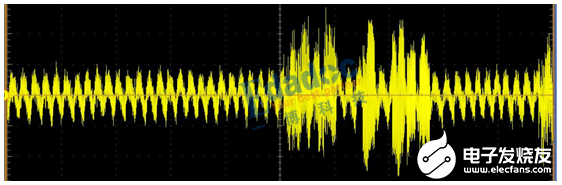

另外客戶反饋電源部分電容數(shù)量都是按照demo板推薦的,但他們測試時(shí)電源紋波比較大,其中VDD_1V測試波形如下圖所示。

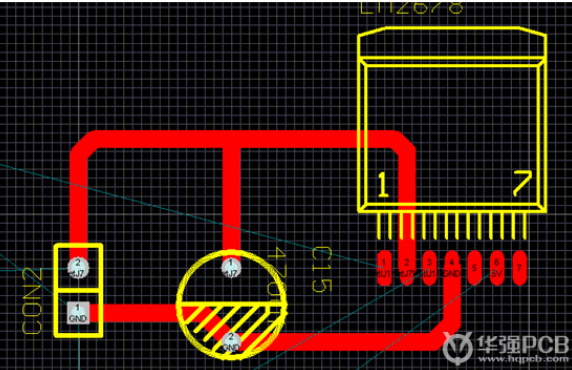

當(dāng)找到這一路電源時(shí),從電容位置和設(shè)計(jì)來看,感覺還是蠻好的。但仔細(xì)查看后發(fā)現(xiàn),由于HDI有多個(gè)層鋪為地平面(其中L4/L7為主地平面),當(dāng)看到SOC下方電源地的fanout時(shí),我和我的小伙伴們都驚呆了,不多說,有圖有真相!

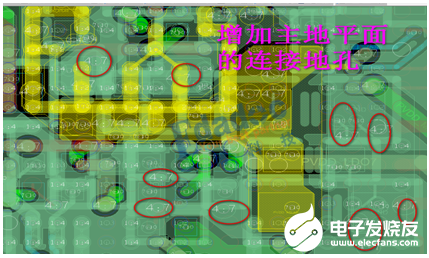

芯片在Top層,濾波電容在Bottom層;但L4/L7主地平面沒有就近的回流地孔,導(dǎo)致濾波電容的回路較遠(yuǎn),嚴(yán)重影響了濾波電容的性能!不信我們來仿真驗(yàn)證一下在客戶原始版本和增加部分地孔版本, PDN阻抗曲線差異!

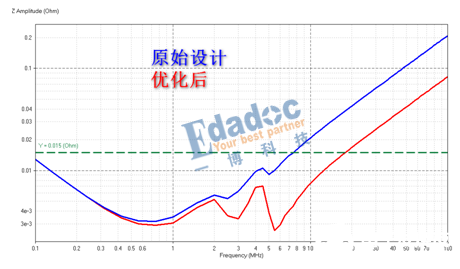

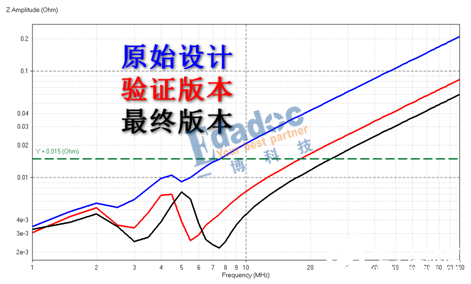

仿真驗(yàn)證PDN阻抗曲線如下所示:(在1MHz之后PDN差異就慢慢體現(xiàn)出來了)

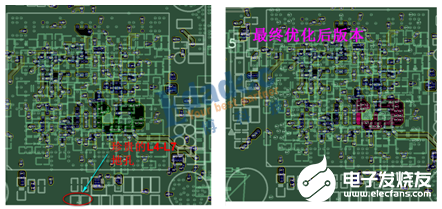

看到這里,就到了展現(xiàn)我們設(shè)計(jì)能力的時(shí)候(老司機(jī)們都知道,0.4BGA的高階HDI加孔的難度不亞于重新設(shè)計(jì))。然而我們是行動(dòng)派,有條件要上,沒有條件創(chuàng)造條件也要上!大家看看我們pcb修改前后對比,是不是棒棒地。

經(jīng)過我們修改優(yōu)化,客戶后期調(diào)試都通過了。當(dāng)然最重要的是我們PDN部分的優(yōu)化,還是用數(shù)據(jù)來說話!

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396287 -

濾波電容

+關(guān)注

關(guān)注

8文章

457瀏覽量

39988 -

soc

+關(guān)注

關(guān)注

38文章

4122瀏覽量

217938

發(fā)布評論請先 登錄

相關(guān)推薦

什么是HDI?PCB設(shè)計(jì)基礎(chǔ)與HDI PCB制造工藝

PCB設(shè)計(jì)之電容

介紹了濾波電容在PCB設(shè)計(jì)中正確接法

濾波電路的PCB設(shè)計(jì)注意事項(xiàng)

濾波電容在PCB設(shè)計(jì)中的正確接法

PCB設(shè)計(jì)中濾波電容布線的技巧和方法

PCB設(shè)計(jì)誤區(qū)-電源是不是必須從濾波電容進(jìn)入芯片管腳(終結(jié)篇)

電容的布局布線 - 電源是不是必須從濾波電容進(jìn)入芯片管腳(PCB設(shè)計(jì)十大誤區(qū)-1)

PCB設(shè)計(jì)誤區(qū)-電容的布局布線-電源是不是必須從濾波電容進(jìn)入芯片管腳(2)

PCB設(shè)計(jì)之HDI濾波電容的應(yīng)用

PCB設(shè)計(jì)之HDI濾波電容的應(yīng)用

評論