今天要給大家分享的文章如下,這次的題目很容易讀懂,就叫DDR4通道里,過(guò)孔的stub對(duì)信號(hào)質(zhì)量的影響分析。

那主要肯定是講過(guò)孔stub(殘樁)對(duì)DDR4的影響咯。首先呢作者對(duì)DDR4的信號(hào)質(zhì)量做了一些前提的判定和分析,例如要求通道的插損諧振頻率點(diǎn)要大于5倍的時(shí)鐘頻率,按本文分析的3200Mbps來(lái)說(shuō)的話(huà),時(shí)鐘是1.6GHz,因此要求的諧振頻率點(diǎn)必須大于8GHz。

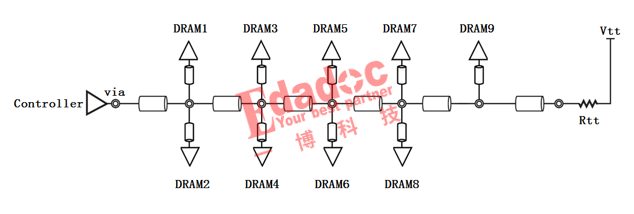

好,立馬進(jìn)入正題,看看作者是如何分情況對(duì)DDR4通道進(jìn)行分析的。他們主要對(duì)3種不同的場(chǎng)景進(jìn)行分析,一是顆粒版本的表層走線(xiàn),那肯定就是沒(méi)有過(guò)孔stub了;二是顆粒版本的內(nèi)層走線(xiàn),有過(guò)孔stub的情況;三是Dimm版本的內(nèi)層走線(xiàn),不僅有過(guò)孔stub,還包括了Dimm條連接器這個(gè)阻抗不匹配的點(diǎn)。下圖就是三種不同case的示意圖。

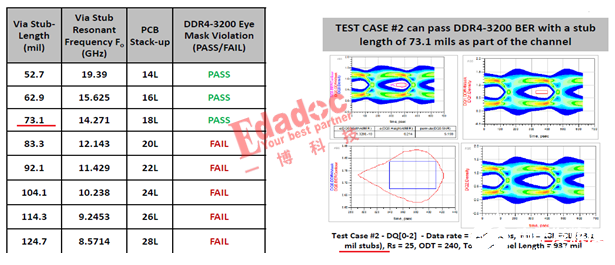

既然是詳細(xì)的研究過(guò)孔stub對(duì)信號(hào)質(zhì)量的影響程度,那肯定是需要不同的過(guò)孔stub長(zhǎng)度的比較了。于是本文做了非常非常多的疊層進(jìn)行分析,過(guò)孔stub從14層的52.7mil(內(nèi)層走線(xiàn)都以L(fǎng)3層出線(xiàn),分析不同疊層的最長(zhǎng)過(guò)孔stub的情況)到28層的124.7mil。幾乎涵蓋了99%的應(yīng)用需求。

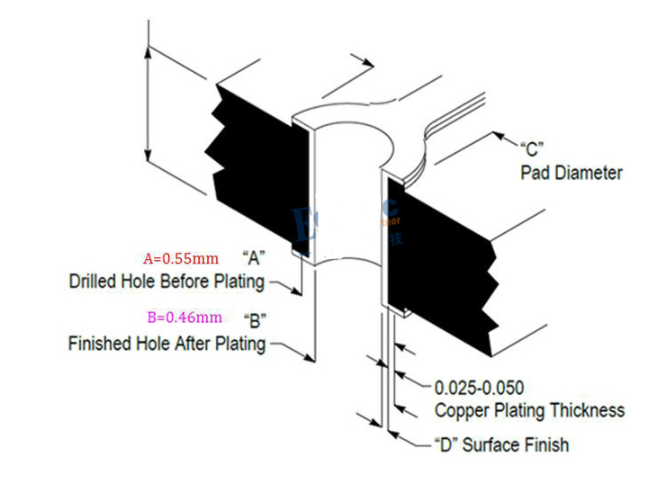

另外,作者還給出了所使用的過(guò)孔的一些參數(shù)情況和進(jìn)行3D仿真的模型。

好,我們一起來(lái)看分析的結(jié)果吧。

首先case1,表層走線(xiàn),沒(méi)有過(guò)孔stub的情況下,結(jié)果比較簡(jiǎn)單也比較明確,在3200Mbps的速率下信號(hào)質(zhì)量比較好,在-16次方的嚴(yán)格誤碼率下,眼圖仍有比較大的裕量。

那么進(jìn)行case2的分析了。可以看到,過(guò)孔stub長(zhǎng)度在73.1mil的時(shí)候是一個(gè)臨界點(diǎn),這個(gè)時(shí)候眼圖剛好壓在-16次方誤碼率的mask,再往下的話(huà)就不能滿(mǎn)足該誤碼率的標(biāo)準(zhǔn)了。

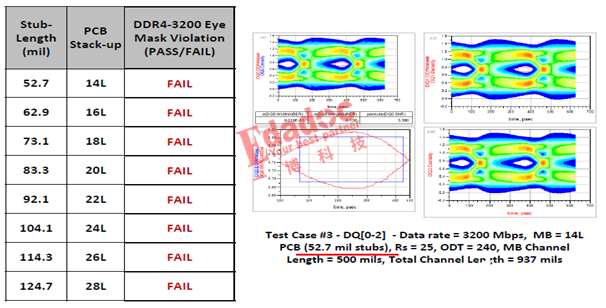

那么case3呢,加上一個(gè)dimm條連接器之后的情況又會(huì)是如何呢?恩!是的,想到了會(huì)變差,但是,是不是沒(méi)想到差成這樣??

可以看到在Dimm條應(yīng)用的情況下,50mil以上的stub都是有風(fēng)險(xiǎn)的,過(guò)不了-16次方誤碼率的標(biāo)準(zhǔn)。

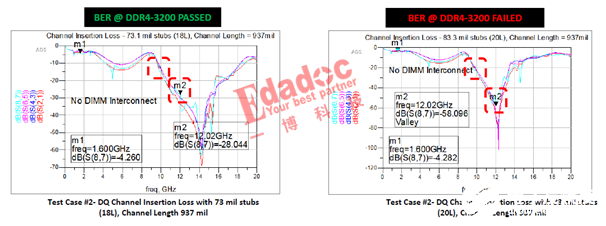

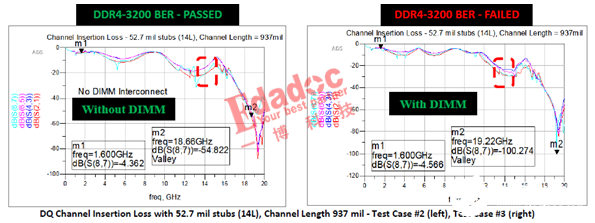

進(jìn)行完眼圖的分析后,我們?cè)賮?lái)看看頻域的分析,插損情況的對(duì)比。

首先進(jìn)行了case2的73mil臨界點(diǎn)和83mil不過(guò)的兩種情況的對(duì)比。可以看到雖然只是10mil的差別,但是從下圖紅色框標(biāo)出的幾個(gè)點(diǎn)的損耗情況都有比較大的差異,幾乎有30dB的區(qū)別。

而對(duì)比53mil的過(guò)孔stub長(zhǎng)度下顆粒版本和Dimm條應(yīng)用的情況如下。可以看到Dimm條模式下也會(huì)有接近10dB的差異了。

最后,作者給出了在不同過(guò)孔stub情況下的成功率的預(yù)測(cè),非常的直觀明了。

編輯:hfy

-

DDR4

+關(guān)注

關(guān)注

12文章

320瀏覽量

40699 -

信號(hào)質(zhì)量

+關(guān)注

關(guān)注

0文章

7瀏覽量

6790

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

連接器過(guò)孔stub到底對(duì)信號(hào)有什么樣的影響?

DDR4信號(hào)完整性測(cè)試要求

DDR設(shè)計(jì)需要背鉆嗎

過(guò)孔當(dāng)?shù)溃咚?b class='flag-5'>DDR4信號(hào)該何去何從?

DDR4復(fù)位偏差要求是什么?

佛山回收DDR4 高價(jià)回收DDR4

過(guò)孔STUB長(zhǎng),DDR信號(hào)“強(qiáng)”?

DDR4,什么是DDR4

Xilinx FPGA DDR4接口應(yīng)用分析

DDR4技術(shù)有什么特點(diǎn)?如何采用ANSYS進(jìn)行DDR4仿真?

DDR4設(shè)計(jì)過(guò)孔STUB長(zhǎng),DDR信號(hào)“強(qiáng)”?

DDR4協(xié)議

DDR4和DDR5規(guī)格之間的差異

淺談Via stub在DDR4并行鏈路上的表現(xiàn)

0706線(xiàn)下活動(dòng) I DDR4/DDR5內(nèi)存技術(shù)高速信號(hào)專(zhuān)題設(shè)計(jì)技術(shù)交流活動(dòng)

DDR4通道中過(guò)孔 stub對(duì)信號(hào)質(zhì)量的影響分析

DDR4通道中過(guò)孔 stub對(duì)信號(hào)質(zhì)量的影響分析

評(píng)論