與傳統低壓差(LDO)穩壓器相比,開關電源(SMPS)的高效優勢顯而易見。但也因其開關特性,開關電源在開關頻率和諧波處會產生噪聲。本文闡述了如何利用濾波器實現開關電源超低輸出電壓噪聲。應用低ESR陶瓷電容的單級電容濾波器廣泛用于輸出電壓紋波大于1-2mV的應用。對于像RF ADC和DAC這樣的應用,其紋波要求小于1mV,則需使用兩級 LC 濾波器來有效過濾開關噪聲。

單級濾波器設計

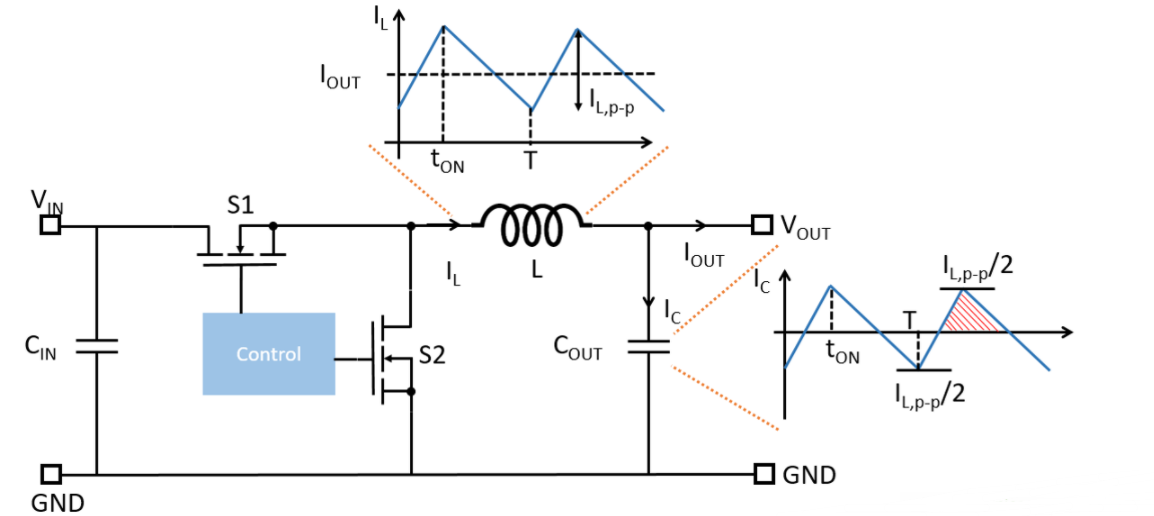

同步降壓變換器由輸入電容器CIN、兩個開關(S1和S2)及其體二極管、儲能電感(L)和輸出電容器(COUT)組成。當S1接通,S2斷開時,輸入源向功率電感(L)和負載提供電流,此時,電感電流上升。當S2接通而S1斷開時,電感器中存儲的能量被轉至輸出電容器和負載,導致電感器電流下降。降壓調節器的開關行為導致輸出電壓波動。此時,應在輸出端放置一個輸出電容器(Cout),以便在穩態時平滑輸出電壓。輸出電容器通過為高頻電壓分量提供低阻抗路徑,將高頻紋波反射回接地,從而降低輸出電壓紋波。

圖1:同步降壓調節器的連續導通模式(CCM)

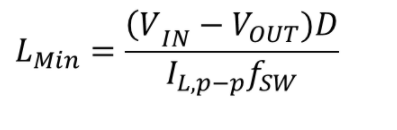

接著,假設Buck降壓變換器采用連續導通模式(CCM),以最大限度地降低輸出電壓紋波。L電感值也滿足電感器的電流紋波要求,其最小值可通過以下公式計算得出:

(1)

其中,VIN 和 VOUT 分別代表輸入和輸出電壓, 代表占空比,IL,p--p 代表電感的峰-峰電流紋波,fSW代表變換器的開關頻率。通常,峰-峰電感電流紋波可設置為輸出DC電流的20-40%。

輸出電容值應能確保其輸出紋波低于應用需要的峰-峰紋波值。對于單級電容濾波器,其最小輸出電壓紋波可達1~2 mV。

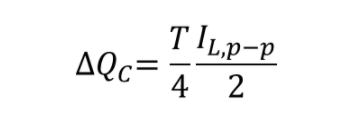

在穩態下的一個開關周期內,向電容器輸送的凈電荷為零。圖1陰影區的電容電荷可通過以下公式計算得出:

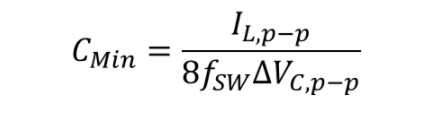

(2)

其中T為開關切換周期。根據定義,給定周期內的電容電荷也可表示為:

(3)

公式(2)代入公式(3),得到輸出峰-峰電壓紋波(VOUT,p--p)所需的最小電容為:

(4)

理想情況下,并聯更多的輸出電容可以降低對地的高頻阻抗,從而減小輸出紋波。而實際上,輸出電容器是橫放在印刷電路板上的,如果在印刷電路板上增加更多的輸出電容,會給并聯電路增加額外的寄生電感和交流電阻,增加輸出電容的效果會逐漸降低。

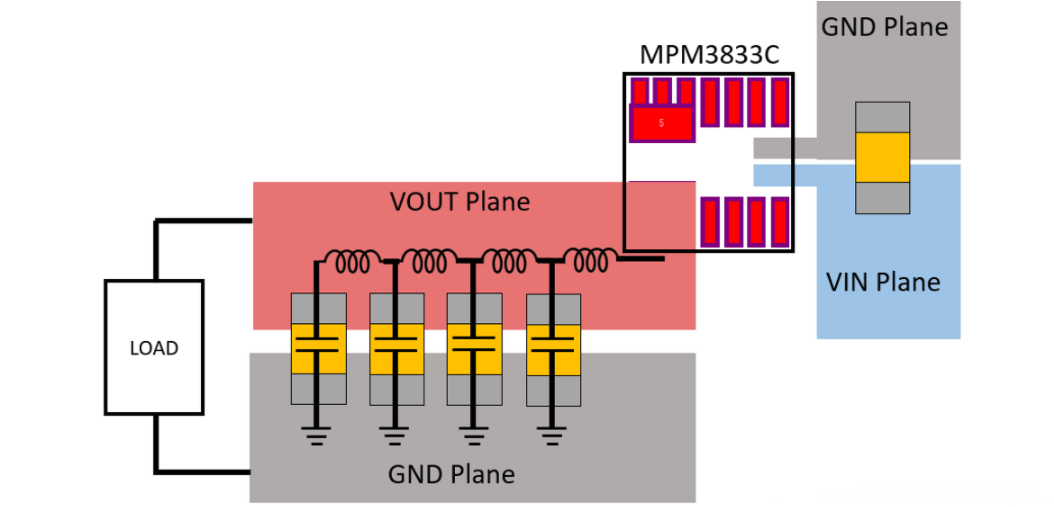

如圖2所示的典型PCB布局,MPS電源模塊通過集成電感,可大大簡化電源轉換器設計。在MPM3833C的PCB布局中,為輸出功率路徑進行了大面積鋪銅,這能最大限度地降低功率損耗。輸出電容器也是沿著輸出電流路徑放置的。如圖所示,隨著放置在輸出平面上的電容器越來越多,附加電容器與電源模塊輸出引腳之間的距離也變得越來越大。因此,在離電源模塊較遠的輸出電容中,會產生更多的寄生電感。增加輸出電容的效果變得越來越差,最終遠端電容的高頻對地回路以寄生電感為主。

圖2:MPM3833C電源模塊典型PCB布局

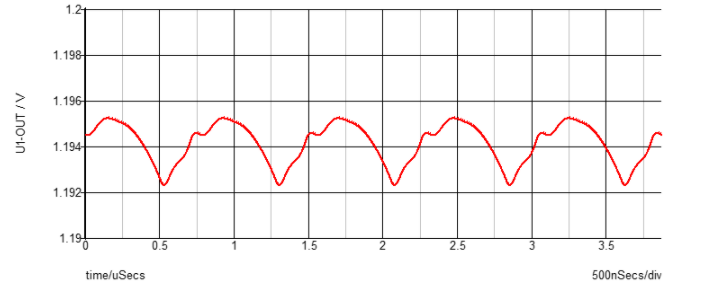

為演示回路寄生電感的影響,這里使用Simplis設計出了具有不同輸出電容的MPM3833C,并假設每個增加的輸出電容向回路引入0.5nH的寄生電感。圖3展示了帶有一個22μF電容器的電源模塊輸出紋波。可以看出,輸出電容器的確有效地降低了輸出紋波:在5V輸入,1.2V 輸出和2A 負載時,輸出紋波降至約為3mV。

圖3:帶一個22μF輸出電容的MPM3833C所產生的輸出紋波

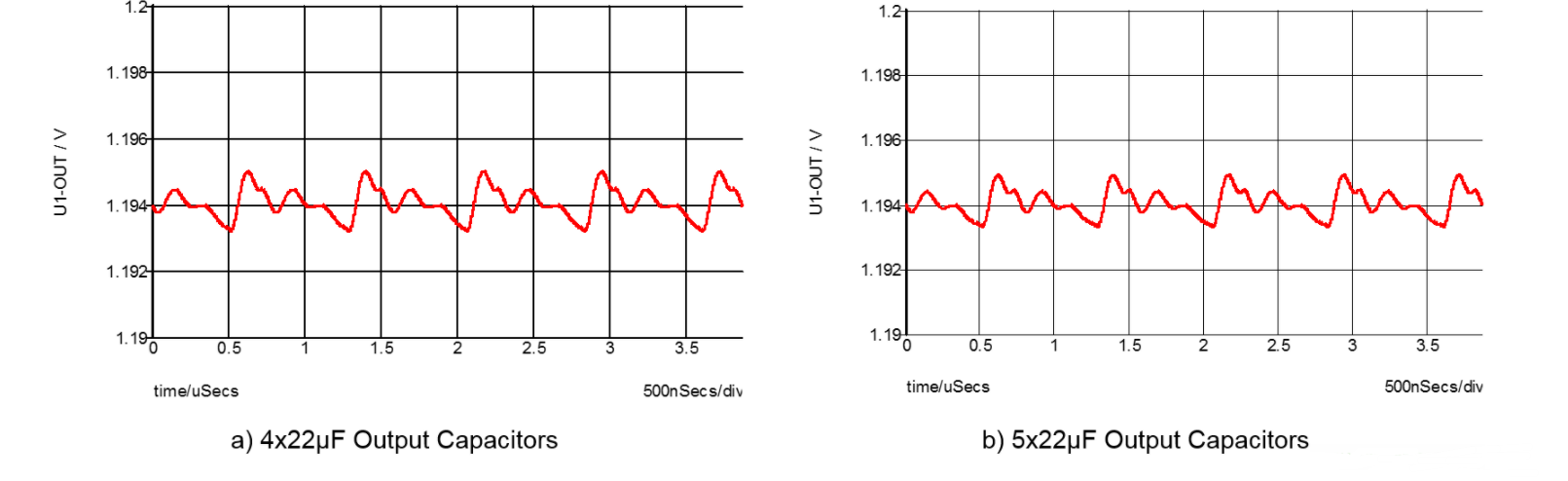

為了進一步降低輸出電壓紋波,可以在輸出端再增加一個22μF的輸出電容。由于新增的電容器必須放置在離電源模塊更遠的地方,因此新增電容器所引入的寄生電感為1nH。圖4a給出了仿真輸出電壓波形圖,其中輸出電壓紋波已降到2mV。與圖3所示的波形圖相比,增加一個22μF輸出電容器可將輸出電壓紋波有效降至3mV,而再增加一個 22μF電容器的效果其實并不明顯。圖4b顯示了多一個22μF電容器后(總共4x22μF)的輸出電壓紋波。最后一個22μF 電容器在其高頻對地回路中引入的寄生電感為1.5nH。如圖所示,與使用3x22μF的情況相比,多增加一個電容器后輸出紋波降低度小于5%。

圖4:MPM3833C 輸出電壓紋波對比圖

從圖3和圖4的演示可知,PCB上添加的電容器越多,PCB鋪銅/走線所產生的寄生電感就越多。最終,增加更多電容器的作用被回路中不斷增加的附加寄生電感所抵消。

第二級濾波器設計

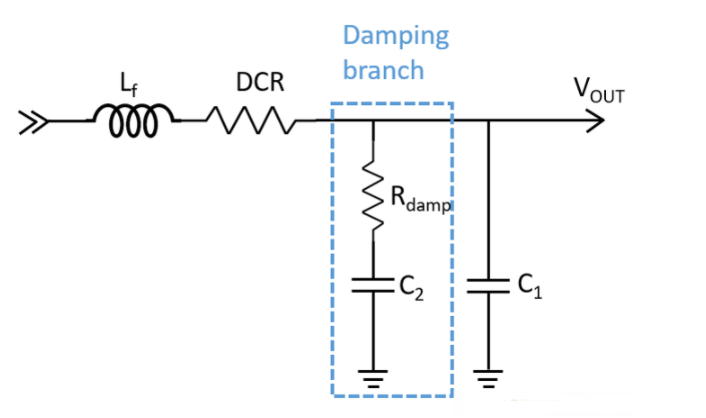

通常,并聯輸出電容器能將輸出電壓紋波有效降低到最低1-2mV。要實現低于1mV的紋波,需要一個第二級輸出濾波器。圖5展示了第二寄濾波器的典型電路。第二級濾波器由一個濾波電感及其串聯電阻(DCR)、一個對地電容器支路和一個阻尼支路組成。濾波電感(Lf)在設計的高頻范圍內具有電阻,以熱量的形式耗散噪聲能量。該電感器與附加的并聯電容器結合形成低通LC濾波器網絡。

圖5:帶并聯阻尼支路的兩級LC濾波器

合理設計的第二級濾波器會有效降低輸出電壓噪聲。針對工作頻率來選擇LC濾波器組件至關重要。設計的第一步是根據公式(4)選擇第一級輸出電容器。在第一極的設計中,典型的輸出電壓紋波一般為5mV至10mV。所以,通常選用10-22μF電容器就足夠了。為保證系統的穩定性,第一級的電容容量(COUT)必須小于第二級的旁路電容(C1)。

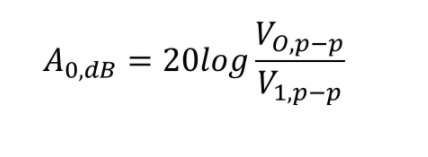

一旦確定了第一級電容器并給出了規定的輸出電壓紋波(在給定頻率下),第二級LC濾波器所需的衰減可確定為:

(5)

其中,V1,p--p 代表輸出電容器的峰-峰電壓紋波,Vo,p--p代表輸出電壓的峰-峰電壓(在第二級濾波器之后)。

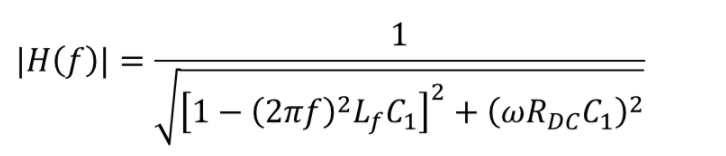

使用相量分析,LC濾波器增益的振幅可通過以下公式計算:

(6)

阻尼支路(由一個大型電阻和電容串聯組成)的阻抗在開關頻率下比對地支路大得多。因此,在下面的分析中,圖5所示的濾波器可等效于一個二階RLC濾波器。

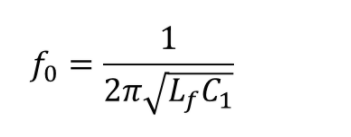

濾波器的截止頻率為:

(7)

通常,可以選擇電感值為0.22μH到1μH的電感器來實現所需的輸出紋波。此濾波電感的并聯阻抗會增加功耗并降低了輸出電壓的精度,因此應選擇DCR最小的電感。需要注意的是,隨著直流電流的增大,電感的磁芯材料會逐漸飽和,從而也會降低電感的電感值。應確保額定直流電流下的電感值足夠高。

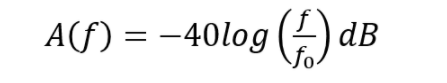

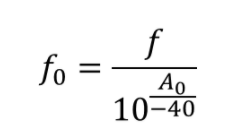

一旦選擇了濾波電感器,就可以從數據表中提取其DCR。第二級LC濾波器是一個二階濾波器,在截止頻率之后每十檔衰減40db。給定頻率下的衰減可根據以下公式估算出:

(8)

根據公式(5)計算出的衰減,可使用以下公式計算出所需的截止頻率:

(9)

然后,可計算出所需的對地支路的電容值(C1):

(10)

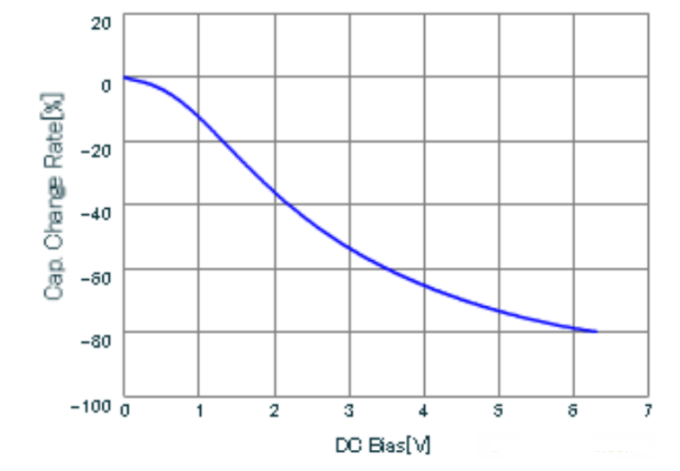

由于低ESR和ESL,應使用陶瓷電容器作為旁路電容器。需注意,在直流偏壓下,陶瓷電容器的電容會發生顯著降額。圖6給出了額定電壓為6.3V的Murata 0805陶瓷電容器的直流降額曲線。如圖所示,在滿額直流偏壓下,電容降到額定值的20%。旁路電容器應在額定直流偏壓下選擇,以便考慮降額值。

圖6:DC偏置下的典型陶瓷電容降額曲線

阻尼

如果第二級LC濾波器的阻尼不合適,可能會出現諧振。濾波電感與對地支路之間的諧振會放大輸出紋波,在負載瞬態時還會產生不希望出現的振鈴。圖7a顯示了帶第二級LC濾波器的欠阻尼變換器系統的輸出電壓。最初,系統在穩態下運行。當t=200μs時,負載瞬態從1A變成2A,輸出電壓引起振鈴。圖7b說明了過阻尼二級濾波器負載瞬態下的輸出電壓和電流。為避免在負載瞬態時產生振鈴,第二級LC濾波器諧振必須得到適當的抑制。在大多數設計中,第二級濾波器會被放置在控制回路之外,以避免控制回路不穩定。因此,阻尼必須使用無源元件(附加阻尼電阻)。

圖7:瞬態響應

濾波電感通常包含與電感串聯的寄生直流電阻。此DCR向網絡提供阻尼。然而,為了能向串聯RLC電路提供足夠的阻尼,串聯電阻必須滿足 。大部分情況下,DCR無法獨自提供足夠的阻尼。為此,需在旁路電容處并聯一個RC阻尼網路,與串聯DCR電阻一起阻尼諧振電路。

設計實例

EVREF0102A是專為賽靈思ZCU1275 Zynq UltraScale+RFSOC設計平臺所開發的模擬電源模塊。EVREF0102模擬電源模塊為ZCU1275開發套件上的高速數模變換器提供超低噪聲電源。

圖8:EVRF0102超低噪聲電源模塊

EVREF0102A采用了五個帶集成電感器的高效降壓開關電源模塊。MPM3833C是一款6V、3A、超小型降壓電源模塊,MPM3683-7是一款16V、8A電源模塊。兩款電源模塊都具有集成保護功能,包括OCP、OVP、UVP和OTP。與傳統的LDO解決方案相比,EVREF0102A的效率提高了80%。EVREF0102A模擬電源模塊通過采用強制連續導通工作模式(CCM)和后無源濾波器,實現了超低噪聲水平,可以滿足Xilinx對高速數模變換器規范。其中,兩個最敏感的ADC和DAC電源使用CLC無源濾波器,其他電源使用電容濾波器。

MPM3833C電源模塊用來為ADC_AVCC電壓軌供電,下面便以此為例說明其設計過程。MPM3833C集成了一個1μH的功率電感,通過公式(1)計算出電感在5V輸入和0.925V輸出時的電流紋波為0.63A。隨后,基于公式(4)選擇第一級輸出電容器為22μF,為第二級濾波器提供3mV的電壓紋波。

第二級LC濾波器的所需增益由公式(5)確定為-30dB,在開關頻率下可實現120μV的輸出電壓紋波。考慮到尺寸和額定電流,選擇具有足夠額定電流的0.24μH Murata芯片電感DFE201612E-R24。ADC和DAC電源要求超低噪聲頻率范圍高達15MHz。為了提供足夠的衰減裕度,第二級濾波器的截止頻率選擇為25kHz。最后,濾波電容器的選擇150μF。這種設計雖比較保守,但能提供足夠的裕度。。阻尼電容選用100mΩ ESR 的SP電容器。鑒于SP電容器的串聯電阻足夠高,因此無需添加外部電阻來增加阻尼。

EVREF0102A輸出噪聲測量的FFT結果如圖9所示。如圖所示,開關頻率處的峰值噪聲被降至14μV。

圖9:EVREF0102中ADC_AVCC電源的輸出噪聲測量

總結

本文概述了如何使用輸出濾波器實現降壓調節器超低輸出電壓噪聲的設計過程。一個單級輸出電容濾波器能夠將輸出電壓紋波降低至1-2mV。若需將輸出電壓紋波有效降低至1mV以下,可增加第二級LC濾波器。第二級LC濾波器的設計包括了濾波電感、旁路電容和阻尼支路的選擇。文中還給出了Xilinx ZCU 1275套件中高速數模轉換器電源的設計實例。優化后的濾波器有效地降低了輸出電壓紋波,滿足ADC/DAC電源的超低噪聲要求。

編輯:hfy

-

電容器

+關注

關注

64文章

6206瀏覽量

99331 -

濾波器

+關注

關注

160文章

7748瀏覽量

177721 -

電源模塊

+關注

關注

32文章

1687瀏覽量

92725 -

LDO穩壓器

+關注

關注

0文章

139瀏覽量

16694

發布評論請先 登錄

相關推薦

如何實現調節器的正反作用

濾波器時間常數對輸出信號的影響

SM 72485降壓開關調節器數據表

低功率低噪聲150 mA低輸出線性調節器TPS764系列數據表

電源模塊的電路原理 BOSHIDA 寬電壓輸入 整流器濾波器穩壓器

超低功率100 mA低輸出線性調節器TPS769xx系列數據表

超低功率50 mA低輸出線性調節器TPS770xx數據表

如何使用輸出濾波器實現降壓調節器超低輸出電壓噪聲

如何使用輸出濾波器實現降壓調節器超低輸出電壓噪聲

評論