你肯定會相信阻抗不匹配影響PCB性能;你會相信等長做得不好影響DDR的時序;你也會相信PCB太長的話高速信號會有問題;但是如果我們告訴你總有一天BGA芯片里面不能穿差分線的話,你會相信嗎?

所謂BGA,也就是學名為球柵陣列封裝的芯片,是芯片封裝界發展到今天為止算是集成度最高的封裝技術了哈。小則幾百pin,多則幾千pin都密密麻麻的按照一定的pitch間距進行排列,我們目前常用的pitch為1.2mm,1mm,0.8mm這些。

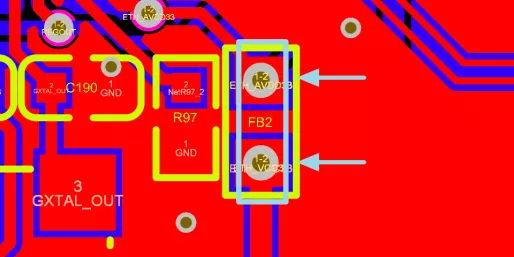

那么說到密集,大家肯定都有過這樣的經歷,也就是處于BGA里面的高速信號如果要走出BGA的話,一般會在pin的位置去做fanout,也就是所謂的BGA扇出,然后通過一個內層(當然底層也可以)從BGA里面層層進行突圍,直到走出BGA區域為止。有的時候,這對走線在走出來的過程中經過的地方可謂是非常的坎坷,坑坑洼洼的,例如下面這樣,做過高速信號PCB設計的粉絲們應該都很清楚為什么會這樣了哈。

我們知道,高速信號的過孔是要進行反焊盤處理的,那么這個時候我們就會發現,一對從BGA里面走出來的線可能需要經過若干個過孔反焊盤的邊緣。為什么叫邊緣呢?因為過孔反焊盤理論上是挖的越大越好,這樣才能最大程度的提高過孔的阻抗,因此在走線經過的區域,基本上是走線上下的參考平面就會被反焊盤挖空掉,也就是在過孔的區域,走線是沒有多余的參考的。

如果要問大家這個時候是保證過孔的阻抗呢還是保留那么一小段走線的參考平面,我相信百分之80以上的人都說是保證過孔的阻抗,大家的意見都是也就幾十mil的走線少一點參考平面能有多大的影響,再說了,又不是完全沒參考平面,只是沒有多余的參考平面而已嘛。另外很重要的一點就是,這個是作為PCB設計界一個通用的處理方式,而且在大多數產品做出來之后都是沒有問題的。因此大家也就覺得是一個很穩妥的設計方法了。

但是高速先生總喜歡對一些看起來很正常的設計理念進行“挑戰”,這次我們就針對BGA穿線是不是真的沒有問題進行研究。我們做了一塊測試板,驗證下在1.0mm pitch BGA間距的情況下穿線的影響。如下所示:我們在1.0mm的BGA下穿過一對差分線,然后模擬經過若干個其他走線的過孔反焊盤區域的情況,我們來看看這對走線本身的性能如何。

經過我們對幾塊板的同一個待測物的測試結果對比發現,結論是驚人的一致!!!它的損耗不會是一條我們認為的平直的曲線,其中在25GHz之后有非常巨大的諧振點。

那個,我相信大多數粉絲們都能看懂上圖的插入損耗曲線,至少能分辨出好還是不好。

好,我們繼續往下講,從這個糟糕的S參數來看,我們大致可以判斷它的可用范圍在25GHz內,如果大家還是對頻域參數不是很熟悉的話,我們換成大家喜歡的時域來分析哈。從上面的損耗參數來看,走現在很成熟的10Gbps到25Gbps應該都是沒太大問題的,那我們就直接跳過10G到25G,從56Gbps起步來衡量。那放到我們現在也做得比較多的56G-PAM4的高速設計上,我們看看如果發送一個理想的56G-PAM4信號源經過這個BGA扇出之后會是怎么樣呢?

恩,看來這個BGA的扇出設計對于56G-PAM4還是OK的,那我們再來個更厲害的?目前業界已經開始對112G-PAM4進行研究了,那高速先生也嘗試下加入一個112G-PAM4的信號源進去,看看經過這個BGA扇出之后會是什么情況。結果如下所示:

從上面的眼圖可以看到,就只是經過了一個BGA扇出之后眼圖就“涼”了一半了,壓根都還沒開始走線,加上走線的話估計就……呃!

就像前面所說的,在112G來臨的時候,如果還是像上面一樣的BGA扇出的話,這對差分線的性能會大打折扣,甚至可能一個我們認為很簡單的扇出設計就消耗掉整個通道的裕量。BGA扇出雖然是個很簡單而且約定俗成的設計,但是在信號速率越來越高之后,信號的性能會受到越來越多因素的影響,比如BGA的pitch大小,過孔反焊盤設計,疊層設計,線寬線距選擇,加工誤差等,使得原本看起來一個很平常的設計都可能出現問題,這可能也變成我們SI未來要去思考的問題了。

編輯:hfy

-

PCB設計

+關注

關注

394文章

4671瀏覽量

85319 -

BGA芯片

+關注

關注

1文章

31瀏覽量

13622

發布評論請先 登錄

相關推薦

編譯差分線時出現錯誤怎么辦?

PCB設計那幾個阻抗沒法連續的地方怎么辦

高速串行:BGA里面不能走差分線?

PCB設計總有幾個阻抗沒法連續的地方,怎么辦?

PCB設計:BGA芯片里面不能穿差分線的怎么辦

PCB設計:BGA芯片里面不能穿差分線的怎么辦

評論