晶振為什么不能放置在PCB邊緣?現象描述:

某塑料外殼產品,帶一根I/O 電纜,在進行 EMC 標準規定的輻射發射測試時發現輻射超標,具體頻點是 160 MHz。需要分析其輻射超標的原因,并給出相應對策。

原因分析:

該產品只有一塊 PCB,其上有一個頻率為 16MHz 的晶振。由此可見,160MHz 的輻射應該與該晶振有關(注意:并不是說輻射超標是晶振直接輻射造成的,可能是倍頻產生的)。圖 1 所示的是該產品局部PCB 布局實圖,從圖 1 中可以明顯看到,16MHz 的晶振正好布置在PCB 的邊緣。

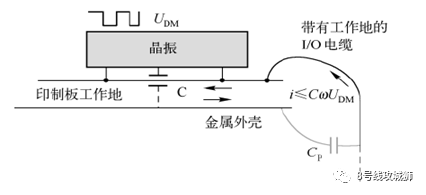

圖 1 該產品局部 PCB 布局實圖 當一個被測產品置于輻射發射的測試環境中時,被測產品中的高速信號線或高速器件與實驗室中參考接地板會形成一定的容性耦合(本產品中晶振屬于高速器件,其對應的上升下降沿較陡,晶振在工作時,其引線部分的 dU/dt 比較大,屬于強干擾源,在輻射發射測試中是隱患),即被測產品中的高速信號線或高速器件與實驗室中參考接地板之間存在電場分布或寄生電容,這個寄生電容很小(如小于0.1pF),但是還是會導致產品出現一種共模輻射,產生這種共模輻射的原理如圖 2 所示。在圖2 中,晶振殼體上的電壓(外殼不接大地的晶振)或晶振時鐘信號引腳上的電壓Udm 和參考接地板之間產生寄生回路,回路中的共模電流通過電纜產生共模輻射,共模輻射電流 Icm ≈C * w * Udm,其中,C 為 PCB 中信號印制線與參考接地板之間的寄生電容, 約在十分之一皮法到幾皮法之間;Cp 為參考接地板與電纜之間的寄生電容,約為 100 pF;w 為信號角頻率。共模輻射電流 Icm 會在幾微安到數十微安之間,經分析可知,電纜上流過這個數量級的共模電流已足夠造成輻射發射測試的超標。

圖 2 晶振與參考接地板之間的容性耦合導致輻射發射原理

為什么晶振布置在 PCB 邊緣時會導致輻射超標,而向板內移動后,可以使輻射發射測試通過呢?

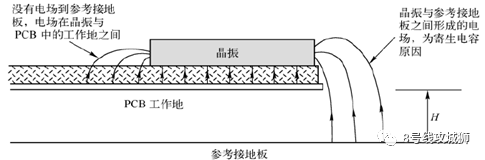

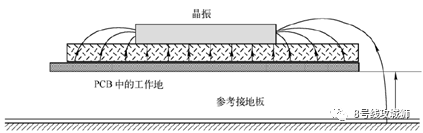

從以上分析已經可以看出,晶振與參考接地板之間的耦合導致電纜共模輻射的實質是晶振與參考接地板之間的寄生電容,也就是說這個寄生電容越大,晶振與參考接地板之間的耦合就越厲害,流過電纜的共模電流也越大,電纜產生的共模輻射發射也越大;反之輻射發射就越小。那這個寄生電容的實質是什么呢,實際上這個晶振與參考接地板之間的寄生電容就是由于晶振與參考接地板之間存在的電場分布,當兩者之間的電壓差恒定時,兩者之間電場分布越多,兩者之間的電場強度就越大,兩者之間寄生電容也會越大。當晶振布置在 PCB 的邊緣時,晶振與參考接地板之間的電場分布示意圖如圖 3 所示。當晶振布置在 PCB 中間,或離 PCB 邊緣較遠時,晶振與參考接地板之間的電場分布示意圖如圖4 所示。

圖 3 PCB 邊緣的晶振與參考接地板之間的電場分布示意圖

從圖 3 和圖 4 的比較可以看出,當晶振布置在 PCB 中間,或離PCB 邊緣較遠時,由于 PCB 中工作地(GND)平面的存在,使大部分的電場控制在晶振與工作地(GND)之間,即在 PCB 內部,分布到參考接地板的電場大大減小,即晶振與參考接地板之間的寄生電容大大減小。這時也不難理解為何晶振布置在PCB 邊緣時會導致輻射超標,而向板內移動后,輻射發射就降了。

圖 4 PCB 中間的晶振與參考接地板之間的電場分布示意圖

處理措施:

方案一:將晶振內移,使其離 PCB 地平面邊緣至少有1 cm 以上的距離,并在 PCB 表層離晶振 1 cm 的范圍內敷銅,同時把表層的銅通過過孔與 PCB 地平面相連。

方案二:不改電路板的情況下選擇放棄使用外部晶振,在軟件中屏蔽外部晶振,采用單片機內部晶振。

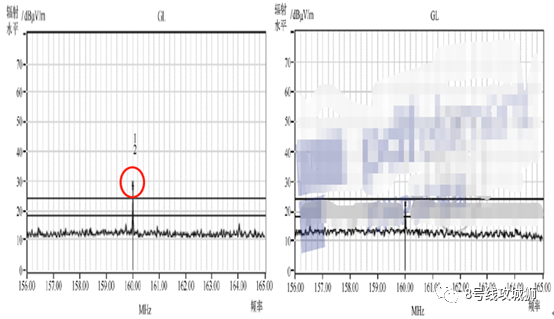

本次實驗采用方案一,經過修改后的測試結果有明顯的改善,如下圖 5 所示,左右分別是整改前與整改后的整改前后輻射發射測試頻譜圖,可以明顯看出整改后,輻射發射有明顯的改善。

圖 5 整改前后輻射發射測試頻譜圖

思考與啟示

(1) 高 dU/dt 的印制線或器件與參考接地板之間的容性耦合,會產生 EMI 問題,敏感印制線或器件布置在 PCB 邊緣會產生抗擾度問題;

(2) 杜絕高 dU/dt的印制線或器件放置在PCB 的邊緣,如果設計中由于其他原因一定要布置在 PCB 邊緣,那么可以在晶振印制線邊上再布一根工作地(GND)線,并注意一定要在包地線上間隔一段距離就打過孔,把晶振部分圍起來,如下圖6 示意;

圖 6 晶振包地示意圖

其理論依據同法拉第電籠:由于金屬的靜電等勢性,可以有效屏蔽外電場的電磁干擾。法拉第屏罩無論被加上多高的電壓內部也不存在電場。而且由于金屬的導電性,即使籠子通過很大的電流,內部的物體通過的電流也微乎其微。在面對電磁波時,可以有效的阻止電磁波的進入。 由于法拉第屏罩的靜電屏蔽原理,在汽車、飛機等交通工具中的人是不會被雷擊的。同樣,也是因為法拉第屏罩的原理,有金屬外皮的同軸電纜也可以不受干擾地傳播訊號。如果電梯內沒有中繼器的話,那么當電梯關上的時候,里面任何電子訊號也收不到。為防止干擾,一些精密儀器需放在籠內才可進行運作或量測。或者也可以再開一個洞,例如金屬機身構造的的智能手機。

(3) 消除一種誤解:不要認為輻射是由晶振直接造成的,事實上晶振個體較小,它直接影響的是近場輻射(表現為晶振與其他導體(如參考接地板)之間形成的寄生電容),造成遠場輻射的直接因素是電纜或產品中最大尺寸與輻射頻率波長可以比擬的導體;

(4)此外,將晶振外殼接地可以在一定程度上減少這種干擾疊加到系統上。

責任編輯人:CC

-

pcb

+關注

關注

4317文章

23004瀏覽量

396247 -

晶振

+關注

關注

34文章

2824瀏覽量

67901

原文標題:晶振為什么不能放置在PCB邊緣?

文章出處:【微信號:gh_3a15b8772f73,微信公眾號:硬件工程師煉成之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電磁兼容(EMC):晶振為什么不能放置在PCB邊緣?

晶振不能放置在PCB邊緣的原因?

晶振不能放置在PCB邊緣的原因是什么

晶振為什么不能放置在PCB邊緣?

晶振不能放置在PCB邊緣的原因是什么

晶振不能放置在PCB邊緣的原因是什么

評論