一、高速ADC

1.背景知識

隨著計算機技術(shù)、通信技術(shù)和微電子技術(shù)的高速發(fā)展,大大促進了ADC技術(shù)的發(fā)展,ADC作為模擬量與數(shù)據(jù)量接口的關(guān)鍵部件,廣泛應(yīng)用于各領(lǐng)域,在信息技術(shù)中起著重要作用。ADC同計算機一樣,經(jīng)歷了低速到高速的發(fā)展過程。ADC的低速(轉(zhuǎn)換時間大于300uS )結(jié)構(gòu)有積分型、斜坡型、跟蹤型;ADC的中速(轉(zhuǎn)換時間在1uS-300uS )結(jié)構(gòu)有逐次逼近型;ADC的高速(轉(zhuǎn)換時間小于1uS)結(jié)構(gòu)有閃爍型、分區(qū)式以及高分辨率結(jié)構(gòu)的∑-△型。這些不同的結(jié)構(gòu)滿足了實際應(yīng)用的廣泛性和多樣性的需求,其中高速ADC已成為決定諸如雷達、通信、電子對抗、航天航空、導(dǎo)彈、測控、地展、醫(yī)療、儀器儀表、圖像、高性能控制器及數(shù)字通信系統(tǒng)等現(xiàn)代化電子設(shè)備性能的重要環(huán)節(jié)。

2.基本原理

目前的高速ADC主要采用了以下兩種結(jié)構(gòu)形式。一種是全并行結(jié)構(gòu),也叫Flash結(jié)構(gòu)。這種結(jié)構(gòu)的ADC至少有2“-1個比較器,例如,一個八位ADC就至少有255個比較器。當(dāng)ADC分辨率增加時,不僅電路體積龐大,而且功耗猛增,也易出現(xiàn)“火花碼’,,因而一般用于分辨率較低的ADC,如六位、八位ADC.另一 種 結(jié) 構(gòu)形式稱為分區(qū)式結(jié)構(gòu)或折疊式結(jié)構(gòu),如兩步法、多步法。其電路結(jié)構(gòu)主要包含了S/H(或T/H)放大器、Flash A/D轉(zhuǎn)換器、時標(biāo)電路及數(shù)字誤差校正電路等。分區(qū)式結(jié)構(gòu)ADC克服了純Flash結(jié)構(gòu)ADC隨著分辨率增加,電路體積龐大、功耗猛增的缺點但又帶來另一個問題,即差分放大器和其中與第二次轉(zhuǎn)換處理輸入電壓有關(guān)的電路引入的誤差,這些誤差將超過轉(zhuǎn)換器允許的誤差,因此必須引入數(shù)字誤差校正。

當(dāng)前又有一種名為“流水線”的結(jié)構(gòu),它也是基于Flash結(jié)構(gòu)的多步轉(zhuǎn)換結(jié)構(gòu)(分區(qū)式),它是SAR和Flash兩種相結(jié)合的一種結(jié)構(gòu)。這種結(jié)構(gòu)實際上是犧牲ADC的速度來換取精度,因此適于較高精度的高速ADC.

二、流水線ADC結(jié)構(gòu)

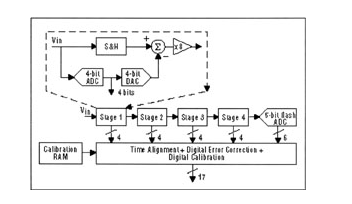

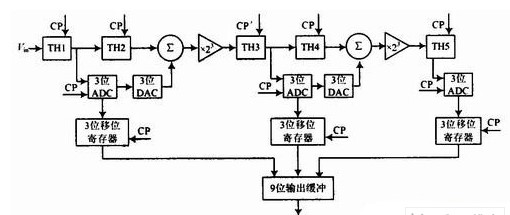

下圖為12位流水線ADC的結(jié)構(gòu)圖。輸入Vin首先被采樣/保持(S&H)電路所采樣,同時第一級的閃速ADC把它量化為3位,此3位輸出送給一3位的DAC(具有12位精度),輸入信號減去此DAC的輸出,放大4倍送給下一級(第二級),繼續(xù)重復(fù)上述過程,每級提供3位,直到最后一級4位閃速ADC。對應(yīng)某一次采樣,由于每級在不同的時間得到變換結(jié)果,因此在進行數(shù)字誤差校正前用移位寄存器對各級的結(jié)果先按時間對準(zhǔn)。注意只要某一級完成了某一采樣的變換,得到結(jié)果并把差值送給下一級,它就可以處理下一個采樣。因此流水線操作提高了處理能力。

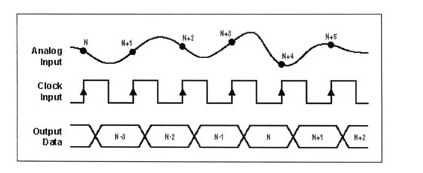

1. 延遲時間

由于每個采樣必須通過整個流水線才能得到數(shù)字誤差校正所需的各個位,因此流水線ADC有數(shù)據(jù)延遲。在圖1的例子中,大約要延時3個周期(見下圖)。

2. 數(shù)字誤差校正

大多數(shù)現(xiàn)代流水線ADC采用“數(shù)字誤差校正”技術(shù)來大大降低對閃速ADC(即內(nèi)部的每個比較器)的精度要求。3位的差值輸出其動態(tài)范圍是輸入信號Vin的1/8,然而隨后的增益只有4,因此給第二級的輸入只有第二級ADC 3位范圍的一半(在第一級的3位變換沒有誤差的情況下)。

如果第一級的3位閃速ADC的某一個比較器有很大的失調(diào),同時輸入電壓又正處于此比較點上,那么就會產(chǎn)生不正確3位碼和不正確的3位DAC輸出,此時產(chǎn)生了不同的差值。可以證明,只要放大后的差值沒有超出后續(xù)的3位ADC的范圍,以后產(chǎn)生的LSB碼加上前面不正確的3位MSB碼同樣能產(chǎn)生正確的ADC結(jié)果。實際上,四級流水線中的第一級3位閃速ADC只需4位的精度。數(shù)字誤差校正不能修正最后4位閃速轉(zhuǎn)換器產(chǎn)生的誤差。但是,這里產(chǎn)生的任何誤差要除以前面的累積增益(44),因此只要求最后一級的精度大于4位。

在本節(jié)第一張圖的例子種,雖然每級產(chǎn)生3位,但由于級間的增益是4,每級(第一級至第四級)的有效分辨率為2位。額外的位只是用于使尾數(shù)減半,使下一級3位ADC有額外的范圍進行數(shù)字校正。這種方法被稱之為級間“1位重疊”。因此整個ADC的有效位數(shù)是2+2+2+2+4=12位。

3. 元件精度

數(shù)字校正不能修正每個DAC和增益放大器的增益和線性特性。特別是前端的采樣保持電路,DAC需要12位的精度。但是隨后各級的元件只需較低的精度(如,第二級10位精度,第三級8位,等等),因為他們的誤差要除以前面的級間增益。通常利用這一事實把流水線逐級做小來進一步降低功耗。

在大多數(shù)采用CMOS和BiCMOS技術(shù)的流水線ADC中,采樣/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的單開關(guān)電容電路來實現(xiàn)。限制MDAC精度的主要因素是內(nèi)在的電容不匹配。純雙極型實現(xiàn)方法更加復(fù)雜,主要受電流源DAC和級間增益放大器中電阻不匹配影響。通常12位或更高精度都需要阻容修正和數(shù)字校正,特別是第一級。

4. 數(shù)字標(biāo)定

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用數(shù)字標(biāo)定來保證其優(yōu)越的精度和動態(tài)性能。MAX1200系列是CMOS流水線ADC,它由四級4位(其中一位重疊)和最后的5位閃速ADC構(gòu)成,總位數(shù)是3+3+3+3+5=17位(參見圖3)。額外的1到3位是數(shù)字標(biāo)定用來量化誤差項來達到更高的精度,舍掉它們后,最后得到14位或16位的精度。

標(biāo)定從第三級的MDAC開始。第三級以上的MDAC誤差已經(jīng)足夠小,不必標(biāo)定。第三級的輸出經(jīng)剩余的流水線ADC數(shù)字化后,誤差項存入片內(nèi)的RAM中,第三級標(biāo)定后,就可以用同樣的方式由第三級來標(biāo)定第二級,同樣,第二級標(biāo)定后,再標(biāo)定第一級。為了使標(biāo)定免受噪聲的影響,采用取平均的方法(特別是第一和第二級的MDAC)。在正常轉(zhuǎn)換期間,從RAM中取出標(biāo)定的誤差項來調(diào)整數(shù)字誤差校正后的輸出結(jié)果。

責(zé)任編輯人:CC

-

adc

+關(guān)注

關(guān)注

98文章

6452瀏覽量

544149 -

流水線ADC

+關(guān)注

關(guān)注

0文章

3瀏覽量

1825

發(fā)布評論請先 登錄

相關(guān)推薦

流水線ADC結(jié)構(gòu)解析 流水線ADC和其它ADC的比較

如何設(shè)計一種適用于流水線ADC的運算放大器?

一種流水線結(jié)構(gòu)AD轉(zhuǎn)換器的速度分析方法

流水線ADC

流水線ADC的行為級仿真

基于VHDL_AMS的流水線ADC結(jié)構(gòu)式建模方法與仿真

一種改進運放共享結(jié)構(gòu)的11位流水線ADC設(shè)計

一文讀懂處理器流水線

采用三級流水線結(jié)構(gòu)的9位100 MSPS A/D轉(zhuǎn)換器的設(shè)計

了解流水線型ADC

什么是流水線 Jenkins的流水線詳解

流水線ADC的內(nèi)部結(jié)構(gòu)和工作原理是什么

一文詳解流水線ADC結(jié)構(gòu)

一文詳解流水線ADC結(jié)構(gòu)

評論