如今,電子產(chǎn)品日益緊湊的趨勢要求多層印刷電路板的三維設(shè)計。但是,層堆疊提出了與此設(shè)計觀點相關(guān)的新問題。其中一個問題就是為項目獲取高質(zhì)量的疊層構(gòu)建。

隨著生產(chǎn)越來越多的由多層組成的復雜印刷電路,PCB的堆疊在變得尤為重要。

良好的PCB疊層設(shè)計對于減少PCB回路和相關(guān)電路的輻射至關(guān)重要。相反,不良的堆積可能會顯著增加輻射,從安全角度來看這是有害的。

什么是PCB疊層?

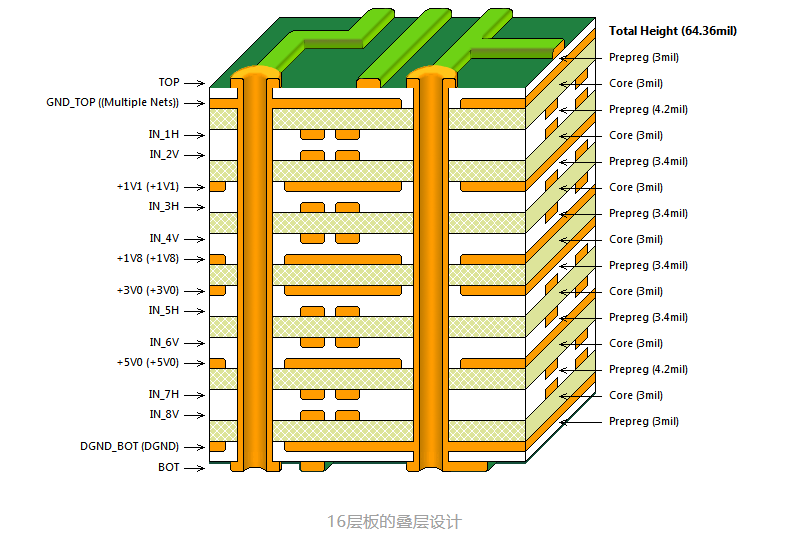

在最終布局設(shè)計完成之前,PCB疊層將PCB的絕緣體和銅分層放置。開發(fā)有效的堆疊是一個復雜的過程。PCB在物理設(shè)備之間連接電源和信號,而電路板材料的正確分層直接影響其功能。

為什么要進行PCB疊層?

開發(fā)PCB疊層對于設(shè)計高效電路板至關(guān)重要。PCB疊層具有許多好處,因為多層結(jié)構(gòu)可以提高能量分配能力、防止電磁干擾、限制交叉干擾并支持高速信號傳輸。

盡管堆疊的主要目的是通過多層將多個電子電路放置在一塊板上,但PCB堆疊的結(jié)構(gòu)也提供了其他重要優(yōu)勢。這些措施包括最大程度地降低電路板對外部噪聲的脆弱性,并減少高速系統(tǒng)的串擾和阻抗問題。

良好的PCB疊層也可以幫助確保較低的最終生產(chǎn)成本。通過最大化效率并改善整個項目的電磁兼容性,PCB疊層可以有效節(jié)省的時間和資金。

圖源:pixabay

PCB疊層設(shè)計注意事項和規(guī)則

● 層數(shù)

簡單的堆疊可能包括四層PCB,而更復雜的板則需要專業(yè)的順序?qū)訅骸1M管更為復雜,但更高的層數(shù)允許設(shè)計人員有更多的布置空間,而不會增加遇到不可能的解決方案的風險。

通常,需要八層或更多層才能獲得最佳的層布置和間隔以最大化功能。在多層板上使用質(zhì)量平面和電源平面還可以減少輻射。

● 層排列

構(gòu)成電路的銅層和絕緣層的布置構(gòu)成了PCB重疊操作。防止PCB翹曲需在布置各層時,使板的橫截面對稱且平衡。例如,在八層板中,第二層和第七層厚度應相似以實現(xiàn)最佳平衡。

信號層應始終與平面相鄰,而電源平面和質(zhì)量平面則嚴格耦合在一起。最好使用多個接地層,因為它們通常可以減少輻射并降低接地阻抗。

● 圖層材質(zhì)類型

每個基板的熱、機械和電特性以及它們?nèi)绾蜗嗷プ饔脤x擇PCB疊層材料選擇至關(guān)重要。

電路板通常由堅固的玻璃纖維基板芯組成,可提供PCB的厚度和剛性。某些柔性PCB可能由柔性高溫塑料制成。

表面層是附著在板上的由銅箔制成的薄箔。在雙面PCB的兩面都存在銅,銅的厚度根據(jù)PCB疊層的層數(shù)而變化。

在銅箔的頂部覆蓋一層阻焊層,以使銅線跡與其他金屬接觸。這種材料對于幫助用戶避免焊接跳線的正確位置至關(guān)重要。

在阻焊層上施加絲網(wǎng)印刷層,以添加符號,數(shù)字和字母,以便于組裝,并使人們可以更好地理解電路板。

● 確定布線和通孔

設(shè)計人員應該在層之間的中間層上布線高速信號。這允許接地平面提供屏蔽,該屏蔽包含從軌道高速發(fā)射的輻射。

信號電平靠近平面電平的放置使返回電流可以在相鄰平面上流動,從而將返回路徑電感降至最低。相鄰電源和接地層之間沒有足夠的電容,無法使用標準構(gòu)造技術(shù)提供500 MHz以下的去耦。

● 層之間的間距

由于電容減小,因此信號和電流返回平面之間的緊密耦合至關(guān)重要。電源和接地層也應緊密耦合在一起。

信號層即使位于相鄰平面中也應始終彼此靠近。層之間的緊密耦合和間隔對于不間斷的信號和整體功能至關(guān)重要。

總結(jié)

PCB疊層技術(shù)存在許多不同的多層PCB板設(shè)計。當涉及多層時,必須結(jié)合考慮內(nèi)部結(jié)構(gòu)和表面布局的三維方法。隨著現(xiàn)代電路的高運行速度,必須進行仔細的PCB疊層設(shè)計以提高分配能力并限制干擾。設(shè)計不良的PCB可能會降低信號傳輸、可生產(chǎn)性、功率傳輸和長期可靠性。

責任編輯:xj

原文標題:PCB疊層設(shè)計的介紹與應用

文章出處:【微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

pcb

+關(guān)注

關(guān)注

4317文章

23003瀏覽量

396236 -

基板

+關(guān)注

關(guān)注

2文章

266瀏覽量

22967 -

疊層

+關(guān)注

關(guān)注

0文章

28瀏覽量

9828

原文標題:PCB疊層設(shè)計的介紹與應用

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何根據(jù)貼片疊層電感參數(shù)進行選型

一文讓你了解PCB六層板布局

PCB多層板為什么都是偶數(shù)層?奇數(shù)層不行嗎?

什么是PCB疊層?PCB疊層設(shè)計原則

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

要畫好PCB,先學好信號完整性!

PCB疊層結(jié)構(gòu)與阻抗計算筆記分享

PCB疊層設(shè)計優(yōu)化ESD性能設(shè)計

PCB疊層設(shè)計詳解

PCB疊層設(shè)計示例詳解

4層以上的PCB設(shè)計,如何選取合適的疊層方案?

各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)設(shè)計

DDR電路的疊層與阻抗設(shè)計!

DDR電路的疊層與阻抗設(shè)計

鈣鈦礦疊層電池知識整理匯總

為什么要進行PCB疊層

為什么要進行PCB疊層

評論