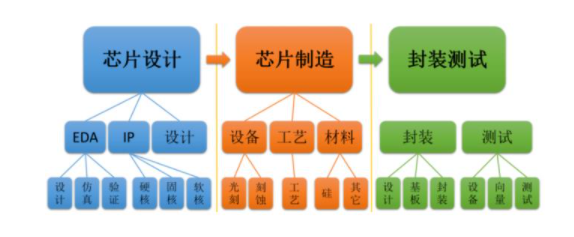

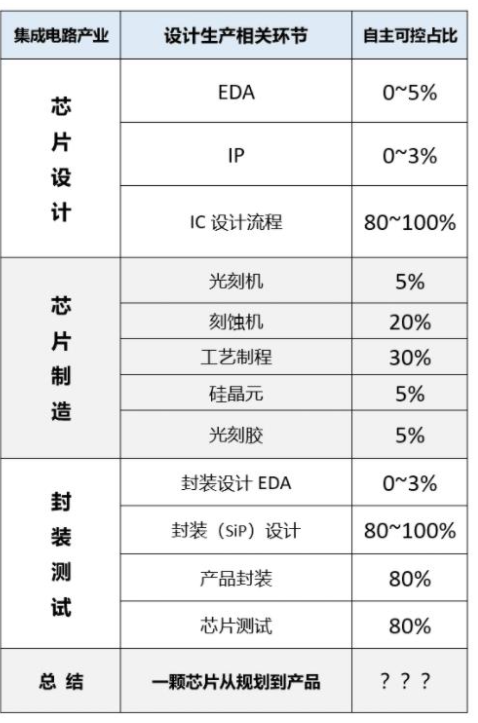

首先,什么叫自主可控,最直觀的理解就是當別人“卡脖子”的時候不會被卡住。集成電路產業通常被分為芯片設計、芯片制造、封裝測試三大領域,參看下圖:

我們逐一進行分析,芯片設計主要從EDA、IP、設計三個方面來分析;芯片制造主要從設備、工藝和材料三個方面來分析;封裝測試則從封裝設計、產品封裝和芯片測試幾方面來分析。

芯 片 設 計

如何開始一款芯片設計呢?

首先要有工具(EDA),然后借助現有的資源(IP),加上自己的構思和規劃就可以開始芯片設計了。

這里,我們就從芯片設計工具EDA,知識產權IP,以及集成電路的設計流程來分析芯片設計。

1.1 EDA

EDA(Electronic Design Automation)電子設計自動化,常指代用于電子設計的軟件。

曾經有人跟我說:“EDA有啥呀,不就是個工具嘛?”是啊,確實就是個工具,可是沒這個工具,你啥也設計不了啊!

現在的大規模集成電路在芝麻粒大小的1平方毫米內可以集成1億只以上的晶體管,這些晶體管之間的連接網絡更是多達數億個。當今主流的SoC芯片,其晶體管數量已經超過百億量級。如果沒有精準的,功能強大的EDA工具,怎么設計呢?

EDA是芯片設計的必備工具,目前,Synopsys、Cadence和Mentor(Siemens EDA)占據著超過90%以上的市場份額。在10納米以下的高端芯片設計上,其占有率甚至高達100%。也就是說,現在研發一款10nm以下的芯片,沒有以上三家的EDA工具幾乎是不可能實現的。

下表所示是目前芯片設計中主流的EDA工具:

芯片設計分為設計、仿真、驗證等環節,對應的EDA工具分為設計工具、仿真工具、驗證工具等。

設計工具解決的是模型的構建,也就是從0到1(從無到有)的問題,仿真和驗證工具解決模型的確認,也就是1是1還是0.9或者1.1的問題。因此,從EDA開發的角度,設計工具的開發難度更大。

此外,設計規模越大,工藝節點要求越高,EDA工具的開發難度也越大。

國產EDA工具目前在一些仿真驗證點工具上取得一些成績,在模擬電路設計方面也初步具備了全流程工具,但在大規模集成電路設計上和三大廠商還有很大的差距,尤其在高端數字芯片設計流程上基本還是空白。

1.2 IP

IP(Intelligent Property)代表著知識產權的意思,在業界是指一種事先定義、經過驗證的、可以重復使用,能完成特定功能的模塊,IP是構成大規模集成電路的基礎單元,SoC甚至可以說是基于IP核的復用技術。

IP一般分為硬核、軟核和固核。IP硬核一般已經映射到特定工藝,經過芯片制造驗證,具有面積和性能可預測的特點,但靈活性較小;

IP軟核以HDL形式提交,靈活性強,但性能方面具有不可預測性;

IP固核通過布局布線或利用通用工藝庫,對性能和面積進行了優化,比硬核靈活,比軟核在性能和面積上更可預測,是硬核和軟核的折中。

下表為目前全球前10大IP提供商,可以看到中國有兩家入圍前十,但是兩家市場份額加起來也僅有3%,而ARM一家就占據了40%以上的市場份額,美國的企業則占據了30%的市場份額,如果ARM被英偉達收購,基本上IP市場就是美國的天下了。此外我們也發現,全球最大的兩家EDA公司Synopsys和Cadence,在IP領域也同樣占據的第二、第三的位置。

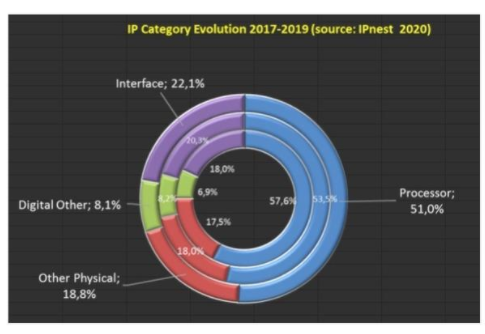

下圖所示為IP的種類,其中處理器占51%,接口IP占22.1%,數字類占8.1%,其他占18.8%,處理器類ARM一家獨大,在接口類IP中,Synopsys是業界領導者。

我們需要考慮的是,在設計的芯片中那些IP是自主設計的,那些是外購的,這些外購的IP是否存在不可控因素?如果你設計的SoC僅僅是把別人的IP打包整合,那自主可控性就要大打折扣了。

下面,我們以華為麒麟980為例,了解一下芯片研發中的IP使用情況。

麒麟980芯片集成的主要部件有CPU、GPU(俗稱顯卡)、ISP(處理拍照數據)、NPU(人工智能引擎)和基帶(負責通信)。

根據華為官方資料,ISP是華為自研,NPU是華為和寒武紀合作的成果,至于CPU(Cortex-A76)和GPU(Mali-G76)則是華為向ARM公司購買的授權,包括指令集授權和內核授權。

如果沒有IP授權,還有沒有可能自研麒麟980芯片,目前看來,沒有 。

1.3 設計流程

芯片設計流程通常可分為:數字IC設計流程和模擬IC設計流程。

數字IC設計流程:芯片定義 → 邏輯設計 → 邏輯綜合 → 物理設計 → 物理驗證 → 版圖交付。

芯片定義(Specification)是指根據需求制定芯片的功能和性能指標,完成設計規格文檔。

邏輯設計(Logic Design)是指基于硬件描述語言在RTL(Register-Transfer Level)級實現邏輯設計,并通過邏輯驗證或者形式驗證等驗證功能正確。

邏輯綜合(Logic Synthesis)是指將RTL轉換成特定目標的門級網表,并優化網表延時、面積和功耗。

物理設計(Physical Design)是指將門級網表根據約束布局、布線并最終生成版圖的過程,其中又包含:數據導入 → 布局規劃 → 單元布局 → 時鐘樹綜合 → 布線。

數據導入是指導入綜合后的網表和時序約束的腳本文件,以及代工廠提供的庫文件。

布局規劃是指在芯片上規劃輸入/輸出單元,宏單元及其他主要模塊位置的過程。

單元布局是根據網表和時序約束自動放置標準單元的過程。

時鐘樹綜合是指插入時鐘緩沖器,生成時鐘網絡,最小化時鐘延遲和偏差的過程。

布線是指在滿足布線層數限制,線寬、線間距等約束條件下,根據電路關系自動連接各個單元的過程。

物理驗證(Physical Verificaiton)通常包括版圖設計規則檢查(DRC),版圖原理圖一致性檢查(LVS)和電氣規則檢查(ERC)等。

版圖交付(Tape Out)是在所有檢查和驗證都正確無誤的前提下,傳遞版圖文件給代工廠生成掩膜圖形,并生產芯片。

模擬IC設計流程:芯片定義 → 電路設計 → 版圖設計 → 版圖驗證 → 版圖交付。

其中芯片定義和版圖交付和數字電路相同,模擬IC在電路設計、版圖設計、版圖驗證和數字電路有所不同。

模擬電路設計是指根據系統需求,設計晶體管級的模擬電路結構,并采用SPICE等仿真工具驗證電路的功能和性能。

模擬版圖設計是按照設計規則,繪制電路圖對應的版圖幾何圖形,并仿真版圖的功能和性能。

模擬版圖驗證是驗證版圖的工藝規則、電氣規則以及版圖電路圖一致性檢查等。

這里,我們做一個簡單的總結:

芯片設計:就是在EDA工具的支持下,通過購買IP授權+自主研發(合作開發)的IP,并遵循嚴格的集成電路設計仿真驗證流程,完成芯片設計的整個過程。在這個過程中,EDA、IP、嚴格的設計流程三者缺一不可。

目前看來,在這三要素中最先可能實現自主可控的就是設計流程了。

下表列出了當前世界前10的芯片設計公司,供大家參考。

芯片制造目前是集成電路產業門檻最高的行業,怎么看待門檻的高低呢,投資越高、玩家越少就表明門檻越高,目前在高端芯片的制造上也僅剩下臺積電(TSMC)、三星(SAMSUNG)和英特爾(Intel)三家了。下面,我們分別從設備、工藝和材料三個方面來分析芯片制造,尋找我們和先進制造技術的差距。

2.1 設備

芯片制造需要經過兩千多道工藝制程才能完成,每個步驟都要依賴特定設備才能實現。

芯片制造中,有三大關鍵工序:光刻、刻蝕、沉積。三大工序在生產過程中不斷重復循環,最終制造出合格的芯片。

三大關鍵工序要用到三種關鍵設備,分別是光刻機、刻蝕機、薄膜沉積設備。三大設備占所有設備投入的22%、22%、20%左右,是三種占比最高的半導體設備。

下面就以最為典型的光刻機和刻蝕機為例進行介紹并分析自主可控。

1)光刻機

光刻機的原理其實像幻燈機一樣,就是把光通過帶電路圖的掩膜(也叫光罩)Mask投影到涂有光刻膠的晶圓上。60年代末,日本尼康和佳能開始進入這個領域,當時的光刻機并不比照相機復雜多少。

為了實現摩爾定律,光刻技術需要每兩年把曝光關鍵尺寸(CD)降低30%-50%。需要不斷降低光刻機的波長λ。然而,波長被卡在193nm無法進步長達20年。后來通過工程上最簡單的方法解決,在晶圓光刻膠上方加1mm厚的水,把193nm的波長折射成134nm,稱為浸入式光刻。

浸入式光刻成功翻越了157nm大關,加上后來不斷改進的鏡頭、多光罩、Pitch-split、波段靈敏光刻膠等技術,浸入式193nm光刻機一直可以做到今天的7nm芯片(蘋果A12和華為麒麟980)。

2)EVU光刻機

EUV極紫外光刻(Extreme Ultra-Violet)是一種使用極紫外(EUV)波長的新一代光刻技術,其波長為13.5納米。由于光刻精度是幾納米,EUV對光的集中度要求極高,相當于拿個手電照到月球光斑不超過一枚硬幣。反射的鏡子要求長30cm起伏不到0.3nm,相當于北京到上海的鐵軌起伏不超過1毫米。一臺EUV光刻機重達180噸,超過10萬個零件,需要40個集裝箱運輸,安裝調試要超過一年時間。

2000年時,日本尼康還是光刻機領域的老大,到了2009年ASML已經遙遙領先,市場占有率近7成。目前,最先進的光刻機也只有ASML一家可以提供了。

國內的情況,上海微電子(SMEE)已經有分辨率為90nm的光刻機,新的光刻機也在研制中。

在集成電路制造中,光刻只是其中的一個環節,另外還有無數先進科技用于前后道工藝中。

3)刻蝕機

刻蝕是將晶圓表面不必要的材質去除的過程。刻蝕工藝位于光刻之后。

光刻機用光將掩膜上的電路結構復制到硅片上,刻蝕機把復制到硅片上的電路結構進行微雕,雕刻出溝槽和接觸點,讓線路能夠放進去。

按照刻蝕工藝分為干法刻蝕以及濕法刻蝕,干法刻蝕主要利用反應氣體與等離子體進行刻蝕,濕法刻蝕工藝主要是將刻蝕材料浸泡在腐蝕液內進行刻蝕。

干法刻蝕在半導體刻蝕中占據主流,市場占比達到95%,其最大優勢在于能夠實現各向異性刻蝕,即刻蝕時可控制僅垂直方向的材料被刻蝕,而不影響橫向材料,從而保證細小圖形保真性。濕法刻蝕由于刻蝕方向的不可控性,在先進制程很容易降低線寬,甚至破壞線路本身,導致芯片品質變差。

目前普遍采用多重模板工藝原理,即通過多次沉積、刻蝕工藝實現需要的特征尺寸,例如14nm制程所需使用的刻蝕步驟達到64次,較 28nm提升60%;7nm制程所需刻蝕步驟更是高達140次,較14nm提升118%。

下圖所示為多次刻蝕原理。

和光刻機一樣,刻蝕機的廠商也相對較少,代表企業主要是美國的 Lam Research(泛林半導體)、AMAT(應用材料)、日本的TEL(東京電子)等企業。這三家企業占據全球半導體刻蝕機的94%的市場份額,而其他參與者合計僅占6%。其中,Lam Research 占比高達55%,為行業龍頭,東京電子與應用材料分別占比20%和19%。

國內的情況,目前刻蝕設備代表公司為中微公司、北方華創等。中微公司較為領先,工藝節點已經達到5nm。在全球前十大晶圓企業中,中微公司已經進入其中六家,作為臺積電的合作伙伴協同驗證14nm/7nm/5nm等先進工藝。

基于此,如果目前在光刻機領域我們還無力做出改變,那么已經有一定優勢的刻蝕機勢必會成為國產替代的先鋒。

2.2 工藝制程

芯片制造過程需要兩千多道工藝制程,下面,我們按照8大步驟對芯片制造工藝進行簡單介紹。

1.)光刻(光學顯影)

光刻是經過曝光和顯影程序,把光罩上的圖形轉換到光刻膠下面的晶圓上。光刻主要包含感光膠涂布、烘烤、光罩對準、 曝光和顯影等程序。曝光方式包括:紫外線、極紫外光、X射線、電子束等。

2.)刻蝕(蝕刻)

刻蝕是將材料使用化學反應或物理撞擊作用而移除的技術。干刻蝕(dry etching)利用等離子體撞擊晶片表面所產生的物理作用,或等離子體與晶片表面原子間的化學反應,或者兩者的復合作用。濕刻蝕(wet etching)使用的是化學溶液,經過化學反應達到刻蝕的目的。

3)化學氣相沉積(CVD)

CVD利用熱能、放電或紫外光照射等化學反應的方式,將反應物在晶圓表面沉積形成穩定固態薄膜(film)的一種沉積技術。CVD技術在芯片制程中運用極為廣泛,如介電材料(dielectrics)、導體或半導體等材料都能用CVD技術完成。

4)物理氣相沉積(PVD)

PVD是物理制程而非化學制程,一般使用氬等氣體,在真空中將氬離子加速以撞擊濺鍍靶材后,可將靶材原子一個個濺擊出來,并使被濺擊出來的材質如雪片般沉積在晶圓表面。

5)離子植入(Ion Implant)

離子植入可將摻雜物以離子型態植入半導體組件的特定區域上,以獲得精確的電特性。離子先被加速至足夠能量與速度,以穿透(植入)薄膜,到達預定的植入深度。離子植入可對植入區內的摻質濃度加以精密控制。

6)化學機械研磨(CMP)

化學機械研磨技術具有研磨性物質的機械式研磨與酸堿溶液的化學式研磨兩種作用,可以使晶圓表面達到全面性的平坦化,以利后續薄膜沉積。

7)清洗

清洗的目的是去除金屬雜質、有機物污染、微塵與自然氧化物;降低表面粗糙度;幾乎所有制程前后都需要清洗。

8)晶片切割(Die Saw)

晶片切割是將加工完成的晶圓上一顆顆晶粒裸芯片(die)切割分離,便于后續封裝測試。

雖然不同的Foundry廠的流程大致相同,但不同的工藝控制能力造就了各廠家在先進制程上的區別,隨著制程進入5nm,能夠量產的芯片制造商就屈指可數了,目前能夠量產5nm芯片的只有TSMC和SAMSUNG。

兩千多道工藝制程中隱藏著Foundry的無窮的智慧和雄厚的財力,并不是說有了先進的設備,就能造出合格的芯片。

雖然先進制程是技術發展的方向,我們也不能忽視成熟制程。成熟制程依然有很大市場份額。下圖是按成熟制程(節點≥40nm)產能排序的全球晶圓代工廠商Top榜單。

可以看出,成熟制程產能排名前四的廠商分別為:臺積電(市占率28%),聯電(13%),中芯國際(11%),三星(10%)。成熟制程在2020年非常火爆,產能嚴重短缺,這給各大晶圓代工廠帶來了巨大的商機。而從2021年的產業發展形勢來看,這種短缺狀況在近期內還難以緩解。

2.3 材料

生產集成電路的材料有成千上萬種,我們就以最為典型的硅晶圓和光刻膠進行分析。

1)硅晶圓

硅晶圓是集成電路行業的糧食,是最主要最基礎的集成電路材料,90%以上的芯片在硅晶圓上制造,目前300mm硅晶圓是芯片制造的主流材料,使用比例超過70%。曾經,我國300mm半導體硅片100%依賴進口,是我國集成電路產業鏈建設與發展的主要瓶頸。

全球主要的半導體硅晶圓供應商包括日本信越化學(Shin-Estu)、日本盛高(SUMCO)、德國Siltronic、韓國SK Siltron以及中國臺灣的環球晶圓、合晶科技等公司。五大晶圓供貨商的全球市占率達到了92%,其中日本信越化學占27%,日本盛高占26%,臺灣環球晶圓占17%,德國Silitronic占13%,韓國SK Siltron占9%。

下表列出了全球10大硅晶圓提供商,供參考。

國內的情況,中國大陸半導體硅晶圓銷售額年均復合增長率達到41.17%,遠高于同期全球半導體硅片市場的25.75%。但這塊市場并沒有掌握在本土廠商手中,在打造國產化產業鏈的今天,還有很大的空間供國內晶圓制造商去發展。

2)光刻膠

光刻膠是光刻過程最重要的耗材,光刻膠的質量對光刻工藝有著重要影響。光刻膠可分為半導體光刻膠、面板光刻膠和PCB光刻膠。其中,半導體光刻膠的技術壁壘最高。

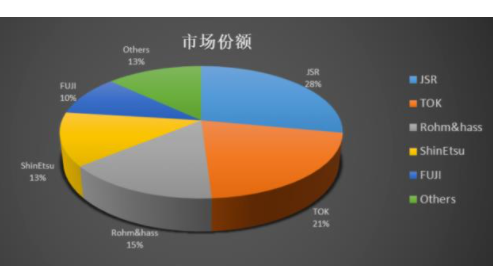

目前全球光刻膠主要企業有日本合成橡膠(JSR)、東京應化(TOK)、信越化學(ShinEtsu)、富士電子(FUJI)、美國羅門哈斯(Rohm&Hass)等,市場集中度非常高,所占市場份額超過85%。

下圖顯示的是光刻膠企業的市場占有率。

高分辨率的半導體光刻膠是半導體化學品中技術壁壘最高的材料,日美企業技術領先國內企業二十年至三十年。從光刻膠技術水平來看,國內企業在缺乏經驗、缺乏專業技術人才、缺失關鍵上游原材料和設備的條件下,探索出一條自主研發之路,光刻膠高端技術短期內尚難突破,還要很長的路要走。在PCB領域,國產光刻膠具備了一定的量產能力,已經實現對主流廠商供貨。

封 裝 測 試

封裝測試是集成電路三大產業中的最后一個環節。一般認為封裝測試的技術含量和實現難度比前兩者低,但是隨著SiP及先進封裝技術的出現和迅速發展,需要重新定義芯片的封裝和測試。

SiP及先進封裝在封裝原來的三個特點:芯片保護、尺度放大、電氣連接的基礎上,增加了三個新特點:提升功能密度、縮短互聯長度、進行系統重構,因此其復雜程度和實現難度與傳統的封裝相比有很大程度的提升。

同時,SiP及先進封裝也給封裝測試提出了新的機遇和挑戰。

3.1 芯片封裝

我們從封裝設計和產品封裝兩方面來分析芯片封裝。

1)封裝設計

早先的封裝中沒有集成(Integration)的概念,封裝設計是比較簡單的,對工具要求也很低,Auto CAD就是常用的封裝設計工具,隨著MCM、SiP技術的出現,封裝設計變得越來越復雜,加上目前SiP、先進封裝、Chiplet、異構集成概念的市場接受度越來越高,封裝內集成的復雜度和靈活度急劇上升,對封裝設計的要求也越來越高。

SiP和先進封裝設計工具目前只有Cadence和 Siemens EDA(Mentor)兩家,Cadence是老牌的封裝設計EDA提供商,市場占有率高,用戶的忠誠度也比較高。

Siemens EDA(Mentor)是封裝設計領域的后起之秀,但其技術先進性上則體現了“后浪”的特點。業界大佬TSMC, Intel, SAMSUNG紛紛選擇Siemens EDA作為其先進封裝(HDAP)的首選工具,主要在于兩點:先進的設計工具和強悍的驗證工具。

首先我們說說設計工具,在一次技術論壇中,我說:“不同于傳統封裝設計,先進封裝和SiP設計對3D環境要求很高,3D設計環境不在于是否看上去很直觀、絢麗,而在于對客觀元素的精準描述,包括鍵合線、腔體、芯片堆疊、硅轉接板、2.5D集成、3D集成,Bump.。.”

在這一點上,Siemens EDA的SiP及先進封裝設計工具已經遠遠將其競爭對手拋在身后。下圖為先進封裝版圖設計工具XPD中的封裝設計3D截圖,4組芯片堆疊中,每組5顆芯片(4HBM+1Logic)以3D TSV連接在一起,和GPU一起集成在硅轉接板(2.5D TSV)上,硅轉接板和電阻、電容等一起集成在封裝基板上。

XPD中的先進封裝設計截圖(3D)

該設計中包含了3D集成、2.5D集成、倒裝焊、Bump、多基板集成等多種方式,在XPD設計環境中得到了精準的實現。

先進封裝驗證工具包括電氣驗證和物理驗證,電氣驗證包含80多條規則,對整個系統進行信號完整性、電源完整性、EMIEMC等電氣相關的檢查和驗證,物理驗證則是基于IC驗證工具Calibre,整合出Calibre 3D STACK,專門用于3D先進封裝的物理驗證。

隨著封裝內的集成度、設計復雜度越來越高,對工具的要求也越來越高,另外,在先進封裝領域,封裝設計和芯片設計的協同度日益提高,在某種程度上有逐漸融合的趨勢,因此對協同設計的要求也日益提升。

2)產品封裝

根據材料和工藝不同,封裝可以分為塑料封裝、陶瓷封裝和金屬封裝三種類型。

塑封主要基于有機基板,多應用于商業級產品,體積小、重量輕、價格便宜,具有大批量、低成本優勢,但在芯片散熱、穩定性、氣密性方面相對較差。

陶瓷封裝和金屬封裝則主要基于陶瓷基板,陶瓷封裝一般采用HTCC基板,金屬封裝則多采用LTCC基板,對于大功耗產品,散熱要求高,可選用氮化鋁基板。

陶瓷封裝特點包括:密封性好,散熱性能良好,對極限溫度的抵抗性好,容易拆解,便于問題分析;和金屬封裝相比體積相對小,適合大規模復雜芯片,適合航空航天等對氣密性有要求的嚴苛環境應用;但價格昂貴,生產周期長,重量和體積都比同類塑封產品大。

金屬封裝特點包括:密封性好,散熱性能良好,容易拆解,靈活性高;但體積相對較大,引腳數量較少,不適合復雜芯片,價格貴,生產周期長,需要組裝金屬外殼和基板,工序復雜,多應用于MCM設計,航空航天領域應用較為普遍。

陶瓷封裝和金屬封裝內部均為空腔結構,具有可拆解的優勢,便于故障查找和問題“歸零”, 因此受到航空航天等領域用戶的歡迎。

3.2 芯片測試

芯片測試的項目非常多,這里我們重點了解一下機臺測試的系統測試。

1)機臺測試

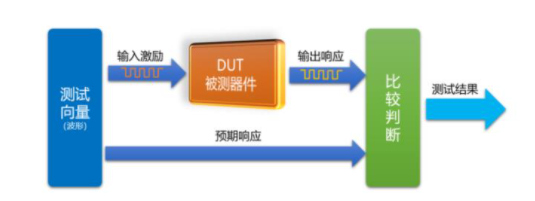

一般是指采用ATE(Automatic Test Equipment)自動測試設備來進行芯片測試,測試芯片的基本功能和相應的電參數。機臺可以提供待測器件DUT(Device Under Test)所需的電源、不同周期和時序的波形、驅動電平等。

測試向量(Test Vector)是每個時鐘周期應用于器件管腳的用于測試的邏輯1和邏輯0數據,是由帶定時特性和電平特性的波形代表,與波形形狀、脈沖寬度、脈沖邊緣或斜率以及上升沿和下降沿的位置都有關系。

測試向量可基于EDA工具的仿真向量(包含輸入信號和期望的輸出),經過優化和轉換,形成ATE格式的測試向量。利用EDA工具建立器件模型,通過建立一個Testbench仿真驗證平臺,對其提供測試激勵,進行仿真,驗證結果,將輸入激勵和輸出響應存儲,按照ATE向量格式,生成ATE向量文件。

2)系統測試

系統測試也稱為板級系統測試,是指模擬芯片真實的工作環境,對芯片進行各種操作,確認其功能和性能是否正常。

除了機臺測試和系統測試之外,還需要對芯片進行了一系列的試驗和考核,內容包括:熱沖擊、溫度循環、機械沖擊、掃頻震動、恒定加速度、鍵合強度、芯片剪切強度、穩態壽命、密封、內部水汽含量、耐濕氣等試驗。

只有所有的測試都順利通過了,一顆芯片才能算成功,作為合格的產品應用到下一個環節。

4.自主可控總結

最后,結合下面表格,我們對自主可控作一個簡單總結。

從表格可以看出,我們在IC設計流程、封裝(SiP)設計,以及在產品封裝、芯片測試環節的自主可控程度比較高;在刻蝕機、芯片工藝制程上有一定的自主可控性,而在EDA,IP,光刻機,硅晶元,光刻膠等環節自主可控的程度非常低,所以高端芯片很容易被“卡脖子”,因為高端芯片所用到的EDA,IP,光刻機,硅晶元,光刻膠幾乎全部依賴進口。

自主可控相對較高的IC設計流程、封裝(SiP)設計也幾乎全部依賴進口的EDA工具,在產品封裝和芯片測試環節,封裝設備和測試設備大約80%以上是進口設備;工藝制程上高端芯片同樣也無法自主生產。考慮到這些,不由得讓我們無法盲目樂觀,因為越往源頭挖掘,自主可控的比例就越低。

當別人不卡脖子的時候,不要趾高氣揚,似乎一切盡在掌控;當別人卡脖子的時候,不要突然發現,竟然全身上下都是脖子!

編輯:hfy

-

集成電路

+關注

關注

5381文章

11385瀏覽量

360875 -

IC設計

+關注

關注

37文章

1291瀏覽量

103768 -

soc

+關注

關注

38文章

4122瀏覽量

217941 -

芯片設計

+關注

關注

15文章

1001瀏覽量

54812

發布評論請先 登錄

相關推薦

集成電路市場的產業格局與產業結構

世界集成電路發展歷程及產業結構的變化

解讀中國集成電路產業新政

欠驅動機器人可控性綜述

在集成電路產業無錫因自主創新獲得了自主可控技術

中電國基南方集團射頻集成電路產業化項目啟動 將推動實現射頻集成電路核心芯片自主保障

合肥開始存儲式集成電路產業布局

國家自主可控集成電路生態行業產教融合共同體成立

如何開始一款芯片設計 深度解讀集成電路產業自主可控性

如何開始一款芯片設計 深度解讀集成電路產業自主可控性

評論