1、引 言

大多數接收機必須處理動態范圍很大的信號,這需要進行增益調整,以防止過載或某級產生互調,調整解調器的工作以優化工作。在現代無線電接收裝置中。可變增益放大器是電控的,并且當接收機中使用衰減器時,他們通常都是由可變電壓控制的連續衰減器。控制應該是平滑的并且與輸入的信號能量通常成對數關系(線性分貝)。在大多數情況下,由于衰落,AGC 通常用來測量輸入解調器的信號電平,并且通過反饋控制電路把信號電平控制在要求的范同內。

2 、系統總體設計

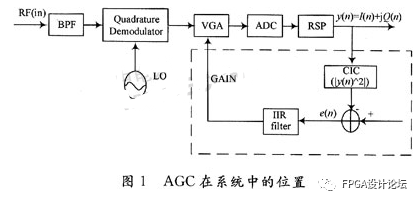

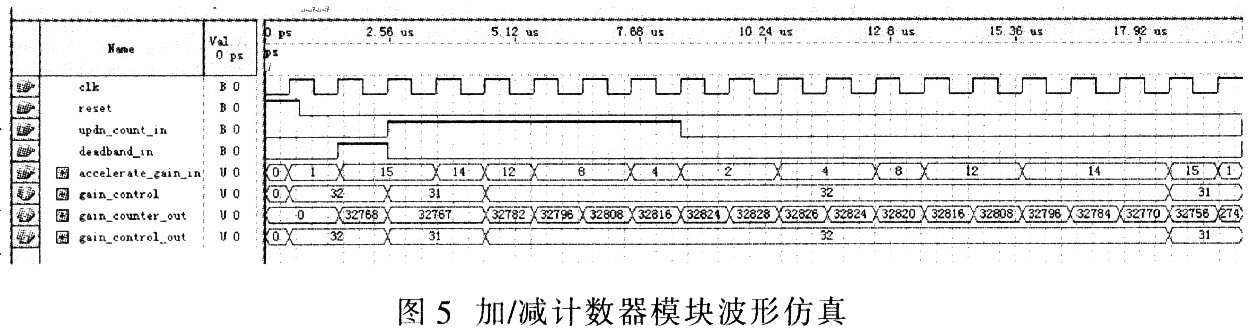

在本設計中,前端 TD_SCDMA 的射頻信號RF輸入后,經過 MAX2392 零中頻下變頻解調后進行增益處理。VGA 輸出的信號經過 ADC 變換后就成為數字中頻信號,經 RSP(接收信號處理器)處理輸出為 IF 數字信號。IF 信號可以經過 AGC 控制算法處理后控制 VGA 的增益。AGC 增益控制算法在數字部分來實現,在本設計中,AGC 電路可以有效提高鏈路的動態范圍(+25~-105 dBm),提高 ADC 輸出的 SNR,以使 DSP 能更容易地實現 Dw-PTS 同步。AGC 在系統中的位置如圖 1 虛線框所示:

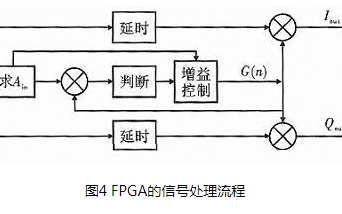

3 、AGC 系統的 FPGA 實現

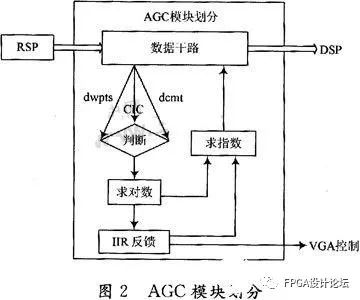

根據 AGC 所實現的功能,在 FPGA 中將 AGC 模塊分為如下幾個部分來實現:

3.1 數據千路模塊

從 RSP 接口來 10 位二進制補碼數據 I1 和 Q1,與求指數模塊傳送來的預放大增益 GAIN2 相乘后所得出的數據(仍取 10 位二進制補碼數據)將要傳送到 CIC 平均模塊,同時要分別與求指數模塊傳送來的放大增益 GAIN3 相乘,然后采取截短處理,取 8 位二進制補碼數據,I1′,Q1′,輸出到 DSP 中。

3.2 計算下行同步碼功率(SYNC_DL)模塊

計算下行同步碼功率(SYNC_DL)模塊對應于圖 2 中的判斷部分,是 AGC 中最為重要算法計算。TD_SCD-MA 每個幀有 6 400 個碼片,在其一幀 5 ms 的時間上是不連續的,因此只能求出下行同步碼(SYNC_DL)的功率值,以此為依據控制 VGA 的電壓值。

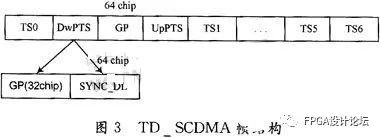

由圖 3 的 TD_SCDMA 的幀結構知道,下行同步碼(SYNC_DL)在下行導頻時隙(DwPTS)發射,SYNC_DL 的長為 64 個碼片,在其左邊和右邊各有 32 和 96 個碼片的保護時隙(GP)。為此,在 FPGA 中共用了 3 種不同的方法計算其功率值。

方法一 在 FPGA 內根據檢波法的原理計算下行同步碼 64 個碼片的功率(AGC 模塊圖 2 中的 dcmt 部分)。考慮 TD 的幀結構,保護時隙 GP 的功率很小,故從接收功率的時間分布上來看,與 GP 相比 SYNC_DL 段的功率較大。當用 SYNC_DL 段的 64 碼片之和除以 SYNC_DL 前后個 32 個碼片相加之和,結果大于 3 時,就可以判斷出 SYNC_DL 的大致位置。因此,基于這種方法,FPGA 在 5 ms 的周期中遍取 6 400 個碼片,每 64 個碼片做積分,依次向前滾動計算,同時做除法運算,最后即可計算出 SYNC_DL 在一幀 6 400 個碼片中的位置和能量,以此控制 VGA 的電壓和后續的計算。不過這種方法只有在信號質量很好,信號強度比較大的時候才計算準確。

方法二 由 DSP 方根據傳過來的數據,通過相干檢測法檢測出 SYNC_DL 的精確位置,并把這個位置參數傳送給 FPGA。FPGA 收到這一點的位置后,立既停止使用其自身檢波法求出的功率值,根據 DSP 傳過來的 SYNC_DL 的位置,計算出這一點之后的 64 個碼片的積分值,作為 SYNC_DL 的總功率,并以此控制 VGA 的電壓(AGC 模塊圖 2 中的 dwpts 部分)。這時求出來的總能量比較精確(DSP 提供的位置比 FPGA 自身檢波法求出來的精確),但是速度比較慢。

方法三 當信號的強度變得很弱,信號可能淹沒在了噪聲當中。這時無論是由 FPGA 的檢波法還是 DSP 的相干法都計算不出 SYNC_DL 的位置和能量。在這種情況下,認為在 5 ms 時域上信號連續,能量均衡,FPGA 求 5ms 幀的平均值,以此作為 SYNC_DL 的功率,并控制 VGA(AGC 模塊圖 2 中的 CIC 部分)。

3.3 求對數運算模塊

在本模塊,將上面得到的功率值進行求對數運算,以減少數據的運算量。用 FPGA 實現求對數運算時,可以先將數據歸一化在 1~2 之間,然后通過將數據平方后推導出最高位的方法逐位求出所求數據的二進制數值。假定自變量 X 歸一化在區間[1,2]內,用二進制數據可表示為 1.X1X2…Xn,則所求的對數值在區間[0,1]內,用二進制數據可表示為 0.Y1Y2…Ym,因而可用數學方法表示為 20.Y1Y2…Ym=1.X1X2…Xn,問題歸結為求 Y1Y2…Ym。將上式左右兩邊同時平方, 可以得出 2Y1Y2…Ym=(1.X11X21…Xn1)2,由此可推倒出 Y1 來。(X 為已知,若等式右邊數據小于 2,則 Y1=0;反之,若大于或等于 2,則 Y1=1)求出 Y1 后可以導出 20.Y2Y3…Ym=1.X11X21…Xn1,同理可推倒出 Y2。依此類推,可求出對數值的各位。

進行 FPGA 設計時,可以設計出一個平方比較單元依次求出對數值,同時要注意需要耗費的系統資源。

3.4 求指數運算模塊

經過求對數模塊后,一路數據傳送到 IIR 中,另一路數據則要傳送到 DSP 中進行算法運算,因此,需要增加一個求指數模塊,將對數模塊運算后的結果還原成原來的數據送到 DSP 中。指數換底公式可知:2x=ex1n2,由雙曲函數定義及特性可知:ex=sinh(x)+cosh(x),而當自變量 x 在[-π/4,7c/4]范圍內時,可以采用 FPGA 的 IP CORE(CORDIC 算法)實現雙曲正弦函數和雙曲余弦函數,因此在 FPGA 內部求以 2 為底的指數函數時,可以先將自變量歸一化在[0,1]內,然后將自變量乘以常系數 1n 2,由于 ln 2《π/4,故可以新乘得的數據作為新的自變量,利用 IPCORE 求出其雙曲正弦函數和雙曲余弦函數后將其相加,即可得到所需要的指數函數值。

3.5 IIR 反饋模塊

IIR 反饋模塊包括 3 部分:IIR 濾波單元、飽和反饋單元和 VGA 控制單元,其中 IIR 濾波單元負責將求對數模塊得出的數值與參考數值比較后得出的誤差數據 Uerr 作 IIR 濾波計算得出 Ufilter,然后依據相關算法計算出 Urssi。飽和反饋單元負責將 Urssi 與飽和限幅數據比較后得出誤差電壓 Uerr2,然后依照相關算法求出 U2 送到求指數模塊,從而能夠控制誤差反饋增益 Gain2。VGA 控制單元負責將 Urssi 進行飽和限幅后得到輸出控制電壓 Uda,量化后經過數模變換從而控制 VGA。

3.6 CIC 平均模塊

當 AGC 用于 WCDMA 系統時,可以將圖 2 中的判斷部分全部去掉,加入這個 CIC 平均模塊。CIC 平均模塊負責將預放大模塊求出的 I1 和 Q1 作為自變量,通過功率算法 P1′=I1*I1+Q1*Q1 求出 P1′,然后將 6 400 個工作頻率為 1.28 MHz 的 P1′平均,得出工作頻率為 1.28 MHz 的 P1。同樣得出 P2 后再求出 P1+P2。

在 FPGA 中對于相加運算,包括 CIC 實現部分的純整數相加算法和其他部分的小數相加算法。其中 CIC 運算部分的運算數據是二進制 10 位有符號數;對于相乘運算,包括 CIC 實現部分的純整數平方算法、CIC 實現部分的常系數小數相乘算法。

4、 結 語

以上介紹的在 FPGA 中實現 AGC 的算法,經過項目的驗證測試,效果比較好,DA 選用 ADS 的 5621,VGA 電壓調節范圍在 0.3~1.8 V 之間,共 45 個 dB 的調節范圍,因此 AGC 在+10~-35 之間起調節作用,信號低于 -45 dBm 時,VGA 電壓保持 1.8 V 最大值;高于+10 dBm 時,VGA 電壓保持在最小 0.3 V。經過測試,FPGA 可在+25~-105 dBm 范圍內搜索到 SYNC_DL 的位置。

此種 AGC 算法,計算相對簡單,運算速度快,不僅可用于 TD_SCDMA 信號,在計算下行同步碼能量時稍加改動,只做 CIC 平均運算,即可應用于 WCDMA 信號。

責任編輯人:CC

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601853 -

AGC

+關注

關注

0文章

160瀏覽量

51636

原文標題:基于FPGA的AGC算法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

實用AGC算法的工作原理及在音頻FPGA中的應用

DS-SS接收機全數字AGC的FPGA實現

AES中SubBytes算法在FPGA的實現

基于FPGA的大動態范圍數字AGC的實現

FPGA實現的FIR算法在汽車動態稱重儀表中的應用

FPGA的超聲波氣體流量計中AGC的原理及設計實現

一種基于實用AGC算法的音頻信號處理方法與FPGA實現的分析研究

實用AGC算法的工作原理及在音頻FPGA中的應用

如何使用FPGA實現全數字式前饋AGC的設計

FPGA中實現AGC的算法

FPGA中實現AGC的算法

評論