FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。

早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內部 buffer、LE、RAM 構建而成,LE 由 LUT(查找表)和 D 觸發器構成,RAM 也往往容量非常小。現在的FPGA不僅包含以前的 LE,RAM 也更大更快更靈活,管教 IOB 也更加的復雜,支持的 IO 類型也更多,而且內部還集成了一些特殊功能單元,包括:

DSP:實際上就是乘加器,FPGA 內部可以集成多個乘加器,而一般的 DSP 芯片往往每個 core 只有一個。換言之,FPGA 可以更容易實現多個 DSP core 功能。在某些需要大量乘加計算的場合,往往多個乘加器并行工作的速度可以遠遠超過一個高速乘加器。

SERDES:高速串行接口。將來 PCI-E、XAUI、HT、S-ATA 等高速串行接口會越來越多。有了 SERDES 模塊,FPGA 可以很容易將這些高速串行接口集成進來,無需再購買專門的接口芯片。

CPU core:分為 2 種,軟 core 和硬 core. 軟 core 是用邏輯代碼寫的 CPU 模塊,可以在任何資源足夠的 FPGA 中實現,使用非常靈活。而且在大容量的 FPGA 中還可以集成多個軟 core,實現多核并行處理。硬 core 是在特定的 FPGA 內部做好的 CPU core,優點是速度快、性能好,缺點是不夠靈活。

不過,FPGA 還是有缺點。對于某些高主頻的應用,FPGA 就無能為力了。現在雖然理論上 FPGA 可以支持的 500MHz,但在實際設計中,往往 200MHz 以上工作頻率就很難實現了。

FPGA 設計要點之一:時鐘樹

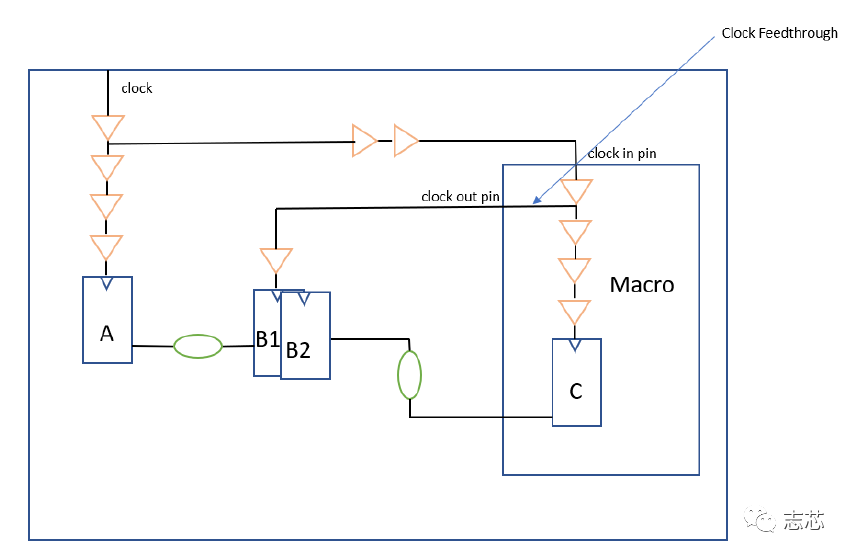

對于 FPGA 來說,要盡可能避免異步設計,盡可能采用同步設計。同步設計的第一個關鍵,也是關鍵中的關鍵,就是時鐘樹。一個糟糕的時鐘樹,對 FPGA 設計來說,是一場無法彌補的災難,是一個沒有打好地基的樓,崩潰是必然的。

具體一些的設計細則:

1)盡可能采用單一時鐘;

2)如果有多個時鐘域,一定要仔細劃分,千萬小心;

3)跨時鐘域的信號一定要做同步處理。對于控制信號,可以采用雙采樣;對于數據信號,可以采用異步 fifo. 需要注意的是,異步 fifo 不是萬能的,一個異步 fifo 也只能解決一定范圍內的頻差問題。

4)盡可能將 FPGA 內部的 PLL、DLL 利用起來,這會給你的設計帶來大量的好處。

5)對于特殊的 IO 接口,需要仔細計算 Tsu、Tco、Th,并利用 PLL、DLL、DDIO、管腳可設置的 delay 等多種工具來實現。簡單對管腳進行 Tsu、Tco、Th 的約束往往是不行的。

可能說的不是很確切。這里的時鐘樹實際上泛指時鐘方案,主要是時鐘域和 PLL 等的規劃,一般情況下不牽扯到走線時延的詳細計算(一般都走全局時鐘網絡和局部時鐘網絡,時延固定),和 ASIC 中的時鐘樹不一樣。對于 ASIC,就必須對時鐘網絡的設計、布線、時延計算進行仔細的分析計算才行。

FPGA 設計要點之二:FSM

FSM:有限狀態機。這個可以說是邏輯設計的基礎。幾乎稍微大一點的邏輯設計,幾乎都能看得到 FSM.FSM 分為 moore 型和 merly 型,moore 型的狀態遷移和變量無關,merly 型則有關。實際使用中大部分都采用 merly 型。

FSM 通常有 2 種寫法:單進程、雙進程。

初學者往往喜歡單進程寫法,格式如下:

always @( posedge clk or posedge rst )

begin

if ( rst == 1'b1 )

FSM_status <= ……;

else

case( FSM_status )

……;

endcase

end

簡單的說,單進程 FSM 就是把所有的同步、異步處理都放入一個 always 中。

優點:

1)看起來比較簡單明了,寫起來也不用在每個 case 分支或者 if 分支中寫全對各個信號和狀態信號的處理。也可以簡單在其中加入一些計數器進行計數處理。

2)所有的輸出信號都已經是經過 D 觸發器鎖存了。

缺點:

1)優化效果不佳。由于同步、異步放在一起,編譯器一般對異步邏輯的優化效果最好。單進程 FSM 把同步、異步混雜在一起的結果就是導致編譯器優化效果差,往往導致邏輯速度慢、資源消耗多。

2)某些時候需要更快的信號輸出,不必經過 D 觸發器鎖存,這時單進程 FSM 的處理就比較麻煩了。

雙進程 FSM,格式如下:

always @( posedge clk or posedge rst )

begin

if ( rst == 1'b1 )

FSM_status_current <= …;

else

FSM_status_current <= FSM_status_next;

always @(*)

begin

case ( FSM_status_current )

FSM_status_next = ……;

endcase

end

從上面可以看到,同步處理和異步處理分別放到 2 個 always 中。其中 FSM 狀態變量也采用 2 個來進行控制。雙進程 FSM 的原理我這里就不多說了,在很多邏輯設計書中都有介紹。這里描述起來太費勁。

優點:

1)編譯器優化效果明顯,可以得到很理想的速度和資源占用率。

2)所有的輸出信號(除了 FSM_status_current)都是組合輸出的,比單進程 FSM 快

缺點:

1)所有的輸出信號(除了 FSM_status_current)都是組合輸出的,在某些場合需要額外寫代碼來進行鎖存。

2)在異步處理的 always 中,所有的 if、case 分支必須把所有的輸出信號都賦值,而且不能出現在 FSM 中的輸出信號回送賦值給本 FSM 中的其他信號的情況,否則會出現 latch.

latch 會導致如下問題:

1)功能仿真結果和后仿不符;

2)出現無法測試的邏輯;

3)邏輯工作不穩定,特別是 latch 部分對毛刺異常敏感;

4)某些及其特殊的情況下,如果出現正反饋,可能會導致災難性的后果。

這不是恐嚇也不是開玩笑,我就親眼見過一個小伙把他做的邏輯加載上去后,整個 FPGA 給炸飛了。后來懷疑可能是出現正反饋導致高頻振蕩,最后導致芯片過熱炸掉(這個 FPGA 芯片沒有安裝散熱片)。

FPGA 設計要點之三:latch

首先回答一下:

1)stateCAD 沒有用過,不過我感覺用這個東東在構建大的系統的時候似乎不是很方便。也許用 systemC 或者 system Verilog 更好一些。

2)同步、異步的叫法是我所在公司的習慣叫法,不太對,不過已經習慣了,呵呵。

這次講一下 latch.

latch 的危害已經說過了,這里不再多說,關鍵講一下如何避免。

1)在組合邏輯進程中,if 語句一定要有 else!并且所有的信號都要在 if 的所有分支中被賦值。

always @( * ) begin

if ( sig_a == 1'b1 ) sig_b = sig_c;

end

這個是絕對會產生 latch 的。

正確的應該是

always @( * ) begin

if ( sig_a == 1'b1 ) sig_b = sig_c;

else sig_b = sig_d;

end

另外需要注意,下面也會產生 latch. 也就是說在組合邏輯進程中不能出現自己賦值給自己或者間接出現自己賦值給自己的情況。

always @( * ) begin

if ( rst == 1'b1 ) counter = 32'h00000000;

else counter = counter + 1;

end

但如果是時序邏輯進程,則不存在該問題。

2)case 語句的 default 一定不能少!

原因和 if 語句相同,這里不再多說了。需要提醒的是,在時序邏輯進程中,default 語句也一定要加上,這是一個很好的習慣。

3)組合邏輯進程敏感變量不能少也不能多。這個問題倒不是太大,verilog2001 語法中可以直接用 * 搞定了。順便提一句,latch 有弊就一定有利。在 FPGA 的 LE 中,總存在一個 latch 和一個 D 觸發器,在支持 DDR 的 IOE(IOB)中也存在著一個 latch 來實現 DDIO. 不過在我們平時的設計中,對 latch 還是要盡可能的敬而遠之。

FPGA 設計要點之四:邏輯仿真

仿真是 FPGA 設計中必不可少的一步。沒有仿真,就沒有一切。仿真是一個單調而繁瑣的工作,很容易讓人產生放棄或者偷工減料的念頭。這時一定要挺住!仿真分為單元仿真、集成仿真、系統仿真。單元仿真:針對每一個最小基本模塊的仿真。單元仿真要求代碼行覆蓋率、條件分支覆蓋率、表達式覆蓋率必須達到 100%!這三種覆蓋率都可以通過 MODELSIM 來查看,不過需要在編譯該模塊時要在 Compile option 中設置好。集成仿真:將多個大模塊合在一起進行仿真。覆蓋率要求盡量高。系統仿真:將整個硬件系統合在一起進行仿真。此時整個仿真平臺包含了邏輯周邊芯片接口的仿真模型,以及 BFM、Testbench 等。系統仿真需要根據被仿真邏輯的功能、性能需求仔細設計仿真測試例和仿真測試平臺。系統仿真是邏輯設計的一個大分支,是一門需要專門學習的學科。

責任編輯:lq

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602034 -

cpu

+關注

關注

68文章

10829瀏覽量

211193 -

D觸發器

+關注

關注

3文章

164瀏覽量

47867

原文標題:FPGA設計要點

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADS4128的輸出時鐘CLKOUTP,是否可以不用,而采用FPGA自己產生的一個時鐘?

FPGA如何消除時鐘抖動

時鐘樹的圖好像是APB的時鐘都是AHB給的,請問這些時鐘為多少是哪兒配的呢?是sysinit里嗎?

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

FPGA時鐘內部設計方案

FPGA設計要點之一:時鐘樹

FPGA設計要點之一:時鐘樹

評論