合成孔徑雷達(SAR)經歷了從光學記錄成像到數字記錄成像,從低分辨率到高分辨率,從單通道、單極化到多通道、多極化,從單頻到多頻的發展過程。SAR系統的迅速發展,使SAR的數據量也急劇增多,普通的存儲器已經無法滿足SAR系統對大容量、高速數據存儲的要求。

常規的數據記錄器的設計思路是通過高速PCI接口,采用SCSI總線處理器將高速數字信號存入SCSI硬盤。其缺點是數據傳輸的速率受PCI帶寬的限制,而且PCI接口對微機系統的依賴性,使系統的模塊化設計變得非常困難。另外,SAR對數據記錄器的可靠性和工作環境的要求也非常高,使SAR數據記錄器不能按照常規的方法設計。通過對SAR系統的研究,基于模塊化設計的思想,開發了一種基于FAS466的高速實時數據記錄器。其特點是采用高速DMA接口、可脫離微機平臺工作、體積小、可靠性高,實際持續存儲速度達到72MB/s。

1 SCSI總線和硬盤

SCSI是美國ANSI9.2委員會定義的計算機和外設之間的接口標準。本系統采用SCSI硬盤,因為5CSI接口比常見的IDE接口具有更多優點:(1)SCSI提供了一個高速傳輸通道,傳輸速度更快;(2)SCSI接口采用總線主控數據傳輸(Bus Master Data Transfer),占用CPU資源少;(3)可同時串接多臺不同類型的設備;(4)SCSI硬盤在標識硬盤扇區時使用了線性的概念,即硬盤只有順序的第1扇區、第2扇區…第n扇區,不像IDE硬盤的“柱面/磁頭/扇區”三維格式。這種線性編排方式訪問延時最小,可加快硬盤存取速率,尤其在持續大容量控據存儲時,所顯現的優勢更為明顯。

2 系統的硬件結構設計

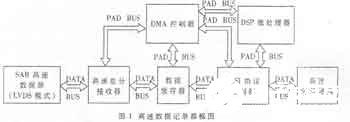

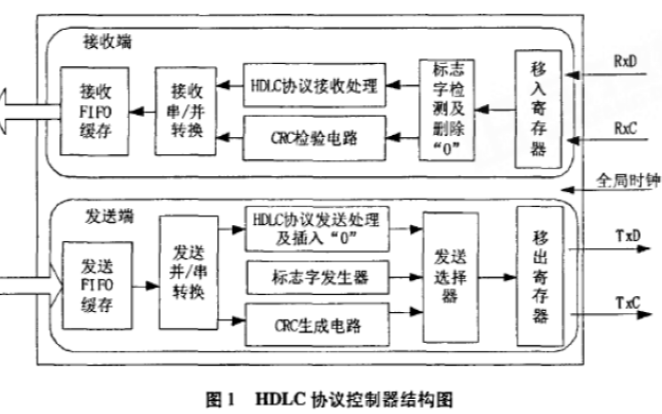

整個系統的設計總體框圖如圖1所示,包括高速數據源、高速差分接收器、DMA控制器、數據緩存器、DSP微處理器、SCSI協議控制器和高速SCSI硬盤等子系統;下面分別給出各子系統的設計(PAD BUS表示控制信號線,DATA BUS表示數據信號線)。

2.1 高速數據源和高速差分線性接收器

系統的高速數據源接口為16位的并行接口,數據傳輸接口的所有信號均采用低電壓差分模式LVDS傳輸,信號進入記錄器之后要將LVDS電平轉換成TTL電平。

2.2 數據緩存器

數據緩存的目的是為SCSI的高速DMA傳輸做好準備,使兩邊數據傳輸速度匹配。數據的流向一般是一個口進,一個口出,不對信號進行任何處理。雙口隨機存儲器RAM雖然也可完成這個任務,但是由于它需要復雜的地址譯碼電路,所以不采用,而采用FIFO。由于SAR系統每幀數據小于8KB,本系統選用的FIFO深度為8KB。

2.3 SCSI協議控制器--FAS466

FAS466(Fast Architecture SCSI Processor)處理器是Qlogic公司1999年上市的一種高性能SCSI引擎,它源于Qlogic公司的TEC450/452三重嵌入式控制鋁系列,可提供Ultra2 SCSI的同步傳輸速率,支持先進的SCSl自動配置模式的1層和2層協議,內部嵌有微控制器,能夠通過編程方式靈活地協調SCSI作業隊列,可以工作在啟動或目標模式并支持單端或低電壓差分模式的SCSI連接。

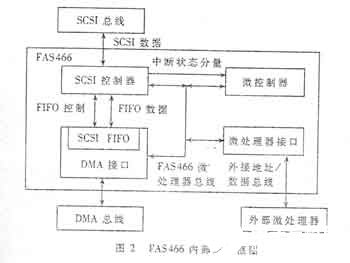

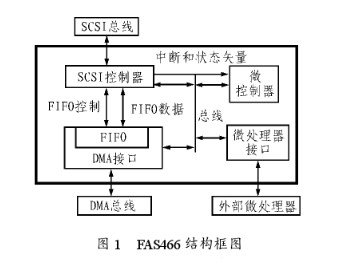

FAS466區別于其它SCSI協議控制器的最大特點是它采用微處理器和DMA接口結構,而常見的SCSI協議控制器采用PCI接口總線結構。這是本設計采用FAS466的一個主要原因。采用微處理器和DMA接口結構,可以通過DSP對傳輸進行控制,脫離微機平臺,減少傳輸帶寬限制,使數據記錄器具有非常好的靈活性和可移植性。 FAS466由SCSI控制器、微控制器、DMA接口和微處理器接口四個模塊組成。外部微處理器通過微處理器接口對FAS466進行控制,SCSI控制器提供靈活、有效的底層SCSI協議控制,微控制器負責控制數據從DMA接口到SCSI硬盤的傳輸以及各個模塊之間的協調。圖2為FAS466的內部結構。

2.4 OMA控制器

本設計采用DMA接口代替高速數據存儲中常見的PCI接口。這不但使傳輸數據的速率有了比較明顯的提高,而且使數據記錄器可以脫離微機系統,使模塊化設計成為現實。

本設計采用CPLD器件實現DMA控制器,而不采用專用的DMA控制器,主要考慮以下一些因素:本設計的數據傳輸速率達到72Mg/s,一般的專用DMA控制器難以勝任;專用的DMA控制器與FAS466之間的連接需要大量的邏輯轉換電路和外圍連線,使設計難度加大;DMA控制器還需要在DSP的控制下與FAS466進行協調才能一起工作,這增加了軟件編程的難度;使用CPLD器件,除了完成DMA控制器的功能之外,還可以把電路中的譯碼、邏輯轉換、系統復位等模塊設計進去,減小了設備的體積,方便了以后對系統的升級和改進。

2.5 DSP微處理器

該高速數據記錄器選用TI公司的TMS320F206作為微處理器。主要考慮TMS320F206片內包含32K×l6字的FLASH EEPROM,使DSP周圍電路簡單、設備的體積減小,而且系統升級也比較方便;指令集非常豐富,與TMS320C5X系列指令兼容;TMS320F206的指令周期為50ns,符合系統對DSP速度的要求。

DSP負責對各個模塊進行協調和控制,實現高速數據記錄的功能。需要注意的是:FAS466的微處理器接口數據/地址總線是復用的,而TMS320F206的數據/地址總線是分開的,需要外部邏輯將數據和信號總線整合。高速數據通過信號源接口進入本系統,首先進行電平轉換,然后進入數據緩存器;在DMA控制器的控制下進入SCSI協議控制器;最后通過SCSI協議控制器存入高速SCSI硬盤。整個數據流程中,DSP微處理器負責各個子系統之間的協調和控制。由于采用分離的微處理器總線和DMA總線結構,因此達到了較高的記錄速度。

3 系統的軟件設計

軟件模塊的設計是本系統設計的重點和難點,它負責對相關硬件控制和協調,最終實現SCSI協議、硬盤的控制和DMA傳輸等。本系統中,軟件設計分為DSP控制軟件和DMA控制器的CPLD實現兩部分。程序的優劣關系到整個系統數據存儲的速度,下面分別討論。

3.1 DSP控制軟件

一般來說.要完成一次數據交換必須完成SCSI總線的仲裁、選擇、消息、命令、數據和狀態等階段。這些階段,微處理器TMS320F206通過對FAS466寄存器的讀寫控制完成實現。FAS466的寄存器主要有:

(1)命令寄存器(Command Register):F206通過向命令寄存器寫入相應指令,控制FAS466完成初始化、復位、總線分配與復位以及SCSI總線各個階段的轉變等功能;(2)FIFO寄存器(FIFO Register):這是一個16字深的FIFO寄存器,SCSI硬盤和FAS466之間的數據交換都通過這個FIFO完成;(3)傳輸計數寄存器(Transfer Count Register):是一個減法計數器,用于保存一次DMA數據傳輸的字節數;(4)中斷寄存器(Interrupt Registet):F206通過FAS466中斷寄存器了解SCSI命令的執行情況,從而決定程序的執行流向。

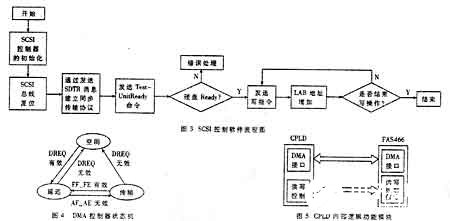

SCSI控制軟件流程如圖3所示。首先初始化SCSI控制器,然后SCSI控制器與SCSI硬盤建立同步傳輸協議,在硬盤準備好的情況下才可以發送各種SCSI命令,如讀、寫等,同時處理好各種意外情況的發生。

3.2 DMA控制器的CPLD實現設計

FAS466外部DMA控制器由CPLD實現。FAS466通過DREQ信號有效請求數據傳輸;DMA控制器檢測到DREQ有效并且外部FIFO非空,則使DACK有效并通知FAS466開始DMA傳輸。控制器的狀態機如圖4所示。CPLD除了實現FAS466的外部DMA控制器之外,還實現FAS466與外部微處理器的部分邏輯和其它邏輯控制。CPLD內部邏輯功能模塊如圖5所示。

本文介紹了一種基于高性能SCSI總線處理器FAS466的專用高速SAR數據存儲設備的設計。本設備可以脫離微機平臺將SAR數據實時高速記錄到SCSI硬盤。數據傳輸采用高速DMA接口,實現了模塊化設計,可移植性好,可以靈活地應用在各種系統中。

責任編輯:gt

-

控制器

+關注

關注

112文章

16206瀏覽量

177423 -

接收器

+關注

關注

14文章

2458瀏覽量

71800 -

微處理器

+關注

關注

11文章

2247瀏覽量

82322

發布評論請先 登錄

相關推薦

符合Ultra2的高性能SCSI處理器FAS466

基于FAS466存儲系統的DMA控制器設計

基于FAS466的CCD相機數字視頻實時存儲系統設計

SCSI控制器進入復位狀態時的注意事項

如何使用FPGA實現HDLC協議控制器

基于SCSI協議控制器FAS466實現專用高速SAR數據存儲設備的設計

基于SCSI協議控制器FAS466實現專用高速SAR數據存儲設備的設計

評論