對于10Gbps及以上數據速率的SerDes,每個數據位的單位間隔是隨著近 20~30ps的信號上升/下降時間而縮短的。選擇合適的封裝互連結構,有效地傳輸這些信號已成為最大限度減少信號完整性問題的重要考慮因素,如串擾、阻抗不連續性等。對于低成本應用,鍵合線封裝是替代相對高端的倒裝芯片封裝的首選方案,但它缺乏執行大I/O數、控制阻抗及為芯片提供有效電源的設計靈活性。

本文將討論通過優化封裝內的阻抗不連續性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規范。

差分阻抗

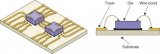

一個典型的SerDes通道包含使用兩個單獨互連結構的互補信號發射器和接收器之間的信息交換。兩個端點之間的物理層包括一個連接到子卡的鍵合線封裝或倒裝芯片封裝的發射器件。子卡通過一個連接器插在背板上。背板上的路由通過插入的子卡連接到一個或一組連接器。采用鍵合線或倒裝芯片封裝的接收芯片也位于這些子卡上。

如果設計不合適,一個通道中的這些多重轉換將會影響信號完整性性能。在10Gbps及以上,通過最大限度地減少阻抗不連續性,得到適合的互連設計已成為提高系統性能的一個重要的考慮因素。由于封裝內有許多不連續區,該收發器封裝在提高回波損耗性能方面存在一個重要瓶頸。

SerDes通道設計通常為100Ω差分阻抗。由于差分信號采用奇模傳播,差分對的每線奇模阻抗都必須是50Ω。差分對的每線信號都需要有50Ω的恒阻抗,以盡量減少回波損耗,最大限度地提高性能。

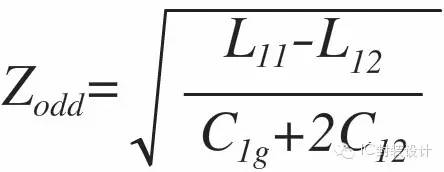

損耗較少的系統的奇模阻抗定義為:

為了優化每線阻抗,所有四個分量都需要平衡,以達到50Ω阻抗。對于差分對,在每一個單端信號傳送一對信號,L12和C12分量都不存在,Zodd是自L/C的平方根。

一次預處理封裝

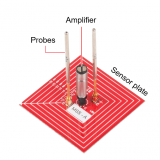

有三個差分對的典型的鍵合線封裝的截面如圖1所示。發射器對以藍色顯示,居中的接收器對為紅色。該封裝基板是一個傳統的4層基板,頂層有微帶印制線,第二層和第三層是電源/接地,焊球在最后一層。這個一次預處理設計的優化可以滿足基頻數據速率下-15dB和一次諧波頻率數據速率下-10dB的回波損耗規范。

圖1 一次預處理封裝

一個典型的鍵合線封裝可以分成三個阻抗區;主要是感應鍵合線區、印制線路由傳輸線區和電容焊球/通孔區。

單端和差分TDR響應

時域反射計(TDR)技術用來監控從芯片到PCB的信號遇到的阻抗。圖2顯示了作為一個單端信號,也可作為一個差分信號驅動的差分對中的每線TDR響應。圖1中只有一個對用于TDR分析,而其他對接地,忽略串擾對TDR響應的影響。

單端TDR曲線顯示了主要電感、后面跟著一小段傳輸線的高阻抗鍵合線區互連結構,其后面是電容、低阻抗通孔和焊球區。由于在差分對鍵合線區有強大的相互感耦合,當相同的結構進行差分驅動時,電感鍵合線尖峰不太明顯。由于差分設置的互電容增加了一倍,電容dip顯著惡化。消除來自通孔/焊球區的額外電容是實現100Ω 差分阻抗的關鍵。圖2 還顯示了焊點區的電場(E-field)曲線,以及集中在焊點上的強電場。

圖2 單端和差分TDR曲線

提高TDR 性能

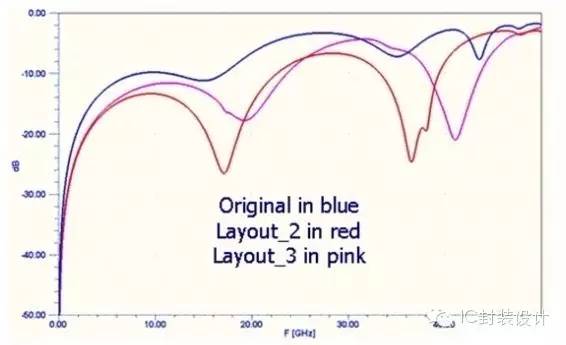

圖3顯示了原來布局的變化(在焊點/通孔區)及其對差分TDR性能的影響。這些略大于焊點的孔是在焊點上的金屬層Layout_2上實現的。原有布局的電容dip現在大約小到20Ω。另一個來自Layout_2的試圖修改的部分是從松散耦合到緊耦合來改變通孔定位,如Layout_3所示。緊耦合通孔旨在提高差分對的串擾性能。它已在另一項研究中得到證明,串擾性能的改善微乎其微,這里不介紹這項研究的其他內容。Layout_3的粉色波形顯示,由于額外兩個通孔之間的電容耦合,電容dip略差。

圖3 三種布局的差分TDR響應

回波損耗性能的影響

圖4顯示了每次修改后回波損耗性能的影響。Layout_3原始布局的整體回波損耗最差。Layout_2 顯示出最佳的整體回波損耗,它直接關系到其TDR性能。

在5GHz下Layout_2的回波損耗為-16dB,而在10GHz下為-14dB,可以輕易滿足基頻為-15dB的規范,以及10Gbps SerDes接口一次諧波頻率-10dB的規范。

圖4 每次修改后回波損耗性能的影響

芯片焊點環布局的影響

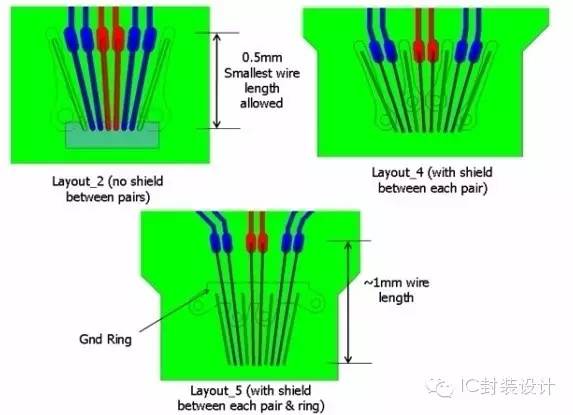

為了盡量減少對間串擾,理想的是用回波焊點隔開芯片上的每個差分對。當邊緣速率在20-30ps級時,由于干擾源-受擾者串擾,可能嚴重惡化接收器性能,這一點至關重要。要保持通孔和焊球焊點區與Layout_2一致,圖5給出了與芯片封裝鍵合線連接相關的兩個額外的封裝布局變化。

圖5 片芯焊點環和鍵合線布局變化

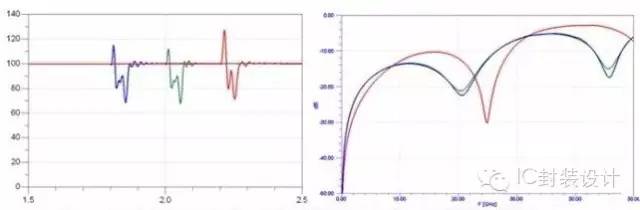

圖6顯示了三個布局的差分TDR和回波損耗性能。藍色的Layout_2響應與前邊的圖一樣。由于相對較小的間斷電感,但其頻域影響不變,Layout_4的TDR性能稍好。Layout_5 TDR響應顯示,由于相對于其他兩個布局的鍵合線,感應尖峰幾乎為2倍。圖6也顯示了長鍵合線對回波損耗性能惡化的直接影響。

圖6 由于 片芯焊點環和鍵合線布局的改變影響了TDR和回波損耗性能

本文小結

本文解釋了鍵合線封裝中的兩個主要不連續區;討論了10Gbps數據速率范圍優化鍵合線封裝布局的快速技術;也顯示了鍵合線長度對回波損耗性能惡化的影響。

責任編輯:lq

-

芯片

+關注

關注

453文章

50410瀏覽量

421849 -

連接器

+關注

關注

98文章

14318瀏覽量

136165 -

封裝

+關注

關注

126文章

7784瀏覽量

142725

原文標題:SI-list【中國】10G SerDes 封裝優化

文章出處:【微信號:si-list,微信公眾號:高頻高速研究中心】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用電容測試方法開創鍵合線檢測新天地

半導體制造的鍵合線檢測解決方案

金絲鍵合工藝溫度研究:揭秘鍵合質量的奧秘!

TUSB1002 USB3.1 10Gbps雙通道線性轉接驅動器數據表

10Gbps SerDes鍵合線封裝規范

10Gbps SerDes鍵合線封裝規范

評論