很多情況下,拍攝的視頻會有不盡人意的地方,這就需要對視頻進行視頻處理(即幀圖像處理)以達到所期望的效果。視頻處理是一個龐大繁瑣又耗時的工程,尋常視頻處理都是在PC機上采用CPU+GPU的異構計算來進行;FPGA的出現及其高效的并行運算性能,使得CPU+FPGA的異構計算更加適合進行高強度的批處理運算,zynq系列兼具處理系統和可編程邏輯的SoC片上系統也使得使用FPGA進行視頻處理這類運算需求量大的工程時更加得心應手。

進行幀圖像處理設計隨著客戶需求的提高變得越來越復雜,復雜的設計變得越來越難以調試:在何處設置探針,重復進行編譯,放置和布線,查看,重置探針,一遍又一遍。調試中重復過程花費時間過多,很少有時間調試根本原因。

虹科FPGA調試工具--VSTAR

此處我們展示虹科FPGA調試工具在視頻處理設計中進行調試并大幅縮短調試周期的案例。 我們對視頻的幀圖像處理采用復雜程度中等的圖像旋轉算法,期望達到視頻某片段旋轉縮小至消失并鏈接下一視頻片段的效果。 圖像旋轉算法映射到具有300 MHz AXI流和200 MHz AXI總線的Xilinx Kintex-7 FPGA K705開發板上。

視頻處理流程框圖

在設計中向圖像旋轉算法人為的注入會造成工程出現預期之外的邏輯錯誤,但可以正確通過編譯、布局布線、綜合和仿真。在VSTAR GUI 中打開該設計,注入VSTAR的驗證IP并選定clk時間信號。

根據設計以及調試需要,選擇了三組總線探針進行監測,VSTAR會根據選定的探針自動生成設計規則,當然如果發現自動設計的規則不太合適也可以自己手動進行設計規則的設定。

下載好bit流文件并運行后,VSTAR開始自動檢測所選探針的錯誤情況,如果監測到設計規則之外的,并顯示故障,通過GTKWave上的VCD向用戶顯示。

VSTAR用于圖像旋轉器有效信號的探針設置

VSTAR為圖像旋轉器的有效信號自動生成的規則之一

由下圖監測結果可以看出,正常運轉時,所監測的探針信號符合設計規則,但當達到人為設計的錯誤觸發條件以后,圖像旋轉器出現信號跳轉錯誤,違背了設計規則,由于設定錯誤緩存區為1次,所以此次出現錯誤后會直接結束監測,并展示VSTAR IP Status狀態窗口,顯示具體錯誤描述。

可根據出現錯誤的信號以及錯誤發生的時間去專向分析產生錯誤的原因,從而大幅縮短調試周期。

監測結果

責任編輯:xj

原文標題:虹科VSTAR縮短FPGA視頻處理調試周期

文章出處:【微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

-

視頻處理

+關注

關注

2文章

98瀏覽量

18804 -

FGPA

+關注

關注

1文章

24瀏覽量

16003 -

虹科電子

+關注

關注

0文章

595瀏覽量

14279

原文標題:虹科VSTAR縮短FPGA視頻處理調試周期

文章出處:【微信號:HK-FPGA_Dep,微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

虹科方案 領航智能交通革新:虹科PEAK智行定位車控系統Demo版亮相

更強的無線(雙)串口數據記錄 調試工具

這個調試工具咋賣39.9?分析了原理后,我悟了

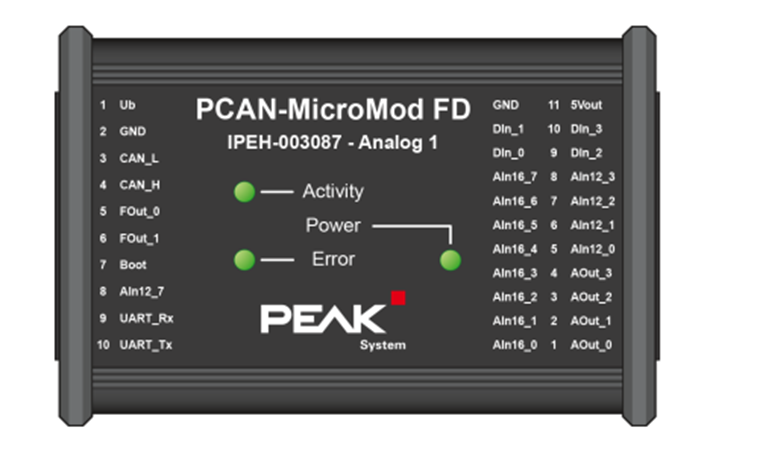

虹科案例|為什么PCAN MicroMod FD是數模信號轉換的首選方案?

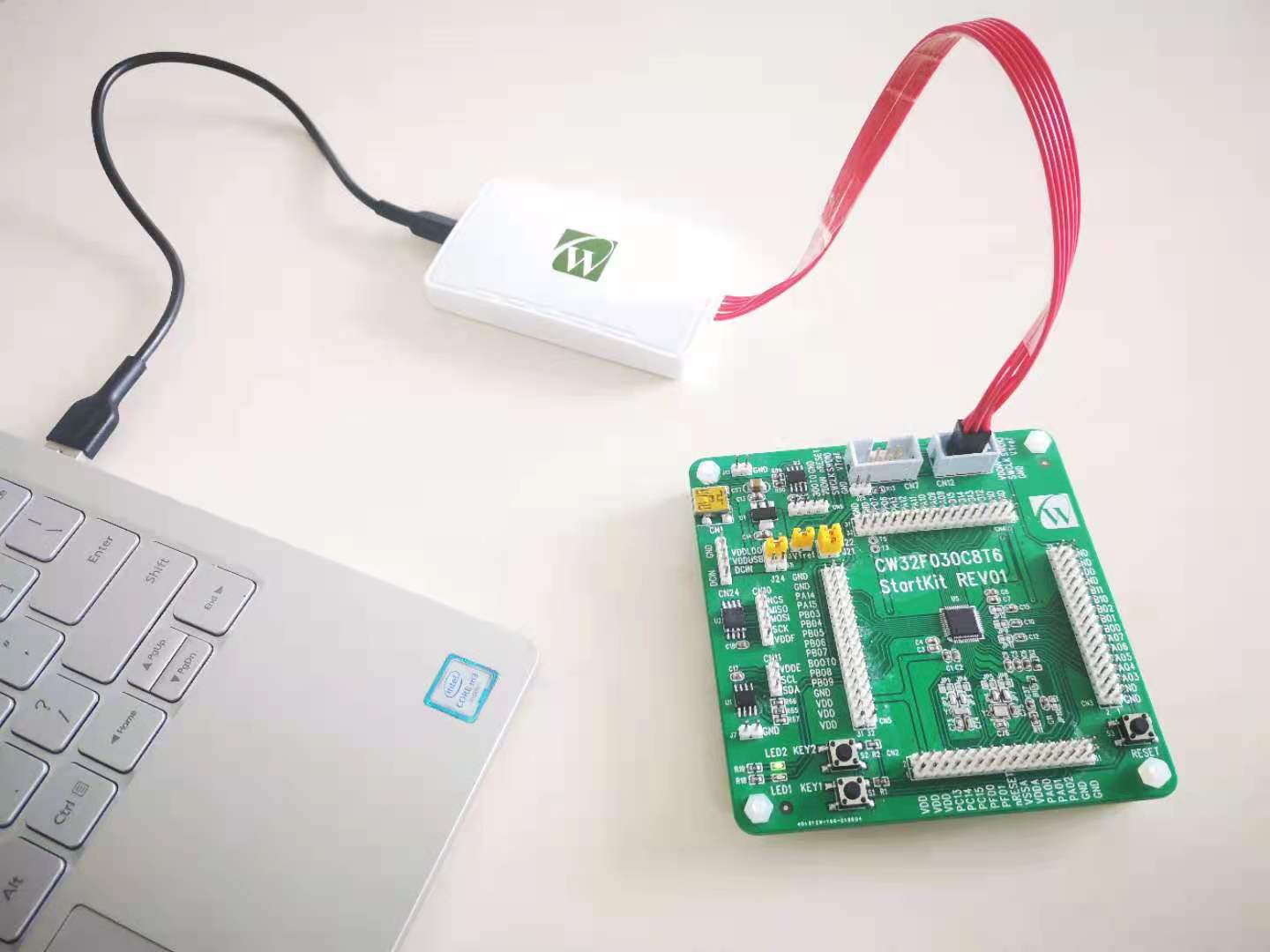

CW-DAPLINK調試工具

虹科FPGA調試工具:VSTAR

虹科FPGA調試工具:VSTAR

評論