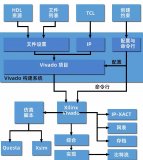

創建 FPGA 設計和維護 Vivado 設計套件項目時,版本控制系統對于團隊合作可能是一項具有挑戰性的任務。工程師必須能跟蹤設計變更,完整地從 HDL 或 TCL 源代碼再現項目并交付特定的項目狀態。Vivado 工具非常適用于這類工作,因為該工具能夠為項目生成存檔文件或創建 TCL 文件,從而再現項目狀態。

然而,上述機制需要一定數量的手動操作,而且在 Vivado 設計套件項目外對設計的參數進行設置,也存在不夠靈活的問題。因此,為了簡化上述操作,我們已經開發出對應腳本。其思路是在提供項目的 HDL 和 TCL 源文件的同時,提供從頭創建 Vivado 設計套件項目所需的其他配置文件。設計構建腳本的目的是幫助用戶在單獨的 Vivado 設計套件項目下開發獨立的項目組成部分(特色),且能夠以其他配置方式對項目不同組成部分的源文件進行組合。此外,構建腳本也可用于創建目標構建工件,例如 IP XACTIPXACT 封裝、仿真、綜合、實現和比特流生成。

與此同時,MLE 也面向 PetaLinux 和賽靈思軟件開發套件 (XSDK) 發布了一套易用型 Makefiles,并將為 Vitis 統一軟件平臺提供后續支持。這些處理系統 Makefiles(或簡稱為 PSMake)還提供在 GitHub 上。

為了加快實現 FPGA 構建環境的自動化(如用于持續集成 (CI)),并確保在開發與生命周期后期階段完整重現設計結果,Missing Link Electronics 團隊已整合出一套腳本。目前,這套腳本化 FPGA 構建環境主要面向賽靈思 Vivado 工具(版本 2016.4 或更新版本),并在 Ubuntu Linux 16.04 LTS 和 18.04 LTS 下通過測試,已通過 Apache 2.0 開源許可證提供在 GitHub 上。

責任編輯:lq

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601866 -

控制系統

+關注

關注

41文章

6546瀏覽量

110485 -

自動化

+關注

關注

29文章

5514瀏覽量

79108

原文標題:如何實現 FPGA 構建環境的自動化

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TI RF Transceiver EVM自動化環境搭建方法

開關電源自動化測試設備:如何實現自動化測試?

機械自動化和電氣自動化區別是什么

機械自動化是自動化的一種嗎

如何實現PLC的自動化控制邏輯

機械制造與自動化是自動化類嗎

工業自動化和自動化區別是什么

工廠自動化控制的典型實現方式

自動化構建環境在FPGA設計中的應用

電源測試怎么自動化?電源模塊自動化測試系統如何實現?

如何實現FPGA構建環境的自動化

如何實現FPGA構建環境的自動化

評論