本文將聚焦“低壓降”的含義,并介紹安森美半導體低壓降和極低壓降值的LDO產品和方案。您的應用需要低壓降的LDO嗎?我們將講解壓降的含義,如何測量以及具有標準壓降和極低壓降的LDO之間的差異。

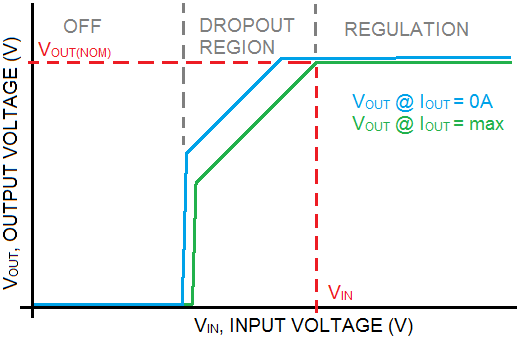

LDO必須具有比壓降參數更高的裕量VIN–VOUT。壓降是LDO正常運行的最關鍵參數之一。壓降是LDO需要適當調節的VDO=VIN–VOUT,NOM的差。VOUT,NOM是LDO處于穩壓狀態時在輸出端的輸出電壓標稱值。

壓降值通常在VOUT低于標稱值(約3%)或100mV時測量。當VOUT下降時,如約100mV,很容易測量該值。通常針對標稱輸出電流測量壓降參數,因為壓降是在VOUT下降(比VOUT,NOM低約3%)時測量的。

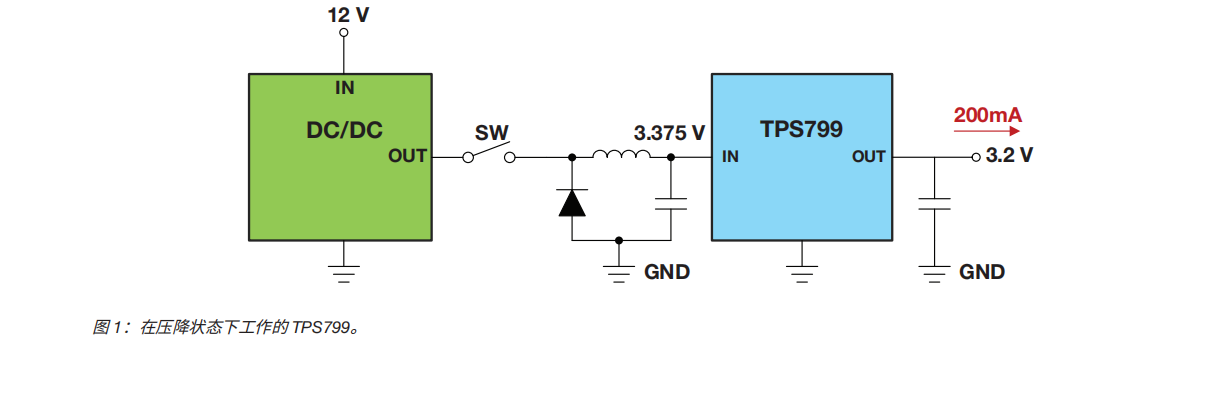

因此,必須在灌電流模式下將輸出連接到電流源,例如,將有源負載連到恒定灌電流。如果電阻連接到輸出,則負載輸出電流將減小,并且測量無效,請參見下圖。

圖1(壓降區域和穩壓區域)

圖2(壓降值的測量)

LDO應該在VIN和VOUT之間有一個電壓差,并具有較高的VDO壓降值,以實現好的動態性能。

大多數LDO有導通器件P溝道MOSFET(PMOS),這對于較低的輸出電壓來說有點不利。當標稱輸出電壓VOUT,NOM較低時,帶PMOS導通器件的LDO的壓降VDO會增加。

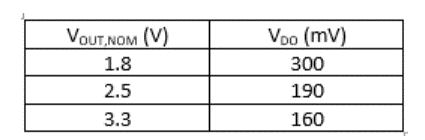

舉例來說,請看下表,假設我們正在使用NCP161。您可以看到1.8V選項的壓降值遠高于3.3V選項。

PMOS器件LDO有缺點,因為它們具有相當高的最小輸入電壓VIN,MIN。NCP110也是PMOS器件LDO,VIN超低。VIN,MIN=1.1V。NCP110的最低輸出電壓選項0.6V的壓降值為500mV。

如果要求非常低的壓降或接近0V的輸出電壓選項,則可以使用偏置軌LDO。這種LDO有導通器件N溝道MOSFET(NMOS),它需要連接比VOUT高約1V–2V的輔助電源VBIAS,以實現極低的壓降。

偏置軌LDO與普通LDO的結構相同,但內部模塊(除導通器件的所有器件)的電源未連接至VIN。它單獨作為次級電源。

這些器件的一些示例是NCP130、NCP134、NCP137和NCP139。與帶PMOS導通器件的LDO相比,帶NMOS導通器件的LDO具有幾乎不受輸出電壓影響的壓降。

這些器件在額定輸出電流下的VDO壓降值在40mV?150mV范圍內。但是必須如上所述連接VBIAS電壓,否則由于伏特單位,壓降會高得多。

在下圖中,您可以看到當VBIAS-VOUT差減小時,NCP134的壓降會怎樣,這樣,VBIAS電壓不夠高。

圖3(NCP134的壓降取決于VBIAS-VOUT)

也可以使LDO帶導通器件NMOS但不提供VBIAS電源。有一個電荷泵用于為內部模塊供電。電荷泵器件從VIN電源產生高兩倍的內部VBIAS電壓。

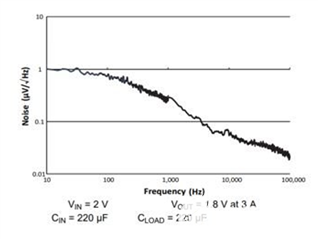

圖4(NCP134和NCP161的壓降差)

在圖4中,您可看到帶PMOS導通器件的LDO和帶NMOS導通器件的LDO的壓降差。帶PMOS導通器件的LDO通常在零輸出電流時具有非零壓降值。LDO壓降的這一部分是內部參考電壓的壓降。

第二部分是通過導通器件的尺寸設置的壓降。帶NMOS導通器件的LDO具有由VBIAS電壓提供的內部基準。因此,它沒有第一部分。帶NMOS導通器件的LDO壓降僅通過導通器件的尺寸設置。

責任編輯人:CC

-

ldo

+關注

關注

35文章

1917瀏覽量

153164 -

LDO穩壓器

+關注

關注

0文章

139瀏覽量

16692 -

壓降分析

+關注

關注

0文章

2瀏覽量

7175

發布評論請先 登錄

相關推薦

一文詳解低壓降穩壓器(LDO)

什么是LDO噪聲呢?低壓降(LDO)穩壓器原理

談談LED導通壓降

什么低壓降(LDO)穩壓器?

LDFMPT-TR,是一種快速,極低壓降線性穩壓器

Diodes全新低壓降線性穩壓器(LDO)提升系統穩定性及瞬

電源芯片選擇什么好?什么是 LDO(低壓降)穩壓器?

什么是低壓降穩壓器(LDO)的壓降? - 第五部分

如何測量LDO標準壓降和極低壓降之間的差異

如何測量LDO標準壓降和極低壓降之間的差異

評論