1 引 言

DDS(Direct Digital Frequency Synthesis,直接數(shù)字頻率合成器)是一種從相位概念出發(fā)直接合成所需波形的頻率合成技術。由于DDS具有相對頻帶寬、頻率分辨率高、頻率變化速度快與相位可連續(xù)線性變化等一系列特點,已被廣泛應用于數(shù)字通信系統(tǒng)中。目前,可供用戶選擇的高性能、多功能的專用DDS芯片比較多。然而在某些對控制方式、置頻速率等方面有特殊要求的場合,設計一個基于高性能FPGA(Field Programming Gate Array,現(xiàn)場可編程門陣列)的DDS電路就是一個很好的選擇。

依據(jù)正弦波對稱性,把DDS的核心部件——相位累加器改進為回旋相位累加器,使得波形存儲ROM空間降為原來的50 %,頻率分辨率提升1倍。另外,在QuartusⅡ,VC與LabWindows/CVI組成的混合仿真環(huán)境下,對該系統(tǒng)進行驗證。這樣,既避免硬件平臺的限制,又增加了硬件實現(xiàn)成功率。

2 混合仿真下改進的DDS系統(tǒng)的實現(xiàn)

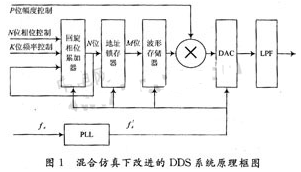

由圖1可見,改進后的DDS系統(tǒng)由回旋相位累加器、波形存儲器、DAC(Digital to Analog Converter,數(shù)模轉(zhuǎn)換器)、PLL(Phase Locked Loop,鎖相環(huán)路)與LPF(LowPass Filter,低通濾波器)構成。

2.1 DDS工作原理

在連續(xù)的時鐘作用下,相位累加器以K位頻率控制字為步進值做累加運算。把累加器的輸出作為波形存儲器的地址數(shù)據(jù),依次讀出相應單元的正弦波波形樣點數(shù)據(jù),然后送往DAC進行數(shù)模轉(zhuǎn)換后,經(jīng)LPF低通濾波后輸出連續(xù)模擬的正弦波形。

假設波形存儲器ROM中存儲了一個完整正弦波波形的樣點數(shù)據(jù),那么通過改變K位頻率控制字的大小,就調(diào)整了累加器的步進值,亦即改變了輸出的正弦波單周期樣點數(shù),從而實現(xiàn)了正弦波形的頻率控制。如每次對K位頻率控制字的累加后,再把N位相位控制字累加進去后,便可實現(xiàn)波形的相位偏移。如每次再對波形存儲器輸出數(shù)據(jù)乘以P位幅度控制字后便實現(xiàn)了正弦波形的幅度控制。

如果正弦波形的采樣深度為D位,那么系統(tǒng)內(nèi)的N位累加器就決定了波形存儲器的存儲空間應為2N×D位。如果取N為32位,D為10位,則需要5 120 MB的ROM資源,這在任何一片F(xiàn)PGA芯片中是難以實現(xiàn)的。由于波形樣點數(shù)據(jù)存在大量的重復值,因此本系統(tǒng)采用了“截尾法”來生成存儲器的地址(圖1中的地址鎖存器完成的就是這個功能)。把累加器輸出的高10位作為存儲器的地址,從而使得ROM空間縮小為1.25 kB。而依據(jù)正弦波形的對稱性把相位累加器改進為回旋相位累加器后,使得ROM只需存儲半波形數(shù)據(jù),進而把ROM空間再降低50%,變?yōu)?.625 kB。

2.2 系統(tǒng)參數(shù)的確定

系統(tǒng)預采用10位無符號的DAC,故存儲波形樣點數(shù)據(jù)的ROM空間大小為210×10位。即D為10位,M為10位。

通過系統(tǒng)的綜合仿真報告,可以發(fā)現(xiàn)系統(tǒng)的極限工作頻率為197.01 MHz。因此,為了最大限度地拓寬DDS的頻帶寬度,系統(tǒng)中引入了PLL來提升時鐘信號頻率及其穩(wěn)定度。選定fs為50 MH,f′s為190 MHz。

雖然奈奎斯特抽樣定理已經(jīng)證明,周期樣點數(shù)只要保留2個以上便可以無誤地復原波形。可是為了保證完整精確地重建正弦波形,保守地選擇單周期樣點的個數(shù)應該≥16個。而回旋相位累加器的每次溢出只表示有半個正弦波形的輸出,即頻率控制字的位數(shù)比回旋相位累加器的位數(shù)少3位。所以,頻率控制字的位數(shù)K為28位,回旋相位累加器的位數(shù)以及相位控制字的位數(shù)N為31位。

2.3 回旋相位累加器

所謂回旋相位累加器,指的是累加器先以頻率控制字為步進值進行加法運算,當累加器溢出后,再以頻率控制字為步進值進行減法運算,如再次溢出后,再進入遞增式的加法運算階段,如此循環(huán),故稱之為回旋相位累加器。回旋相位累加器實質(zhì)上仍然是以頻率控制字為步進值的累加器。他實現(xiàn)“回旋”的思想主要是依據(jù)溢出位COUT。如果COUT=‘0’,則正常輸出;如果COUT=‘1’,則取反后輸出。

由此不難得出,改進的DDS系統(tǒng)的頻率分辨率△f、相位分辨率△p以及系統(tǒng)輸出正弦波的頻率fo由式(1)、式(2)以及式(3)給定:

假設幅度控制字大小為1,則由式(1),(2),(3)可知系統(tǒng)的頻率分辨率△f約為0.044 Hz,相位分辨率△p約為8.382*10-8度,輸出正弦波的最高頻率fmax為11.875 MHz以及最低頻率fmin為0 Hz。

由此不難看到DDS的優(yōu)點:輸出信號的頻帶寬、頻率分辨率以及相位分辨率高。

3 存儲器初始化文件(*.mif文件)的生成以及對仿真數(shù)據(jù)等間隔采樣提取

波形存儲器調(diào)用LPM_ROM元件實現(xiàn)。為了得到1 024個10位正弦波的半周期無符號幅值樣點數(shù)據(jù),并生成相應的存儲器初始化文件(*.mif文件),需要把正弦波波形移至x軸上方后進行采樣。采樣公式為:

![]()

在QuartusⅡ6.0軟件中對DDS進行波形仿真后,把仿真結果保存為含有時間和對應樣點數(shù)據(jù)的*.tbl文件。然后在VC中,依據(jù)tbl文件的存儲格式,編程實現(xiàn)對時間和樣點數(shù)據(jù)的分離提取。

盡管QuartusⅡ6.0是一款十分優(yōu)秀的EDA(Elec-tronic Design Automation,電子設計自動化)開發(fā)工具,但是其仿真結果直觀性差,有必要借助第三方工具來觀察驗證仿真結果。而且可以利用第三方工具來仿真DAC以及LPF。在本系統(tǒng)中,選擇了信號處理函數(shù)庫極其豐富、可視性很強的虛擬儀器開發(fā)平臺LabWindows/CVI 8.0。

由于QuartusⅡ6.0仿真生成的tbl文件中的仿真數(shù)據(jù)在時間上并不是等間隔的,因此在LabWindows中進行濾波處理之前,必須對仿真數(shù)據(jù)進行等間隔采樣。等間隔采樣的方法是“遞進式查找法”,采樣原則是每個周期采樣512個點。

4 仿真結果與分析

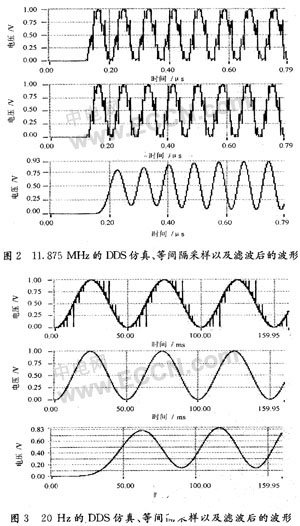

在LabWindows 8.0中使用他的高級信號分析庫中的五階切比雪夫低通濾波器函數(shù)對等間隔采樣后的樣點數(shù)據(jù)進行濾波,便可得到圖2(11.875 MHz的DDS仿真,等間隔采樣以及濾波后的波形)、圖3(20 Hz的DDS仿真,等間隔采樣以及濾波后的波形)的仿真結果。

由圖2、圖3中DDS的仿真波形中存在大量的毛刺,這主要是由于多位的波形數(shù)據(jù)傳輸?shù)紽PGA的管腳時存在微小的時間誤差造成的,屬正常現(xiàn)象。這可以通過后面的濾波電路消除,而圖中的濾波后的波形也十分理想。圖2、圖3中的電壓值只是歸一化的電壓。

5 結 語

文中詳細描述了基于QuartusⅡ6.0,VC 6.0和Lab-Windows/CVI 8.0混合仿真環(huán)境下設計并實現(xiàn)一個改進的DDS系統(tǒng)的方法和過程,這個數(shù)字系統(tǒng)設計的特點就是設計完全避免了硬件平臺的限制,同時提升了系統(tǒng)硬件實現(xiàn)的成功率。另外系統(tǒng)中回旋相位累加器的引入把ROM空間的開銷降低50%,分辨率提升1倍。

但是,由于DDS內(nèi)部的波形存儲器ROM工作速度的限制,使得DDS輸出的最高頻率有限。而DDS的全數(shù)字結構也不可避免地引入了雜散,主要來源有:回旋相位累加器的截尾誤差造成的雜散、幅度量化誤差造成的雜散和DAC非理想特性造成的雜散。但是,通過濾波處理完全可以把這些雜散對波形的影響降到最低。

責任編輯:gt

-

存儲器

+關注

關注

38文章

7452瀏覽量

163606 -

頻率合成器

+關注

關注

5文章

218瀏覽量

32331 -

DDS

+關注

關注

21文章

631瀏覽量

152542

發(fā)布評論請先 登錄

相關推薦

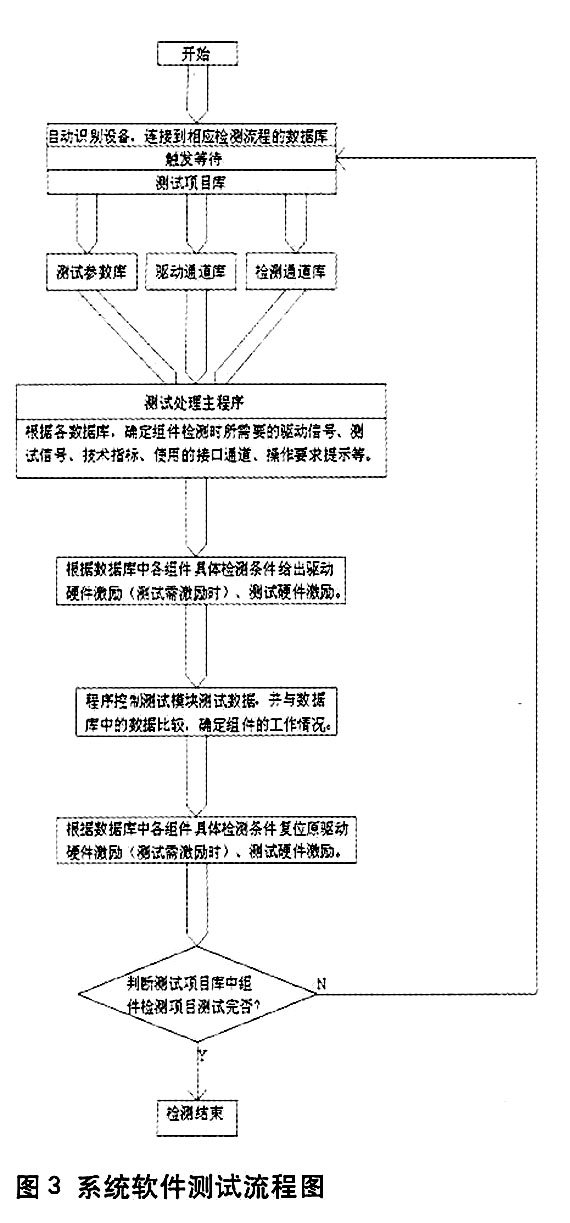

基于Lab Windows/CVI的壓力測量控制系統(tǒng)的設計

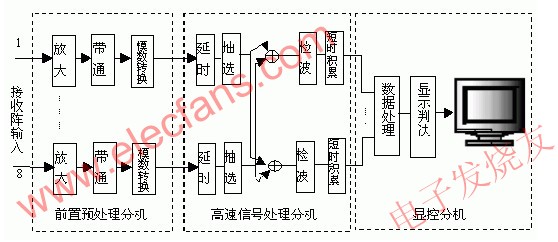

基于Lab Windows/CVI的激光聲遙感系統(tǒng)顯控軟件設

cvi 8.0 下載 (NI LabWindows 電子測量)

基于Lab Windows/CVI7.1綜合檢測系統(tǒng)

基于Lab Windows/CVI的激光聲遙感系統(tǒng)

基于無線傳輸技術的設備狀態(tài)監(jiān)測系統(tǒng)研究

quartus_11.1_Crack_Windows

quartus_11.1_SP2_Crack_Windows

LabWindows教程之LabWindows CVI的虛擬儀器設計與應用教材免費下載

CVI實驗指導(八)Lab WindowsCVI制作流水燈

CVI實驗指導(二) Lab WindowsCVI波形顯示實驗

基于QuartusⅡ6.0和Lab-Windows/CVI 8.0的DDS系統(tǒng)的改進設計

基于QuartusⅡ6.0和Lab-Windows/CVI 8.0的DDS系統(tǒng)的改進設計

評論