據媒體報道,臺積電將于2022年下半年開始量產3納米芯片,單月產能5.5萬片起,在2023年月產量將達到10.5萬片。

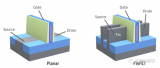

據悉,臺積電 N3 將繼續使用 FinFET 鰭式場效晶體管,而不是過渡到 GAA 環繞式結構場效晶體管。這與三星不同,三星已經表示要在 3 納米節點使用 GAA。臺積電預計 N3 將在 2022 年成為最新、最先進的節點。與 N5 相比,收益同樣不大,性能僅提升 1.1-1.15 倍,功耗提升 1.25-1.3 倍。與 7 納米相比,N3 在同樣的功率下,性能應該提高 1.25 倍 - 1.35 倍,或者在同樣的性能下功耗降低 1.55 倍 - 1.6 倍。

責任編輯:pj

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

454文章

50451瀏覽量

421943 -

臺積電

+關注

關注

44文章

5610瀏覽量

166157 -

晶體管

+關注

關注

77文章

9641瀏覽量

137870

發布評論請先 登錄

相關推薦

NMOS晶體管和PMOS晶體管的區別

NMOS晶體管和PMOS晶體管是兩種常見的金屬氧化物半導體場效應晶體管(MOSFET)類型,它們在多個方面存在顯著的差異。以下將從結構、工作原理、性能特點、應用場景等方面詳細闡述NMOS晶體管

英特爾競購High-NA EUV設備,臺積電決定回避

另一方面,臺積電的年度技術論壇正在美國和歐洲如火如荼地進行,備受世人矚目的是該公司計劃在2026年量產A16技術,該技術將結合納米片晶體管

AMD與臺積電聯手推動先進工藝發展

展望未來,臺積電正通過多個方向推動半導體行業持續發展:包括硅光子學的研發、與DRAM廠商在HBM領域的深度合作以及探索將3D堆疊技術應用于晶體管

如何提高晶體管的開關速度,讓晶體管快如閃電

咱們今天講講電子世界的跑步選手——晶體管。這小東西在電子產品里就像是繼電賽跑的選手,開關的速度決定了電子設備的快慢。那么,如何才能提高晶體管的開關速度呢?來一探究竟。如果把晶體管比作一

晶體管放大時,各級電位狀態是什么

級。 在晶體管放大電路中,輸入級負責接收輸入信號,并將其放大輸出給中間級。中間級繼續放大信號并將其輸出給輸出級,最后輸出級將信號放大到所需的幅值,并輸出給負載。 在每個級別的晶體管中,

什么是達林頓晶體管?達林頓晶體管的基本電路

達林頓晶體管(Darlington Transistor)也稱為達林頓對(Darlington Pair),是由兩個或更多個雙極性晶體管(或其他類似的集成電路或分立元件)組成的復合結構。通過這種結構,第一個雙極性晶體管放大的電流

晶體管Ⅴbe擴散現象是什么?

晶體管并聯時,當需要非常大的電流時,可以將幾個晶體管并聯使用。因為存在VBE擴散現象,有必要在每一個晶體管的發射極上串聯一個小電阻。電阻R用以保證流過每個

發表于 01-26 23:07

如何走向萬億級晶體管之路?

臺積電預計封裝技術(CoWoS、InFO、SoIC 等)將取得進步,使其能夠在 2030 年左右構建封裝超過一萬億個晶體管的大規模多芯片解決

發表于 12-29 10:35

?301次閱讀

臺積電:規劃1萬億晶體管芯片封裝策略

為達成此目標,公司正加緊推進N2和N2P級別的2nm制造節點研究,并同步發展A14和A10級別的1.4nm加工工藝,預計到2030年可以實現。此外,臺積電預計封裝技術,如CoWoS、InFO、SoIC等會不斷優化升級,使他們有望

臺積電將繼續使用 FinFET 鰭式場效晶體管?

臺積電將繼續使用 FinFET 鰭式場效晶體管?

評論