1 引 言

利用高速線掃描攝像機進行監控,具有在線監控、高精度和高速度的特點,一般常見的線掃描攝像機,感光器上的每個像素在進行動態掃描時,每次僅對移動中的物體做一次曝光,而時間延遲積分(TDI)電路具備較多且有效的積分時間,從而增強信號的輸出強度。目前,TDI技術的研究多局限于CCD工藝。CCD器件是實現TDI的理想器件,它能夠實現無噪聲的電荷累加,但傳統CCD圖像傳感器技術存在驅動電路和信號處理電路難與CCD成像陣列單片集成,需要較高的工作電壓,不能與深亞微米超大規模集成電路工藝兼容,圖像信息不能隨機讀取等欠缺。隨著CMOS集成電路工藝和開關電容電路設計技術的發展,CMOS圖像傳感的光電轉換、讀出和A/D轉換等功能已實現單芯片,但目前有關利用CMOS工藝實現線陣TDI的技術鮮有報道,其主要技術難點為如何實現低噪聲的信號累加。本文在研究CMOS電路噪聲的基礎上提出了基于CMOS工藝采用開關電容電路實現TDI功能的電路結構,詳細分析了電路的噪聲,提出了器件級噪聲優化方法,采用SMIC 0.35 μm CMOS工藝進行了仿真,仿真結果表明,該電路能夠實現TDI功能,并且具有低噪聲的特性。

2 TDI工作原理

TDI是指對同一移動中的物體進行多次曝光并將其積累。由于感光器積累多次的入射光,圖像信號及整體亮度也相應大幅提升。在對入射信號累加的同時,對噪聲信號也進行了累加,因此低噪聲的電路設計成了設計中的重點。CMOS-TDI結構如圖1所示,它類似于普通面陣CMOS圖像傳感器,n級的TDI由n行像素單元、積分陣列組和列并行ADC組成。其中,m為像素單元的個數,n為級數。本設計中,n=32。

3 電路設計

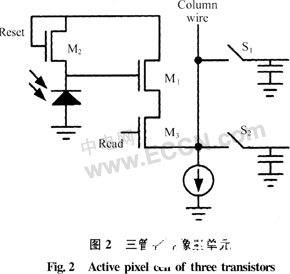

3.1 光敏單元的設計

像素單元的物理結構包括光電二極管、行選信號、電源、地信號和源跟隨晶體管等。由于有源像素相對于無源像素有低讀出噪聲、可集成到更大規模陣列和高速讀出等優勢,采用三管有源像素結構。該結構的填充系數相對較高,而且尋址方式簡單。其電路結構如圖2所示。

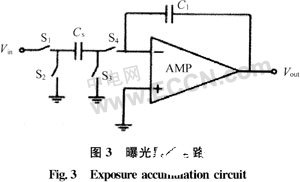

3.2 積分電路的設計

采用的積分器如圖3所示,包括采樣電容、積分電容和兩相不交迭時鐘。工作過程為:在采樣模式下,S1和S3閉合,S2和S4斷開,采樣電容CS兩端的電壓追蹤輸入信號,積分電容C1保持初始值不變。在向積分模式的轉換過程中,S1和S3斷開,S2和S4閉合,存儲在Cs上的電荷通過虛地點傳到CI上。采用適當的時序,使S3和S1之前斷開,可以避免與輸入有關的電荷注入。

3.3 開關電容電路噪聲

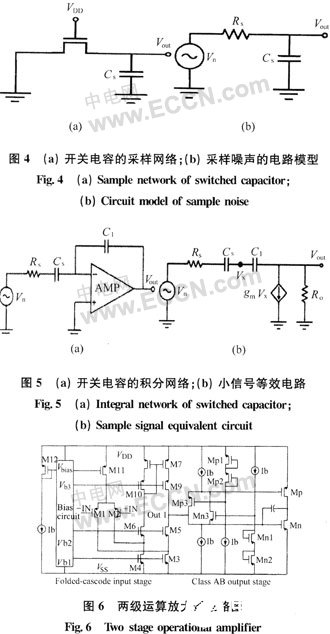

3.3.1 采樣相噪聲

首先分析積分器采樣相噪聲。采樣網絡及采樣噪聲的電路模型如圖4所示,此時積分器可等同于RC網絡。值得注意的是,若采樣時間遠大于RC網絡的時間常數,即有充分的時間使之建立,開關上的壓降在采樣相結束時近似為0。同時,開關的動作過程使開關的Si和氧化物界面狀態復位,從而阻止低頻1/f噪聲的積累。所以1/f噪聲在采樣階段可以忽略。

用作開關作用的MOS管,其熱噪聲譜密度可表示為

![]()

其中:Rs為MOS管的等效電阻;γ=1。VOUT端噪聲功率可表示為

![]()

其中,

![]()

對式(2)積分得到

![]()

觀察式(3)可以發現,Rs并不出現在表達式中,但Rs對噪聲的譜密度有帶限作用。

3.3.2 積分相噪聲

采樣階段獲得的電荷在積分階段傳輸至積分電容。開關引入多余的熱噪聲,引入的噪聲被運放和開關的開啟阻抗以及電容形成的時間常數所帶限,如圖5所示。

由小信號等效電路推導傳輸函數可得

![]()

其中:PA=gm/CS,Ps=-1/RsCS,gm為輸入MOS管跨導,而且│ Ps│≥│PA│。在頻域內積分推出

![]()

因為│Ps│》│ PA│,式(5)可簡化為

![]()

,通過合理選擇積分電容和采樣電容的比值,可以優化噪聲特性。綜合考慮噪聲、面積等綜合因素,選擇CS=CI=2pF。

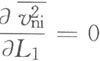

3.4 低噪聲運算放大器的設計

積分器中,運算放大器采用folded cascode結構的兩級運放,如圖6所示。其中folded Cascode共源、共柵結構能夠提高電路的增益,從而減小積分器的泄漏因子,而class AB類的輸出級提高了非線性的轉換速度。分析可知,運放第2級器件產生的噪聲在等效到輸入端時要除以第1級的增益,而通常情況下,第1級為高增益級,因此第2級器件對噪聲貢獻很小。在本文討論中,將第2級器件產生的噪聲忽略不計。具體分析為:將MOS管的器件噪聲等效為與柵極串連的電壓源,則該電路的第1級輸出OUT1端的總噪聲電流可以表示為

假設I3=I11=2I1=2I7,并考慮其對稱性,有

![]()

其中,Gm表示有效跨導,

![]()

,兇為gmγd》1,因此級聯順件M5、M6、M9和M10產生的噪聲可以忽略。輸出噪聲電流可表示為

![]()

,將其等效到運放輸入端,得到等效輸入噪聲電壓為

![]()

3.4.1 熱噪聲分析

MOS器件等效到柵極的熱噪聲譜密度可表示為

![]()

式中:對于工作在飽和區的長溝道MOS晶體管,可由推導得到γ=2/3,而對于亞微米MOS晶體管,γ可能需要更大的值來代替,在某種程度上γ還隨漏源電壓而改變[8];k=1.38×10-23J/K,是玻爾茲曼常數。將式(9)代入式(8)得到圖6所示運放的等效輸入熱噪聲的譜密度

![]()

其中

![]()

式中:S=W/L即器件寬長比;μn、μp分別為電子和空穴的遷移率。由上述推導可知,增大S1和I1即增大輸入器件的寬長比和輸入級的尾電流可減小熱噪聲。在設計中,還應考慮工藝參數與器件寬長比的關系等因素。

3.4.2 1/f噪聲分析

MOS器件等效到柵極的1/f噪聲譜密度可表示為

![]()

其中,K是與工藝有關的常數,數量級為10-25V2F。將式(12)代入式(8)可得到圖6所示運放的等效輸入1/f噪聲的譜密度

![]()

將式(13)對Ll求導,

,得到

![]()

從上式可以看出,合理選擇b、L7的尺寸,存在最優的Ll尺寸,使得1/f噪聲最小。并注意到,增大b、L,的尺寸會減小1/f噪聲。綜合考慮工藝參數及電路面積等兇素,可進一步優化噪聲特性。

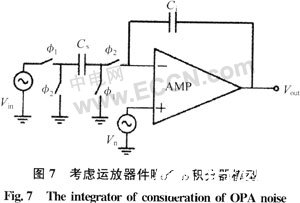

3.5 運放噪聲在積分器輸出端引入的噪聲

運放器件噪聲可以等效成在運放同相端的噪聲源,如圖7所示。

積分器的輸出可以表示成輸入信號和運放器件噪聲的函數

![]()

可以看出,運放的器件噪聲可直接傳輸至積分器輸出端,并經過1/2時鐘周期延時放大Cs/a倍后再疊加到輸出端。

4 信噪比

積分器輸出信噪比可以表示為

圖26 其中Vsig為積分器輸出信號

,Vnopa、Vnsc和Vnpixel分別為運放、開關電容電路和像素單元在積分器輸出端的等效噪聲。假設像素單元每次讀m的信號是相等的,讀出的噪聲也是相等的,如果忽略運放和開關電容電路引入的噪聲,則

即經n級TDI后輸出信噪比為單級時的

倍,其中n為積分器的級數。對于CMOS電路,器件噪聲是不可避免的,因此低噪聲的電路設計是提高該電路信噪比的關鍵。

5 仿真結果

5.1 積分器仿真結果

在標準CMOS工藝下,通過合理的時序關系,TPI電路可由積分陣列來實現。圖8為-32級TDl電路的仿真結果,積分陣列對32行的像素信號進行積分累加,實現了TDI功能。

5.2 運算放大器仿真結果

采用SMIC O.35μm CMOS工藝,本文設計的運放可以達到大約80 dH的直流增益,40 MHz的單位增益帶寬,65°的相位裕度。圖9為spectra仿真的運放頻率特性區線。

5.3 積分器輸出端噪聲匯總

表1列出了單級積分器各部分產生的等效輸出噪聲,其中,VnTi、Vnfi為運算放大器等效輸入的熱噪聲和1/f噪聲。在帶寬范圍內對運放輸入噪聲譜密度進行積分,得到運放等效輸入噪聲,本設計運放帶寬為40 MHz,積分得到運放等效輸入噪聲為36.1μV,乘以增益即得到運放器件噪聲在積分器輸出端的等效噪聲,其余各部分噪聲可以根據所選取的采樣電容和積分電容值計算得到。

6 結 論

提出了在標準CMOS工藝下TDI電路的實現方法,并詳細分析了電路的噪聲,給出了器件級噪聲的優化方法。采用SMIC 0.35μm工藝對電路進行了仿真驗證,仿真結果表明,該電路能夠實現TDI功能,并且具有低噪聲特性。

責任編輯:gt

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752042 -

CMOS

+關注

關注

58文章

5684瀏覽量

235149 -

CCD

+關注

關注

32文章

879瀏覽量

142144

發布評論請先 登錄

相關推薦

怎么采用標準CMOS工藝設計RF集成電路?

DCDC變換器輸出電壓噪聲優化和測試

CMOS技術及接收器拓撲結構

3GHz CMOS低噪聲放大器的優化設計

低功耗低噪聲CMOS放大器設計與優化

3GHz CMOS低噪聲放大器優化設計

采用CMOS工藝的射頻設計研究

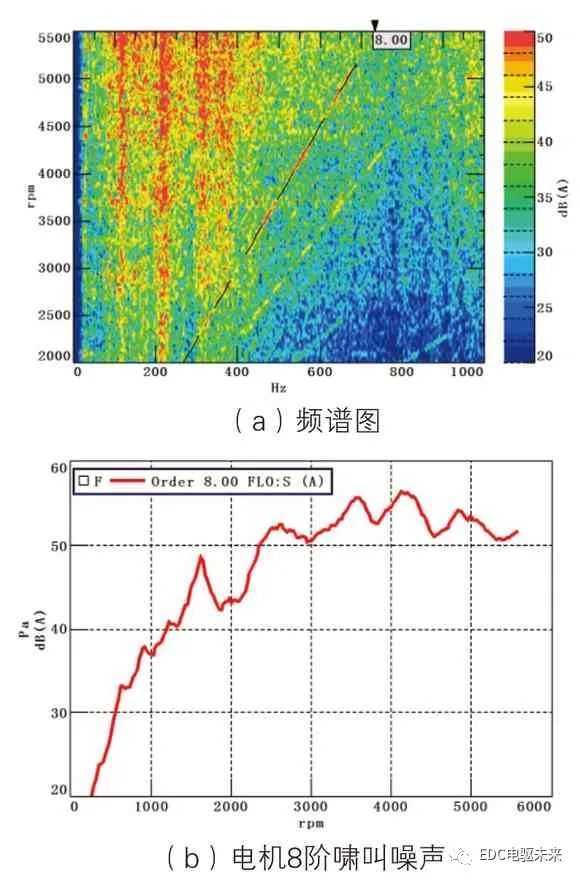

純電動汽車電機嘯叫噪聲優化

100nVpp百納伏噪聲優化

基于CMOS工藝實現器件級噪聲優化方法的研究

基于CMOS工藝實現器件級噪聲優化方法的研究

評論