高速PCB設計完成后,一般都要經過評審才會發出去做板。硬件組在評審的過程中,一般都會在各個方面給出修改的建議,比如EMC,貼片,信號完整性等方面。下面匯總一些以前PCB評審時,硬件組給出的一些修改建議。

1.多層板在設計時至少都會有一個地層,一個完整的地平面,但是在頂層和底層由于要擺放元器件,走線,地平面可能會被瓜分得零零碎碎的,有的呈現的是浮銅,有的呈現的是一條長條狀的銅箔。如果長條狀的地平面,端部又沒有過孔回到地層,這種情況在高速電路板上就會等效成一條天線,產生天線效應,造成嚴重的EMC問題。所以頂層和底層的地平面在設計高速PCB需要做合理的處理和優化。這些情況如下圖所示。

2.優化電源平面,能加寬的平面盡量加寬,有的電源平面雖然看起來很寬了,但是有可能中間打了幾個孔,把大部分的銅箔阻斷了,寬度實際上是變小了,寬度變小的地方阻抗可能就變大,電源紋波可能會增大。加寬電源平面還有一個好處,它和地平面的板級濾波效果會變好。這是從電源完整性方面去優化PCB。

3.有些走線需要做好包地,比如時鐘線,這些線要做好包地設計,如果不包地設計,與其相鄰的走線就有可能會發生串擾現象,如果數字信號的線,那么就會發現數據通信錯誤的問題。因為高速電路的時鐘信號的上升時間和下降時間很快,與其相鄰的線就會被感應出正脈沖或者是負脈沖,對數字信號來說,就是1或0,從而導致通信錯誤。

4.有些元器件或者是走線離板邊很近,會有問題。因為離得太近板邊,PCB的制作工藝可能會損壞焊盤或者走線。

5.有些線可以從美觀的角度優化一下。

編輯:hfy

-

元器件

+關注

關注

112文章

4694瀏覽量

92043 -

PCB設計

+關注

關注

394文章

4671瀏覽量

85321

發布評論請先 登錄

相關推薦

高速PCB設計指南

專業PCB設計,高速PCB設計,PCB設計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設計公司,迅安通科技公司介紹

PCB設計與PCB制板的緊密關系

PCB設計的EMC有哪些注意事項

高速pcb與普通pcb的區別是什么

PCB設計中的常見問題有哪些?

pcb設計

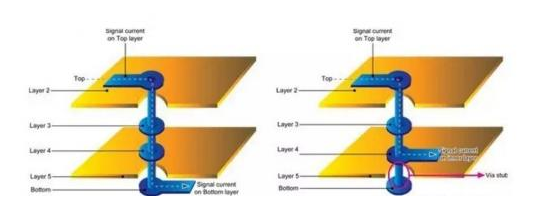

多層pcb設計如何過孔的原理

高速PCB設計中,如何避免過孔帶來的負面效應

EMC之PCB設計技巧

高速PCB設計中的射頻分析與處理方法

關于高速PCB設計的5個修改建議

關于高速PCB設計的5個修改建議

評論