12月10日,中國集成電路設計業2020年會在重慶隆重舉行,臺積電(中國)副總經理陳平指出,5G和AI是新時期的核心技術,對性能和功耗都有極高的要求,因此必須有先進工藝的支持。而5G和AI產生的大量數據需要落地,與萬物互聯,這些需要各種特殊工藝來實現,8英寸傳統工藝比12英寸工藝需求不遑多讓。因此,5G和AI會帶動整個晶圓代工行業。

陳平表示,新冠疫情是2020年突發的大災難,但由于防疫的需要,新冠疫情還產生了一些良性的副作用,其中之一就是對數字化進程的推進,例如線上辦公、線上學習、測溫安防等領域實現了飛躍式發展。

“現在是數據大量提升的時代,這些數據的處理都需要晶體管,因此晶體管數量也在隨著數據而開始以驚人的速度增長。”陳平說。

陳平指出,晶體管數量的增長通過工藝來實現主要有兩個路徑,第一個路徑就是沿著摩爾定律在單片上延伸,第二個路徑就是通過3D集成。目前,世界上最大的GPU已經擁有了500億個晶體管,而用3D集成的最大芯片擁有2000億個晶體管。但隨著工藝的日新月異發展,這些記錄很快也會被打破。

陳平強調,大數據的爆炸式增長對工藝的進步提出了極高的要求,因此工藝的進步一定要追趕上市場需求。

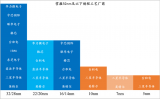

目前,很多的應用都有高能效和集成度兩大要求。陳平表示,為了實現這兩點,先進工藝是不二選擇。以智能終端、5G網絡、邊緣計算和云計算為例,大多數芯片都需要先進工藝來支持。

全產業都在關注先進工藝能否繼續沿著摩爾定律下探,以支持應用的要求。陳平指出,臺積電的先進工藝在全行業的支持下,依然能保持以往的發展速度。臺積電的5nm工藝已經經過了3個季度的量產,無論在產出還是良率上都表現優異。另外,3nm研發也非常順利,預計明年完成驗證,并于后年實現大批量生產,更先進的2nm研發也在如火如荼的進行當中。

陳平還指出,晶體管的微縮有幾大要素,其中最主要的就是光刻技術。從以往光波長為一百多納米的DUV來處理十幾二十納米的器件,到現在用13.5nm光波長的EUV來處理5nm和7nm,晶體管微縮已經實現了跨越。從光刻技術角度來看,EUV可以保證先進工藝下探到2nm以下。

除了光刻,器件結構和器件材料也是晶體管微縮的兩大要素。陳平表示,FinFET結構可以支持到3nm工藝,3nm以后目前也出現了器件結構的新選擇,包括nanowire和nanosheet。材料方面,純粹的硅材料在3nm以后遷移率會快速降低,好在科技人員創造出了新的2D材料,提供更佳的遷移率。

“摩爾定律什么時候終結,我個人認為沒有答案,我們永遠不能低估人類的創造力。當我們遇到困難的時候,總有科學家會找到新的答案。”陳平如是說。

責任編輯:tzh

-

臺積電

+關注

關注

44文章

5609瀏覽量

166131 -

晶圓

+關注

關注

52文章

4846瀏覽量

127805 -

晶體管

+關注

關注

77文章

9635瀏覽量

137857

發布評論請先 登錄

相關推薦

臺積電引領全球晶圓代工熱潮,明年產值料增逾二成

人工智能需求持續爆發,全球晶圓代工行業勢頭強勁

三星晶圓代工發力,挑戰臺積電地位

晶圓代工迎來復蘇,各大廠商展現出回升勢頭

5G智能防爆手持終端在石油化工行業中扮演著什么角色?

中芯國際躋身全球第三大晶圓代工廠,季收入首次超越聯電、格芯

全球晶圓代工行業2024年Q1營收下降,AI需求驅動增長

晶圓代工廠密集降價搶單,原因究竟為何?

5G和AI將帶動整個晶圓代工行業發展

5G和AI將帶動整個晶圓代工行業發展

評論