12月11日上午,在中國集成電路設計業2020年會之《EDA與IC設計創新論壇》上,行業各路大咖在會場對EDA的現狀與前景展開討論。

新思科技技術支持副總監湯木明認為,先進工藝下,設計實現的挑戰不只在于PR是否能理解復雜工藝規則并在符合規則實施PPA優化。影響設計實現周期和目標可以更早來自于綜合引擎是否能否理解工藝規則加入優化考慮中,甚至可能來自于在RTL設計結構的選擇中是否充分評估現金工藝特性的影響。

Cadence高級資深總監劉淼表示,隨著先進工藝節點變得越來越小,設計性能目標似乎總是在提高,不僅是時鐘頻率,而且是功率和面積。為了滿足這些具有挑戰性的要求,Cadence不斷研究新的創新技術,這些技術將有助于交付最新的高性能硅器件。機器學習是一個很好的例子,并顯示出進一步改善數字設計自動化的巨大潛力。

上海國微思爾芯首席執行官兼總裁林俊雄則表示,先進節點的VLSI不只是密度高、系統架構復雜,更往往會搭配多核CPU和需要復雜的處理器運行環境,整體使驗證工作急劇增加。

關于摩爾定律的發展,Mentor亞太區技術總監李立基認為,摩爾定律還在繼續往前走,但是隨著芯片的集成度不斷提高,成本卻沒有降低。同時,李立基介紹了最新的封裝技術對芯片集成帶寬、速率的提高。

另外,Ansys半導體事業部主任工程師姚欣認為,3DIC設計的每一個階段——從芯片到封裝,再到PCB再到系統——都需要仔細關注,以確保在面對熱、功耗、電磁和機械約束以及相互作用時的可靠性。但是,設計階段通常是不連貫的,分散的,從一個抽象層到另一個抽象層的可見性有限。芯片—封裝協同設計是3D集成電路設計的重要組成部分,以成為現代系統設計的重要要求。

談到電源管理芯片,北京華大九天產品總監劉曉明認為,當前電源管理芯片的主要難題在于高功能集成度給設計帶來的難題,多應用場景給仿真驗證帶來的難題和高功率密度給可靠性分析帶來的難題。

而在存儲器方面,上海概倫電子副總裁劉文超表示,存儲器市場飛速發展,已占據全球集成電路銷售額首位,其中DRAM和閃存占比最高,而下一代非易失性存儲器的市場平均增長率極高,達到104%,預計在2023年擴大到72億美元。存儲技術在不斷的提高存儲密度、降低成本。

芯華章商務拓展總監祝丹表示,EDA已經不再是特別小的領域,EDA需要進行行業整合,未來EDA可以和AI與云計算結合。

南京EDA創新中心研發副總經理陳剛表示,隨著IC芯片的復雜度和集成度與日俱增,IC設計對EDA的要求與依賴也越來越高,單一EDA工具很難滿足設計人員對IC設計的全流程需求,不同工具間的切換又為數據完整性增添了風險。

芯師(上海)電子應用工程師經理劉客表示,當從一代工藝技術節點演變到下一代節點時,由于工藝偏差造成的工藝參數離散和由版圖設計到實際光刻過程帶來的光學失真真正在顯著增加。這現象的疊加使得集成電路制造的復雜性不斷提高,同時也影響了良率和可靠性。在納米級微縮工藝中,界定了改善這些現象的方法,而為了達到改善的目的,必須對IC性能進行有效的預測和監測。因此,設計初期分析工藝偏差、優化設計參數和驗證環境條件就變得十分必要。

責任編輯:tzh

-

IC

+關注

關注

36文章

5900瀏覽量

175236 -

cpu

+關注

關注

68文章

10825瀏覽量

211146 -

eda

+關注

關注

71文章

2708瀏覽量

172880

發布評論請先 登錄

相關推薦

醫療機器人發展現狀與趨勢

工控機廠家發展現狀及未來趨勢

國產光電耦合器:2024年的發展現狀與未來前景

國產FPGA的發展前景是什么?

《RISC-V產業年鑒2023》發布,洞察產業發展現狀與趨勢

2.晶體和振蕩器 行業研究及十五五規劃分析報告(行業發展現狀及“十五五”前景預測)

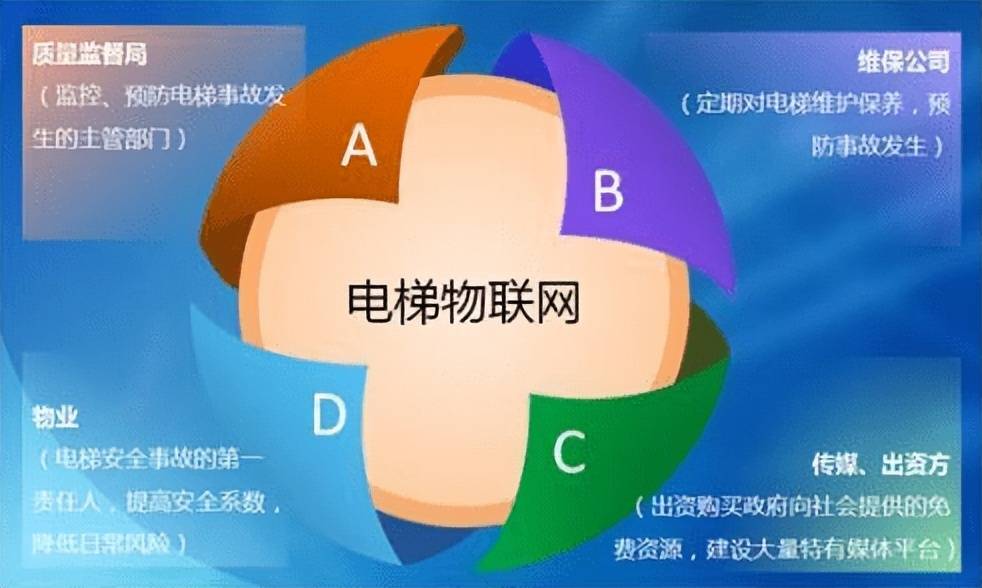

梯云物聯|全球及中國智能電梯市場:蓬勃現狀與廣闊前景

國內EDA工具AI技術應用現狀及發展動態分析

萬兆電口模塊的產業發展現狀與前景展望

工程振弦采集儀監測技術的發展現狀與展望

光伏行業發展現狀與發展趨勢報告

EDA產業發展現狀與前景分析

EDA產業發展現狀與前景分析

評論