對于研發人員而言,大家總是在追求低功耗設計。采用低功耗設計,無疑是能夠帶來諸多好處。為幫助大家了解如何降低功耗,本文中,小編將對降低FPGA功耗的設計技巧加以闡述。如果你對功耗、低功耗以及相關內容具有興趣,不妨繼續往下閱讀哦。

新一代 FPGA的速度變得越來越快,密度變得越來越高,邏輯資源也越來越多。那么如何才能確保功耗不隨這些一起增加呢?很多設計抉擇可以影響系統的功耗,這些抉擇包括從顯見的器件選擇到細小的基于使用頻率的狀態機值的選擇等。

為了更好地理解本文將要討論的設計技巧為什么能夠節省功耗,我們先對功耗做一個簡單介紹。

功耗包含兩個因素:動態功耗和靜態功耗。動態功耗是指對器件內的容性負載充放電所需的功耗。它很大程度上取決于頻率、電壓和負載。這三個變量中的每個變量均在您的某種控制之下。

動態功耗 = 電容×電壓2×頻率

靜態功耗是指由器件中所有晶體管的泄漏電流(源極到漏極以及柵極泄漏,常常集中為靜止電流)引起的功耗,以及任何其他恒定功耗需求之和。泄漏電流很大程度上取決于結溫和晶體管尺寸。

恒定功耗需求包括因終接(如上拉電阻)而造成的電流泄漏。沒有多少措施可以采用來影響泄漏,但恒定功耗可以得到控制。

盡早考慮功耗

您在設計的早期階段做出的功耗決定影響最大。決定采用什么元件對功耗具有重大意義,而在時鐘上插入一個 BUFGMUX 則影響甚微。對功耗的考慮越早越好。

恰當的元件

并不是所有元件都具有相同的靜止功耗。根據普遍規則,器件工藝技術尺寸越小,泄漏功耗越大。但并不是所有工藝技術都一樣。例如,對于 90 nm 技術來說,Virtex-4 器件與其他 90 nm FPGA 技術之間在靜止功耗方面存在顯著差異,

然而,在靜止功耗隨工藝技術縮小而增加的同時,動態功耗卻隨之減小,這是由于較小的工藝有著更低的電壓和電容。考慮好哪種功耗對你的設計影響更大——待機(靜止)功耗還是動態功耗。

除通用切片邏輯單元外,所有Xilinx器件都具有專門邏輯。其形式有塊 RAM、18×18 乘法器、DSP48 塊、SRL16s,以及其他邏輯。這不僅在于專門邏輯具有更高的性能,還在于它們具有更低的密度,因而對于相同的操作可以消耗較少的功率。評估您的器件選項時,請考慮專門邏輯的類型和數量。

選擇適當的 I/O 標準也可以節省功耗。這些都是簡單的決定,如選擇最低的驅動強度或較低的電壓標準。當系統速度要求使用高功率 I/O 標準時,計劃一個缺省狀態以降低功耗。有的 I/O 標準(如 GTL/+)需要使用一個上拉電阻才能正常工作。因此如果該 I/O 的缺省狀態為高電平而不是低電平,就可以節省通過該終接電阻的直流功耗。對于 GTL+,將50Ω終接電阻的適當缺省狀態設置為 1.5V,可使每個 I/O 節省功耗 30 mA。

數據使能

當總線上的數據與寄存器相關時,經常使用片選或時鐘使能邏輯來控制寄存器的使能。進一步來說,盡早對該邏輯進行“數據使能”,以阻止數據總線與時鐘使能寄存器組合邏輯之間不必要的轉換,如圖 1 所示。紅色波形表示原設計;綠色波形表示修改后的設計。

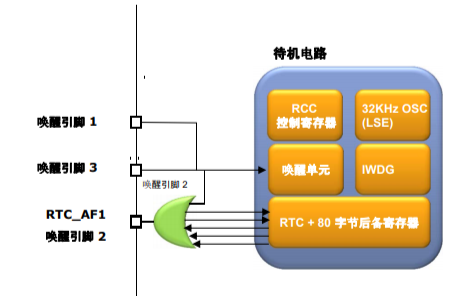

另一種選擇是在電路板上而不是在芯片上進行這種“數據使能”。以盡可能減小處理器時鐘周期。此概念是使用 CPLD 從處理器卸載簡單任務,以便使其更長時間地處于待機模式。

讓我們來看一個在狀態 7 和狀態 8 之間頻繁進行狀態轉換的狀態機。如果您為該狀態機選擇二進制編碼,將意味著對于每次狀態 7 和狀態 8 之間的狀態轉換,將有四位需要改變狀態,如表 1 所示。如果狀態機采用格雷碼而不是二進制碼來設計,則這兩個狀態之間的轉移所需的邏輯轉換的數量將降至僅一位。另外,如果將狀態 7 和 8 分別編碼為 0010 和 0011,也可以達到同樣的效果。

時鐘管理

在一個設計的所有吸收功耗的信號當中,時鐘是罪魁禍首。雖然一個時鐘可能運行在 100 MHz,但從該時鐘派生出的信號卻通常運行在主時鐘頻率的較小分量(通常為 12% ~ 15%)。此外,時鐘的扇出一般也比較高——這兩個因素顯示,為了降低功耗,應當認真研究時鐘。

如果設計的某個部分可以處于非活動狀態,則可以考慮使用一個 BUFG-MUX 來禁止時鐘樹翻轉,而不是使用時鐘使能。時鐘使能將阻止寄存器進行不必要的翻轉,但時鐘樹仍然會翻轉,消耗功率。不過采用時鐘使能總比什么措施也沒有強。

隔離時鐘以使用最少數量的信號區。不使用的時鐘樹信號區不會翻轉,從而降低該時鐘網絡的負載。仔細布局可以在不影響實際設計的情況下達到此目標。

對 FPGA 顯然也可以使用同一概念。雖然 FPGA 不一定擁有待機模式,但使用一個 CPLD 中途欄截總線數據并有選擇地將數據饋送到 FPGA 也可以省去不必要的輸入轉換。

CoolRunner-II CPLD 包含一種稱為“數據門控”的功能,可以禁止引腳上的邏輯轉換到達 CPLD 的內部邏輯。該數據門控使能可通過片上邏輯或引腳來控制。

狀態機設計

根據預測的下一狀態條件列舉狀態機,并選擇常態之間轉換位較少的狀態值。這樣,您就能夠盡可能減少狀態機網絡的轉換量(頻率)。確定常態轉換和選擇適當的狀態值,是降低功耗且對設計影響較小的一種簡單方法。編碼形式越簡單(一位有效編碼或格雷碼),使用的解碼邏輯也會越少。

功耗估算工具

賽靈思提供了兩種形式的功耗估算工具:一種叫做 Web Power Tools 的設計前工具和一種叫做 Xpower 的設計后工具。利用它,您可以僅憑設計利用率估計就能獲得功耗評估,而無需實際設計文件。

XPower 是一種設計后工具,用于分析實際器件利用率,并結合實際的適配后 (post-fit) 仿真數據(VCD 文件格式),給出實際功耗數據。利用 Xpower,您可以在完全不接觸芯片的情況下分析設計改變對總功耗的影響。

基于 Web 的功耗工具

基于 Web 的功耗估計是在設計流程的早期獲得器件功耗情況的最快捷和最方便的方法。這些工具每個季度都會發布新版本,因此信息總是最新的,且不需要安裝或下載,只需要擁有互聯網連接和 Web 瀏覽器即可。您可以指定設計參數并保存和加載設計設置,免去了通過交互使用重新輸入設計參數的麻煩。只要有對設計行為的估計并選定目標器件即可開始。

Xpower:集成的設計專用功耗分析

Xpower 是所有 Xilinx ISE設計工具的一個免費組件,您可以利用它對您的基于設計的功耗需求進行詳細得多的估計。XPower 是在映射或布局和布線后設計的基礎上對器件功耗進行估計的。

對于成熟的投產的 FPGA 和 CPLD,XPower 計算出的功耗估計的平均設計批量誤差 (suite error) 小于 10%。它將把器件數據與您的設計文件結合起來綜合考慮,并按照您的專門設計信息給出估計器件功耗的高精度報告。

XPower直接集成在 ISE 軟件中,可提供層次化的詳細的功耗顯示、詳細的總結報告和功耗向導,即使是新用戶也可輕易上手。XPower 可接受仿真的設計活動數據,并可以 GUI 模式和批處理模式運行。

XPower 將考慮設計中的每個網絡和邏輯元素。ISE 設計文件提供準確的資源使用情況;XPower 交叉參考布線信息以及特性化電容數據。于是物理資源針對電容進行特性化。設計特性化將對新器件持續進行,以給出最精確的結果。Xpower 使用了網絡翻轉速率和輸出負載。然后 XPower 計算功耗和結溫,還可以顯示單個網絡的功耗數據。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601804 -

cpld

+關注

關注

32文章

1247瀏覽量

169201 -

寄存器

+關注

關注

31文章

5317瀏覽量

120002

發布評論請先 登錄

相關推薦

FPGA低功耗設計

聊一聊FPGA低功耗設計的那些事兒

FPGA低功耗設計小貼士

FPGA設計怎么降低功耗

FPGA的低功耗該怎么設計?

便攜式產品具有低功耗意識的FPGA設計方法

FPGA低功耗的設計技巧詳細介紹

FPGA低功耗的設計技巧詳細介紹

評論