1.

硅基調頻連續波雷達信號源技術綜述

調頻連續波毫米波雷達能夠具有全天候、探測距離遠以及可同時測量目標距離和相對速度等特點,是無人駕駛汽車應用的最關鍵傳感器之一。隨著半導體技術的快速發展,硅基工藝在成本和集成度方面的巨大優勢使硅基調頻連續雷達吸引了來自學術界和工業界的大量研究。做為系統的核心組件,調頻連續波雷達信號源技術的發展水平直接決定了調頻連續波雷達所能實現的功能和性能。

清華大學微納電子系池保勇、鄧偉和賈海昆課題組對硅基調頻連續波雷達信號源技術的研究現狀和發展趨勢進行了綜述。在今后的發展趨勢中,大掃頻帶寬、快速掃頻和低頻率誤差調頻連續波雷達信號源技術值得重點關注。

圖. 清華大學課題組研發的2發3收77GHz CMOS毫米波雷達芯片和樣機。

Silicon-based FMCW signal generators: A review

Wei Deng, Haikun Jia, Baoyong Chi

J. Semicond. 2020, 41(11): 111401

doi: 10.1088/1674-4926/41/11/111401

Full Text

2.

模擬與混合信號CMOS集成鎖相環芯片設計技術綜述

CMOS全集成鎖相環(Phase-Locked Loop, PLL)是現代片上系統(System-on-Chip, SoC)集成電路芯片中必不可少的重要組成部分,其廣泛用于SoC中數字電路系統時鐘生成,高速有線通信數據調制時鐘生成,以及無線通信載波信號生成。近年來,隨著CMOS技術的不斷發展,集成電路工藝節點的持續推進,全數字鎖相環(All-Digital PLL, ADPLL)開始變得流行起來。其主要原因為數字電路在先進CMOS工藝條件下具有比模擬電路更靈活的可擴展性、更好的跨工藝設計可移植性和更小的面積等優勢。

但是,相較于廣泛應用的模擬與混合信號鎖相環(Analog and Mixed-Signal PLL, AMS-PLL)而言,ADPLL由于存在量化噪聲,且對電源噪聲更加敏感,因此,ADPLL通常具有比AMS-PLL更高的輸出信號抖動(jitter)。該問題限制了ADPLL在需要生產極低時鐘抖動的應用場景中的應用,包括高性能處理器、5G無線通信、高速有線通信(比如56/112Gbps高速通信)以及下一代以太網通信等應用。因此,即使目前工藝節點尺寸已經到10nm以下,AMS-PLL依然是目前多數應用中的優先選擇。

中國科學院半導體研究所張釗研究員等對AMS-PLL的基本電路結構和基本原理、主要研究問題、目前研究進展做了全面介紹,讓有關科研及工程技術人員能夠全面了解AMS-PLL的基礎、電路設計的常見問題以及主流解決辦法。同時,在全面介紹AMS-PLL的基礎上,根據不同應用場景,對不同結構的AMS-PLL作了優缺點分析與對比,為有關芯片設計人員根據自身所需指標需求合理進行AMS-PLL結構選型提供參考與指導。

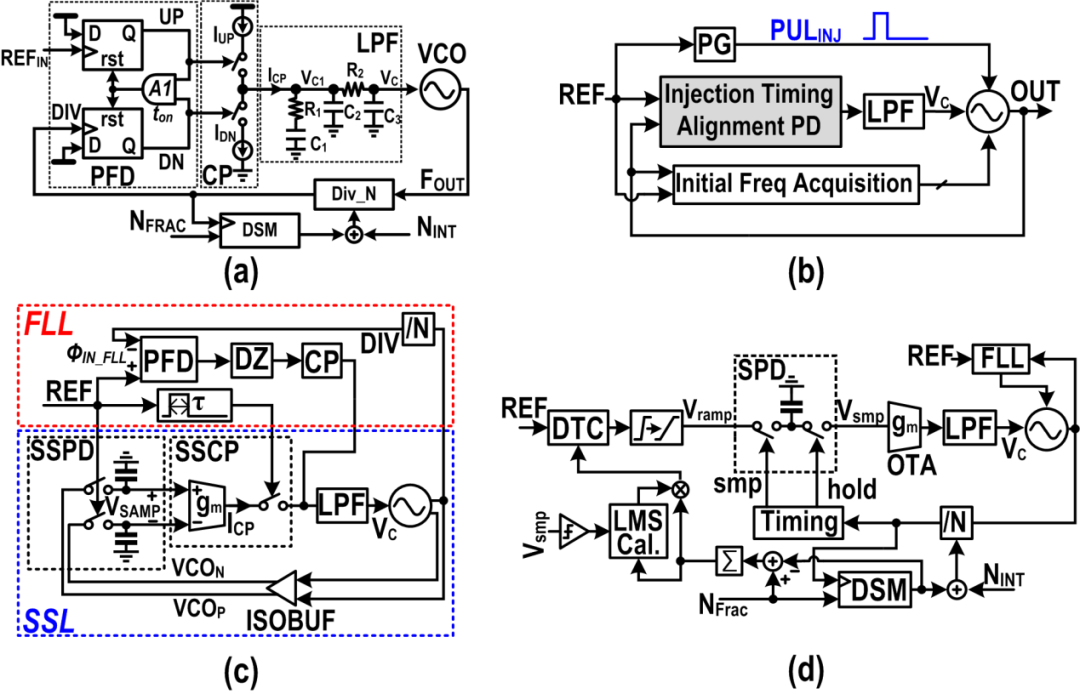

本綜述論文主要包括以下內容:1、簡要回顧AMS-PLL中最常用的電荷泵型鎖相環(Charge-Pump based PLL, CPPLL)的基本原理;2、總結基本型CPPLL中存在的技術問題;3、系統回顧現有提升CPPLL性能的技術;4、簡要介紹近年來開始成為研究熱點的新型結構極低抖動AMS-PLL,包括注入鎖定鎖相環(Injection-Locked PLL, ILPLL)、亞采樣鎖相環(Sub-Sampling PLL, SSPLL)和采樣鎖相環(Sampling PLL, SPLL);5、分析與對比前面介紹的4種AMS-PLL結構,并據此討論在不同應用背景下進行AMS-PLL結構選型的考慮,為有關芯片設計人員根據自身所需指標需求合理進行AMS-PLL結構選型提供參考與指導。

圖1. 四種AMS-PLL電路結構框圖:(a)CPPLL, (b) ILPLL, (c), SSPLL, (d)SPLL。

CMOS analog and mixed-signal phase-locked loops: An overview

Zhao Zhang

J. Semicond. 2020, 41(11): 111402

doi: 10.1088/1674-4926/41/11/111402

Full Text

3.

作為現實模擬世界與數字世界之間的接口,模數轉換器(ADC)在眾多電子系統中有著廣泛而關鍵的應用。近年來蓬勃發展的物聯網技術對低成本、高能效、高精度ADC提出了巨大的需求。逐次逼近型(SAR)ADC因為其結構簡單、功耗低、對先進工藝兼容性好等優勢,成為近年來該領域一個非常熱門的架構。然而,傳統SAR難以實現高精度,這主要受限于以下幾個關鍵的誤差來源:

(1)采樣噪聲。長期以來,學術界公認的ADC采樣噪聲極限是kT/C,要想降低采樣噪聲,唯一的辦法就是增加采樣電容,然而大采樣電容會給ADC的輸入驅動電路和基準緩沖電路帶來很大的功耗和設計復雜度。

(2)比較器噪聲。比較器噪聲是限制SAR ADC信噪比的最主要因素之一。降低6dB的比較器噪聲,需要將比較器的功耗增大四倍,這將嚴重影響ADC整體的能效。

(3)數模轉換器(DAC)失配。DAC會給ADC帶來非線性失真的問題,限制了ADC的精度;而且,隨著集成電路工藝的演進,器件尺寸越小越小,DAC失配的問題將更加嚴重。

近年來,清華大學電子系孫楠教授課題組提出了一系列新型ADC架構和電路技術,致力于降低SAR ADC中的這些關鍵誤差因素,實現高能效高精度的SAR ADC。

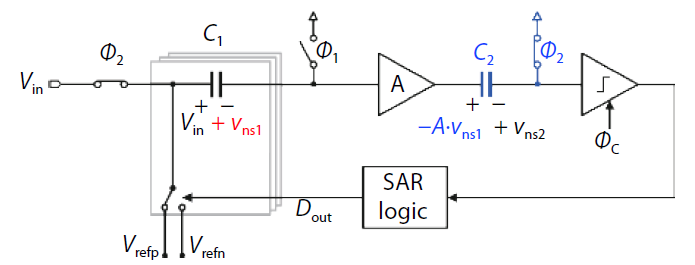

針對采樣噪聲的問題,孫教授課題組提出了連續時間SAR架構、kT/C噪聲抵消技術、噪聲頻譜密度和帶寬解耦技術,打破了kT/C噪聲極限,使得ADC的采樣電容尺寸可以大幅降低而不會帶來巨大的噪聲代價,進而有效緩解了輸入驅動電路和基準緩沖電路的負擔。

圖1. 可抵消kT/C噪聲的SAR ADC。

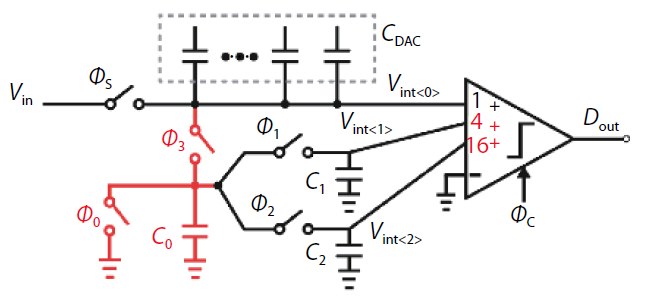

針對比較器噪聲的問題,孫教授課題組提出了多種新穎的噪聲整形SAR ADC技術,包括無源噪聲整形、無源增益產生以及閉環動態放大器等。這些技術不依賴于傳統的靜態放大器就可以實現優異的噪聲整形特性,具有低功耗、高PVT穩定性等特性。

圖2. 無源噪聲整形SAR ADC。

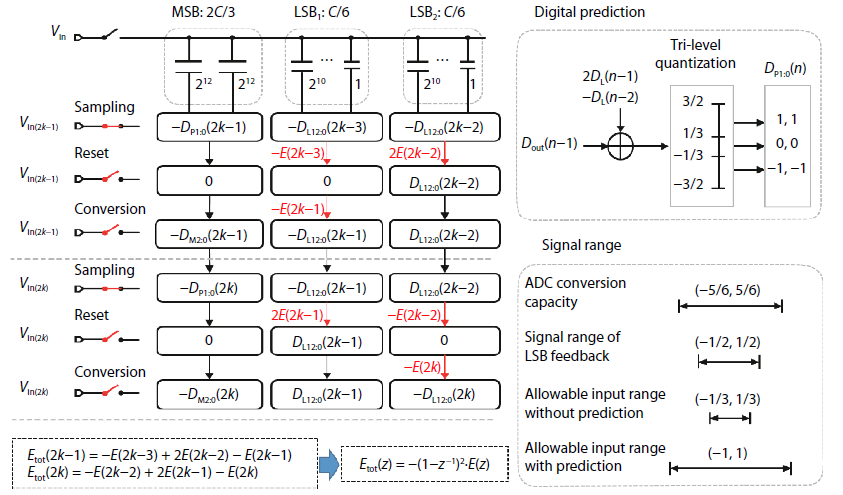

針對DAC失配的問題,孫教授課題組提出了高階DAC失配誤差整形技術,其硬件復雜度低、整形能力強,并可廣泛應用于低通、高通、帶通ADC中。同時,課題組還提出了用數字預測的方法來解決適配誤差整形技術帶來的動態范圍損失的問題。

圖3. 二階DAC失配誤差整形技術。

本文提出的一系列技術可有效提高SAR ADC的精度,同時保證其高能效的特性,在無線通信、物聯網、生物醫療電子等領域有著廣闊的應用前景。隨著研究者們對該領域的持續深入研究,作者相信在將來的高精度ADC設計中,SAR將成為ΔΣ以外的一個極具吸引力的可選架構。

Error suppression techniques for energy-efficient high-resolution SAR ADCs

Jiaxin Liu, Xiyuan Tang, Linxiao Shen, Shaolan Li, Zhelu Li, Wenjuan Guo, Nan Sun

J. Semicond. 2020, 41(11): 111403

doi: 10.1088/1674-4926/41/11/111403

Full Text

4.

高速高精度電流舵型DAC綜述

數模轉換器用于將數字信號轉換成模擬信號,作為連接數字世界和模擬世界的重要橋梁,其應用十分廣泛,在有線及無線通信、數字信號處理、儀表測控、醫療及軍工等領域發揮著重要作用。隨著5G等現代通信技術的快速發展,系統對數據傳輸速率、帶寬及精度均提出了更高的要求,所以對DAC采樣速率與分辨率的高要求經常成為系統性能提升的瓶頸。

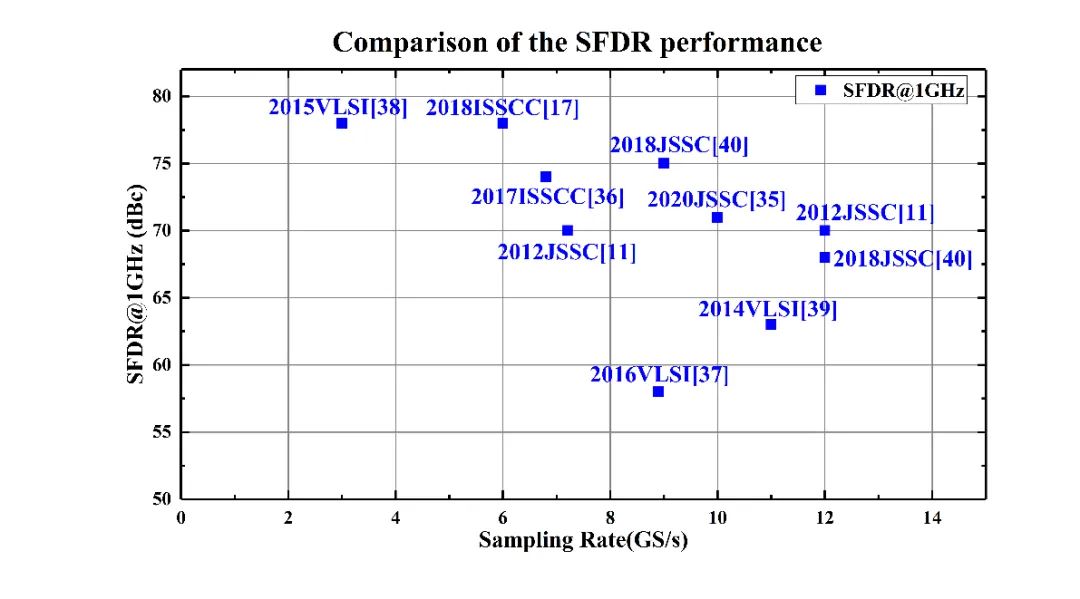

中國科學院微電子所周磊研究員等回顧了近年來國內外報道的關于高速高精度DAC的優秀成果,從電流舵型DAC的結構入手,介紹了各部分典型的電路實現與改良技術。對其中最具代表性/性能最佳的部分成果以圖表的形式進行了更詳細和深入的匯總與比較。

本文比較全面和詳實地介紹了國內外關于高速高精度DAC的優秀成果與代表性技術,對讀者了解電流舵型DAC的架構以及最新研究進展有一定幫助。

A survey of high-speed high-resolution current steering DACs

Xing Li, Lei Zhou

J. Semicond. 2020, 41(11): 111404

doi: 10.1088/1674-4926/41/11/111404

Full Text

5.

數字低壓差穩壓器技術的回顧和展望

在高能效的片上系統(SoC)中,資源的高度動態分配,對電源管理的粒度提出了要求。細粒度電源管理要求每個電源域都用單獨的電壓穩壓器供電,這要求穩壓器具有全集成、低壓差、中等電源抑制等特點。

傳統的模擬低壓差穩壓器(LDO)只能工作在較高輸入電壓和壓差的情況下,難以使用于高能效系統中。相反的,數字LDO完美的克服了上述缺點。但是,數字LDO自身離散采樣的特性,使得其響應速度較慢,電源抑制性能遠遜模擬LDO。

澳門大學黃沫教授課題組長期進行數字LDO技術的研究,并發表了相關成果。本文中,作者首先對數字LDO研究背景進行了介紹。其次,在低電壓工作和工藝伸縮性、功耗-速度折中、穩定性、電源抑制等方面,對模擬和數字LDO進行了比較。然后,作者對數字LDO中的量化器設計技術,PID控制技術,電源抑制比提升技術等方面進行了文獻回顧和分析。最后,作者展望了數字LDO的未來發展方向。

隨著細粒度電源管理需求的深化,數字LDO技術必將繼續發展。其中,將數字控制算法、包括深度學習等技術應用其中,將是后續發展的潛在方向;另外,可全面綜合的數字LDO也將是一個有趣的方向。

A comparative study of digital low dropout regulators

Mo Huang, Yan Lu, Rui P. Martins

J. Semicond. 2020, 41(11): 111405

doi: 10.1088/1674-4926/41/11/111405

Full Text

6.

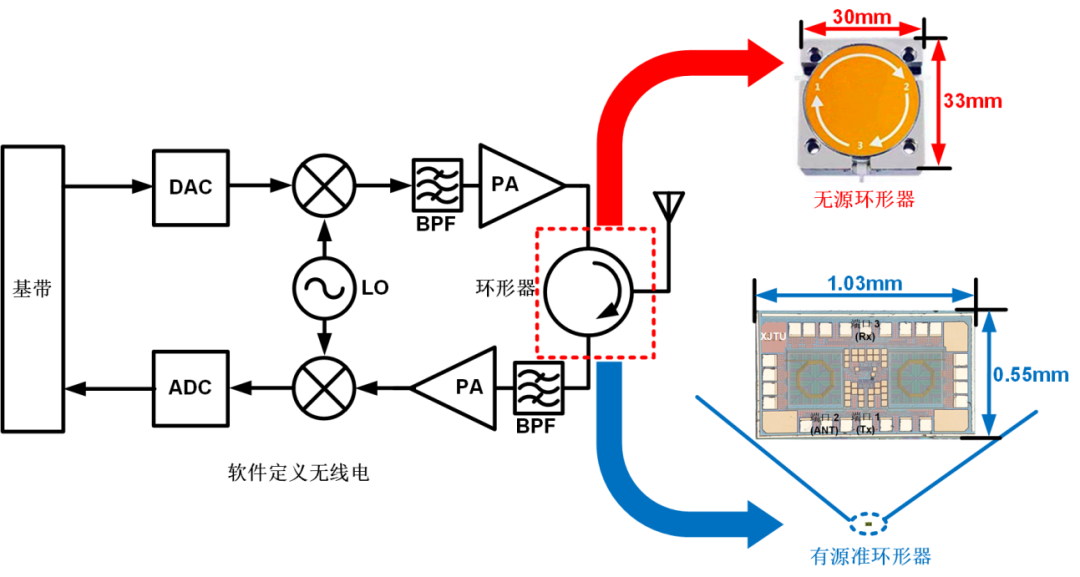

有源準環形器研究

移動電子產品對高速數據需求的日益增長促使通信電路與系統必須具有更寬的帶寬和更高的數據傳輸速率。多頻帶無線通信系統由于能夠以更高數據速率實現大數據傳輸,在現代通信系統中得到了廣泛應用。環形器作為三端口非互易元件通常用在射頻和微波系統中,實現發射信號與接收信號的隔離。環形器作為多頻帶無線通信系統的天線接口模塊,應具有在多個頻率下工作的能力,即具有在寬帶下工作的能力,同時還需要提高發射端至接收端的高隔離度,以降低發射信號對接收信號的干擾。傳統無源環形器通常基于鐵氧體設計,鐵氧體價格昂貴、體積大、難以集成,設計有源環形器可以提高通信系統的集成度,減小體積和價格。有源準環形器是有源環形器的一種,不存在接收端至發射端的傳輸路徑。目前有源環形器的研究主要集中在有源準環形器上,已有的研究成果多為窄帶有源準環形器,在寬帶上實現發射端至接收端的高隔離度是有源準環形器的設計難點之一。

為了突破有源準環形器寬帶和高隔離度不可兼得的瓶頸,西安交通大學耿莉教授課題組的唐炳俊博士提出并設計實現了反饋結構、雙路結構和改進型雙路結構有源準環形器。首先,在基本的有源環形器結構上增加負反饋通路,設計的負反饋有源準環形器的帶寬達到了6 GHz,隔離度提高至27 dB。為了進一步提高隔離度、降低插損,課題組又提出了雙路有源準環形器結構,增加了一條與已有抵消路徑結構一致的抵消路徑,該結構不僅拓寬了有源準環形器的寬帶、提高了隔離度,同時也提升了工藝、電壓及溫度(PVT)魯棒性。

芯片測試結果表明,隔離度相較于反饋結構提升了9 dB,而插入損耗降低了3 dB。隨后,進一步將應用于低噪聲放大器的噪聲抵消技術運用到有源準環形器的設計中,降低了噪聲,同時,加入了對稱隔離緩沖器,有效降低了插入損耗。芯片測試結果表明,在隔離度保持不變的情況下,該有源準環形器的插入損耗比雙路結構降低了6 dB,噪聲系數降低了8 dB,工作帶寬提升了1 GHz。三款有源準環形器分別在國際會議IEEE國際無線會議 (IWS)和國際期刊IEEE微波和無線元件通訊(MWCL)上發表,同時申請了國家發明專利。

有源環形器芯片的開發和應用將進一步減小通信系統的體積和成本。開發具有我國自主知識產權、面向5G和多頻帶無線通信應用的有源環形器芯片,對提高我國通信產品的競爭力具有重要的意義。

A survey of active quasi-circulators

Bingjun Tang, Li Geng

J. Semicond. 2020, 41(11): 111406

doi: 10.1088/1674-4926/41/11/111406

Full Text

7.

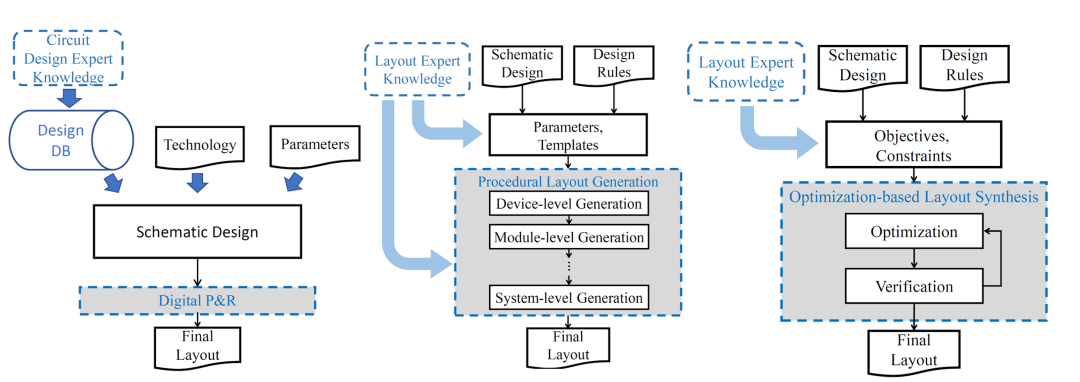

全自動模擬版圖設計面臨的挑戰和機遇

近年來,隨著包含物聯網、5G通信、智能計算、醫療電子等各種新興應用的快速成長,市場對模擬集成電路的需求也在快速增加。在模擬集成電路設計中,后端版圖一直是手動繁瑣、耗時且易出錯的工作。由于日趨復雜的設計規則,這個趨勢在先進工藝中尤為明顯,極大限制了芯片開發速度。盡管近年來,科研工作者在模擬集成電路版圖自動化領域不斷努力,但受限于模擬電路本身的復雜性,其與數字后端設計輔助相比仍有很大的差距。模擬電路涉及較多特定的電路類別,并往往需要對每種架構進行針對性優化。此外,模擬版圖對信號耦合、整體布局和工藝變化較為敏感。電路性能可能會因版圖實現中的微小變化而顯著下降。此外,學術界目前尚缺能夠有效模擬版圖對性能的影響的方法。這些都對模擬版圖自動化設計提出了重大挑戰。

德州大學奧斯汀分校David Z. Pan課題組概述了當前的模擬/混合信號集成電路版圖設計自動化方法,研究趨勢以及模擬版圖自動化的新愿景。文中首先回顧了三種主流的模擬集成電路布局布線方法和相關框架,包括可綜合模擬電路設計、基于過程的布局布線技術、和基于優化的版圖自動設計方法;然后介紹了學術界的一些最新進展,重點包括具有機器學習和統計功能的算法;最后在文中對未來EDA開發中的開放性問題和趨勢提出了看法。

文章介紹到,隨著開源EDA軟件社區的成熟與機器學習算法的進步,最近幾年來,模擬電路版圖自動化領域取得了快速的進步。其中,以德州大學的MAGICAL、加州大學的BAG和明尼蘇達大學的ALIGN為代表,開源模擬電路版圖自動化已經成功證明了自身能夠做到較為復雜的模擬、數字混合信號集成電路系統的版圖設計。文章還著重展望了今后幾年此領域的研究重點和挑戰。文章指出,通過流片與測量驗證,將會是將學術界研究轉換為工業實際工具的重要一步。

Challenges and opportunities toward fully automated analog layout design

Hao Chen, Mingjie Liu, Xiyuan Tang, Keren Zhu, Nan Sun, David Z. Pan

J. Semicond. 2020, 41(11): 111407

doi: 10.1088/1674-4926/41/11/111407

Full Text

研究論文

1.

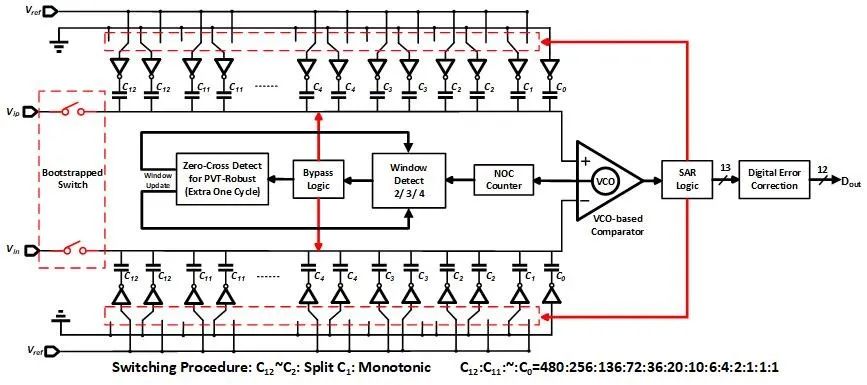

基于VCO比較器振蕩數的自適應多旁路窗在SAR ADC中的應用

模數轉換器(ADC)是模擬集成電路的核心問題之一,也是我國“卡脖子”的重大需求領域。近年來,逐次逼近(SAR)型ADC由于其高度數字化、功耗低、可并行等特點,在先進工藝下得到了長足的發展,并在高速領域逐步取得明顯的優勢。但受制于器件匹配,SAR ADC的高精度設計一直是個難題。而低功耗、低延遲、中高精度的ADC在傳感器和自動控制系統中扮演著不可或缺的角色。

隨著半導體工藝技術的發展,先進CMOS 工藝的特征尺寸與最大供電電壓均在逐年下降。數字電路在功耗和工作速度方面相對較模擬電路在先進CMOS 工藝中獲得了非常大的優勢。對于模擬電路來說,特征尺寸的減小會導致CMOS 管的本征增益降低,低電壓會帶來噪聲與電壓裕度問題。

因此數字化模擬電路成為了一個熱門的研究領域。因為比較器是電荷重分配SAR ADC 系統中唯一的模擬電路,所以將電壓域的比較器替換成時間域的電路就能實現SAR ADC 的數字化。VCO比較器可以將電壓差異轉化為時間差異,如果輸入信號電壓差較大,則基于VCO 的比較器僅需要消耗少量的能量就能得出比較結果;如果輸入信號電壓差較小,則該比較器可以實現低噪聲的性能。基于VCO 的比較器在得出比較結果的時候,其所需要消耗的振蕩周期數與輸入信號的電壓范圍有一定的關系。

電子科技大學低功耗集成電路與系統研究所李強教授團隊首先利用隨機過程理論對VCO比較器的噪聲特性進行了理論分析,得到閉環VCO比較器行為的解析解,發現VCO比較器會因為噪聲原因而在沒有達到足夠多的振蕩次數之前停止振蕩,會降低比較器的噪聲性能。VCO比較器每一個不同的振蕩次數均對應一個不同的電壓范圍,但此對應關系對PVT敏感,自適應旁路窗技術則是通過窗寬度檢測技術得到在PVT變化的情況下的合適的旁路窗,使系統可以跳過正確的逐次逼近周期數。在較高速的高精度ADC中,參考電壓的變化會導致錯誤的輸出,為了避免使用過大面積的片上去耦電容來穩定參考源,論文提出一種用于旁路窗邏輯的分裂-重組冗余算法來糾正錯誤的結果。

本論文展示了一款12-bit 30-MS/s的SAR ADC,使用40nm CMOS工藝進行了仿真,在30MS/s 采樣率、1.1V 供電電壓以及tt corner 下的總功耗為0.38W,SFDR 達到85.35dB,ENOB 為11.12 位,品質因子為5.69 fJ/conversion-step。該項工作證明自適應旁路窗邏輯和用于旁路窗邏輯的分裂-重組冗余算法這兩種技術都可以有效降低電路功耗和提高電路速度。未來還可以深度挖掘振蕩信息,進一步提高ADC 的動態性能,比如利用一些統計學方法得到的ENOB 甚至可以超過ADC 本身的分辨率,但這就需要對VCO-based 比較器的原理比如相位噪聲等進行更深刻的分析。

A 12-bit 30-MS/s VCO-based SAR ADC with NOC-assisted multiple adaptive bypass windows

Xiangxin Pan, Xiong Zhou, Sheng Chang, Zhaoming Ding, Qiang Li

J. Semicond. 2020, 41(11): 112401

doi: 10.1088/1674-4926/41/11/112401

Full Text

2.

隨著對高性能計算不斷增長的需求,現代微處理器的電流消耗和電流變化速率都大大增加。由于負載變化而引起的大而快速的電流變化會導致大的電源電壓下降,從而導致處理器嚴重的性能下降甚至停止工作。為了緩解該問題,向處理器供電的DC-DC轉換器應具有快速的瞬態響應,以便減少輸出電壓降低的幅度和持續時間。

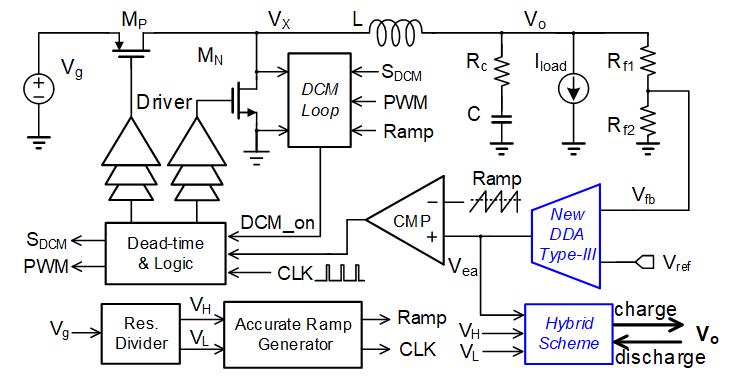

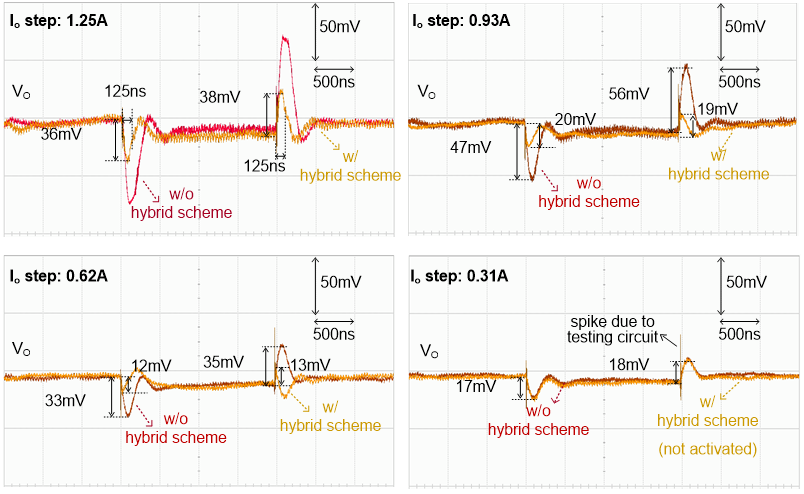

中國科學技術大學程林教授課題組提出了一種快速負載瞬態響應的補償器,使得即使使用簡單的電壓型 PWM 控制模式,也可以將轉換器的瞬態響應速度提高到接近理論上的最快速度,顯著降低了電路的復雜度;同時在此補償器基礎上提出了一種數字線性調整器(digital linear regulator)輔助的混合控制模式(hybrid scheme),利用該技術設計了一款Buck DC-DC芯片,測試結果顯示了其瞬態響應性能得到進一步的顯著提高,取得了125ns/1.25A的瞬態跳變響應速度。

本文所提出的快速瞬態響應技術可以廣泛應用于各種高頻DC-DC轉換器,能有效提高轉換器的負載瞬態響應速度。

圖1. 本文設計的Buck DC-DC轉換器系統框圖。

圖2. 負載瞬態響應測試圖。

Fast-transient techniques for high-frequency DC–DC converters

Lin Cheng, Kui Tang, Wang-Hung Ki, Feng Su

J. Semicond. 2020, 41(11): 112402

doi: 10.1088/1674-4926/41/11/112402

Full Text

責任編輯:xj

原文標題:半導體學報2020年第11期——模擬和數模混合集成電路專刊

文章出處:【微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

-

模擬

+關注

關注

7文章

1422瀏覽量

83897 -

雷達信號

+關注

關注

3文章

65瀏覽量

17291 -

數模混合

+關注

關注

0文章

19瀏覽量

9267

原文標題:半導體學報2020年第11期——模擬和數模混合集成電路專刊

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

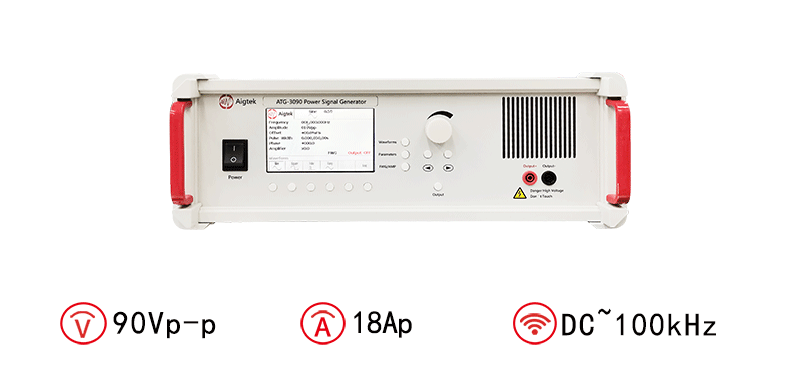

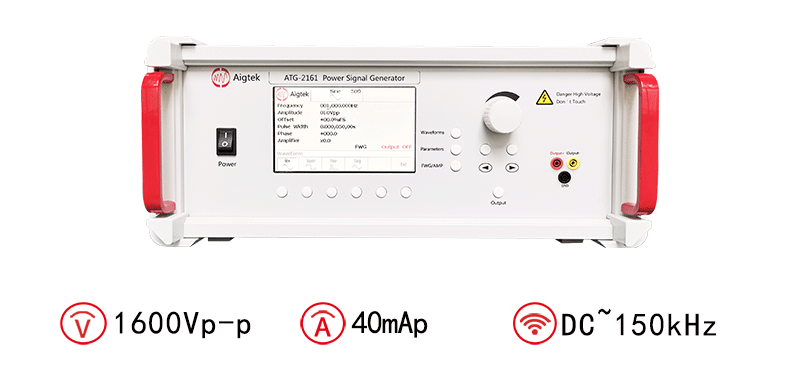

ATG-309功率信號源的使用范圍有哪些

ATG-3080功率信號源:信號源原理介紹

Aigtek:功率信號源是什么東西

Aigtek功率信號源的特點有哪些

安泰ATG-3090功率信號源的輸出信號是什么意思

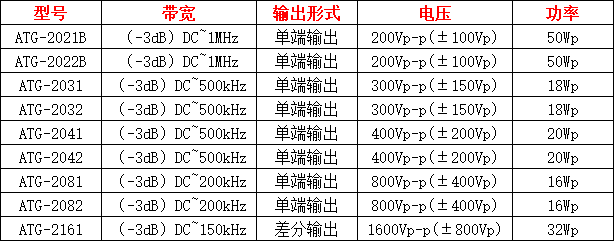

安泰ATG-2161功率信號源使用技巧有哪些內容

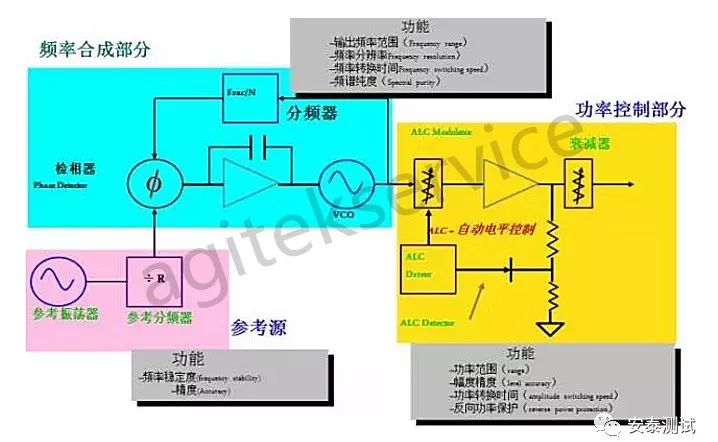

傻傻分不清?射頻模擬信號源和矢量信號源的區別

射頻信號源的LF源與AM調制信號源是如何調試的呢?

功率信號源是什么意思

功率信號源指標參數有哪些

硅基調頻連續波雷達信號源技術綜述

硅基調頻連續波雷達信號源技術綜述

評論