電子發燒友報道(文/程文智)以前,摩爾定律是半導體產業的指南針,每兩年在同樣面積芯片上的晶體管數量就會翻一番。但現在,先進工藝走到5nm后,已經越來越難把更多的晶體管微縮,放到同樣面積的芯片上,因此先進廠商除了繼續推進摩爾定律外,也需要思考其他的方式來制造更高效能的半導體芯片。

此時,先進封裝技術就變成了一個重要的領域,成為了半導體先進工藝領導廠商的最新戰場。業內人士普遍預測未來10到20年,集成電路將主要通過異質結構系統集成來提升芯片密度和性能,實現功耗的降低和集成更多的功能。世界前三大先進工藝廠商已經率先布局,臺積電、三星電子和英特爾都提出了相應的先進封裝技術。

先進封裝的市場規模

據市場調研機構Yole Development在今年9月份發布的報告顯示,2019年整個IC封裝市場的規模為680億美元,其中先進封裝的市場規模為290億美元,占了42.6%。同時,Yole還預測,2019年~2025年,先進封裝的市場規模將會以6.6%的年復合增長率持續增長,到2025年將會達到420億美元。

圖1:2019年~2025年芯片封裝技術市場規模預測。(數據來源:Yole)

而且,Yole還在報告中表示,由于摩爾定律放緩和異構集成,以及包括5G、AI、HPC和IoT在內應用的推動,先進封裝的發展勢頭不可阻擋,預計到2025年,先進封裝的市場規模將會占整個IC封裝市場規模的一半。

Yole的分析師Santosh Kumar補充說,2020年由于新冠疫情的影響,其實先進封裝的市場規模并沒有如預期的增長,而是下滑了7%左右,傳統封裝市場規模下滑了15%。不過,他同時強調,2020年的下滑是意外事件,2021年應該會重拾升勢。

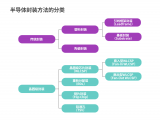

先進封裝主要是指采用了非引線鍵合技術的封裝,主要有Fan-out、Flip-Chip、Fan-in WLP、2.5D、3D封裝,以及埋入式等封裝技術。在先進封裝中,不同的技術增長率也有所不同,其中3D封裝年復合增長率最為快速,為25%。

另據中國半導體協會統計,2019年,中國大陸封測企業數量已經超過了120家,自2012年至2018年,封裝測試業的市場規模從2012年的1034億元,增長至2018年的2196億元,復合增速為13.38%。2020年上半年我國集成電路產業銷售額為3539億元,同比增長16.1%。其中封裝測試業銷售額1082.4億元,同比增長5.9%。

長電科技中國區研發中心副總經理李宗懌在最近的一次演講中表示,近年來先進封裝的發展是大勢所趨,一是智能系統的集成在封裝上是趨勢;二是多種先進封裝技術的混合或混搭是近幾年的熱點;三是封裝在向小、輕、薄方向發展;四是受AI/HPC的推動,其后期組裝的大顆Flip-Chip封裝產品不是在向小方向發展,而是越來越大,預計2020年后的未來3年內很有可能出現100×100mm的尺寸規模。

也正是在這個大趨勢下,半導體行業各大廠商競相投資布局,一場先進封裝技術競賽已然拉開了帷幕。

各大廠商的先進封裝近況

臺積電方面,在封裝技術上陸續推出 2.5D的高端封裝技術 CoWoS(Chip-on-Wafer-on-Substrate),以及經濟型的扇出型晶圓InFO( Integrated Fan-out )等先進封裝技術后,2020年8月,在其線上技術研討會上,臺積電副總裁余振華宣布推出3DFabric整合技術平臺,其中包括了前端封裝技術(SoIC技術和CoW、WoW兩種鍵合方式)和后端封裝技術(CoWoS和InFO系列封裝技術)。

3DFabric可將各種邏輯、存儲器件或專用芯片與SoC集成在一起,為高性能計算機、智能手機、IoT邊緣設備等應用提供更小尺寸的芯片,并且可通過將高密度互連芯片集成到封裝模塊中,從而提高帶寬、延遲和電源效率。

這帶來的好處是:客戶可以在模擬IO、射頻等不經常更改、擴展性不大的模塊上采用更成熟、更低成本的半導體技術,在核心邏輯設計上采用最先進的半導體技術,既節約了成本,又縮短了新產品的上市時間。臺積電認為,芯片在2D層面的微縮已不能滿足異構集成的需求,3D才是未來提升系統效能、縮小芯片面積、整合不同功能的發展趨勢。

在11月份,臺積電開始與Google和AMD等廠商一同測試,合作開發先進的3D堆棧晶圓級封裝產品,并計劃2022年進入量產。

臺積電將此3D堆棧技術命名為“SoIC封裝”,可以垂直與水平的進行芯片鏈接及堆棧封裝。此技術可以讓幾種不同類型的芯片,比如處理器、內存與傳感器堆棧到同一個封裝中。這種技術能可讓芯片組功能更強大,但尺寸更小,且具有更高能效。

據了解,臺積電正在興建中的苗栗竹南廠將采用這種3D堆棧技術。而 Google 和 AMD 將成為 SoIC 芯片的首批客戶。這兩家客戶正協助臺積電進行 3D堆棧技術的測試及驗證。苗栗竹南廠預定明年完工,2022 年開始進入量產。

據消息人士透露,Google所采用的SoIC芯片將計劃用在自動駕駛及其他的應用領域。AMD則希望通過3D堆棧技術打造出性能超越英特爾的芯片產品。

英特爾方面,2017年,推出了EMIB(Embedded Multi-Die Interconnect Bridge,嵌入式多芯片互連橋接)封裝技術,可將不同類型、不同工藝的芯片IP靈活地組合在一起,類似一個松散的SoC。2018年12月,英特爾再推出Foveros 3D堆疊封裝技術,可以通過在水平布置的芯片之上垂直安置更多面積更小、功能更簡單的小芯片來讓方案整體具備更完整的功能。

2019年7月, 英特爾在SEMICON West 大會上分享了三項全新先進封裝技術技術,Co-EMIB、全方位互連技術ODI(Omni-Directional Interconnect)、全新裸片間接口技術MDIO。Co-EMIB可以理解為EMIB和Foveros兩項技術的結合,在水平物理層互連和垂直互連的同時,實現Foveros 3D堆疊之間的水平互連。

2020年8月,英特爾在其2020年架構日中,展示了其在3D封裝技術領域中的新進展,英特爾稱其為“混合結合(Hybrid bonding)”技術。

據介紹,混合結合技術能夠加速實現10微米及以下的凸點間距(Pitch),提供更高的互連密度、更小更簡單的電路、更大的帶寬、更低的電容、更低的功耗(每比特不到0.05皮焦耳)。

Intel目前的3D Foveros立體封裝技術,可以實現50微米左右的凸點間距,每平方毫米集成大約400個凸點,而應用新的混合結合技術,不但凸點間距能縮小到1/5,每平方毫米的凸點數量也能超過1萬,增加足足25倍。

采用混合結合封裝技術的測試芯片已在2020年第二季度流片,但是Intel沒有披露未來會在什么產品上商用。

三星電子方面,2015年在丟失蘋果iPhone處理器代工訂單后,三星電子成立了特別工作小組,目標開發先進封裝FOPLP技術。2018年,三星電子FOPLP技術實現商用,應用于其自家智能手表Galaxy Watch的處理器封裝應用中。

2019年10月,三星電子宣布已率先開發出12層3D-TSV技術。三星電子方面表示,這是大規模生產高性能芯片的最具挑戰性的封裝技術之一,該技術可垂直堆疊12個DRAM芯片,它們通過60000個TSV互連,每一層的厚度僅有頭發絲的1/20。

2020年8月,三星電子宣布其采用3D封裝技術的7納米半導體的試制取得成功。該公司高管表示“如果利用3D這種創新,就能夠跨越半導體的極限”。

三星電子將這種3D封裝技術命名為“X-Cube”,全稱是eXtended-Cube,意為拓展的立方體。在Die之間的互聯上面,它使用的是成熟的TSV工藝,即硅穿孔工藝。使用X-Cube可以將不同芯片搭積木一樣堆疊起來,三星電子表示,該技術目前已經可以用于7nm及5nm工藝。

此外,三星已經完成“2.5D RDL”的開發,還計劃在2021年底啟動I-Cube 8X”技術,在5厘米寬、5厘米長芯片上放置8個HGM和邏輯部件,以及結合X-Cube和I-Cube優勢的“X/I Cube”技術。為了使封裝服務多樣化,三星已將世界第二大后端加工公司Amco列入其代工合作伙伴名單。

除了臺積電、英特爾和三星電子擁有先進封裝技術之外,存儲器廠商美光也在開始自建封測產線、中芯國際在與長電科技合作投建封測廠中芯長電主攻先進封裝、日月光、安靠、長電科技、通富微電,以及天水華天等封測廠商也都緊隨其后,不斷發力先進封裝技術。

圖:長電科技的SiP產品線發展路線圖。

比如長電科技在先進封裝上布局非常全面,目前封裝業務主要以先進封裝為主,占封裝業務的93.74%,長電先進、長電韓國以及星科金朋為主要工廠。長電先進具備FC、PoP、Fan-out、WLP、2.5D/3D等先進封裝的能力;星科金朋新加坡廠擁有Fan-out eWLB和WLCSP封裝能力,韓國廠擁有SiP和FC系統封測能力,江陰廠擁有先進的存儲器封裝、全系列的FC倒裝技術;長電韓國主營SiP高端封裝業務。

結語

目前不僅全球領先的半導體代工廠擁有3D或2.5D的先進封裝技術,封測廠商也在發力先進封裝技術。目前進入先進封裝領域的廠商基本上都是頭部的半導體企業,隨著技術的發展未來將會有更多的廠商加入,競爭才剛剛開始。

本文由電子發燒友原創,未經授權請勿轉載。

-

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

IC封裝

+關注

關注

4文章

185瀏覽量

26697

發布評論請先 登錄

相關推薦

人工智能半導體及先進封裝技術發展趨勢

半導體封裝技術的類型和區別

led封裝和半導體封裝的區別

半導體先進封裝技術

中國大陸先進封裝半導體供應鏈崛起

英特爾實現先進半導體封裝技術芯片的大規模生產

傳統封裝和先進封裝的區別

來elexcon半導體展,看「先進封裝」重塑產業鏈

先進封裝:半導體廠商的新戰場

先進封裝:半導體廠商的新戰場

評論