CMOS是生活中的常用器件,為增進(jìn)大家對(duì)CMOS的了解程度,本文將對(duì)CMOS集成電路的測(cè)試、CMOS集成電路的保護(hù)措施、CMOS電路焊接注意事項(xiàng)、CMOS數(shù)字集成電路的特點(diǎn)等內(nèi)容加以介紹。如果你對(duì)CMOS相關(guān)內(nèi)容具有興趣,不妨繼續(xù)往下閱讀哦。

一、CMOS電路焊接注意事項(xiàng)

為了避免由于靜電感應(yīng)而損壞電路,焊接CMOS集成電路所使用的電烙鐵必需良好接地,焊接時(shí)間不得超過(guò)5秒。最好使用20~25W內(nèi)熱式電烙鐵和502環(huán)氧助焊劑,必要時(shí)可使用插座。

在接通電源的情況下,不應(yīng)裝拆CMOS集成電路。凡是與CMOS集成電路接觸的工序,使用的工作臺(tái)及地板嚴(yán)禁鋪墊高絕緣的板材(如橡膠板、玻璃板、有機(jī)玻璃、膠木板等),應(yīng)在工作臺(tái)上鋪放嚴(yán)格接地的細(xì)鋼絲網(wǎng)或銅絲網(wǎng),并經(jīng)常檢查接地可靠性。

二、CMOS集成電路的測(cè)試

測(cè)試時(shí)所有CMOS集成電路的儀器、儀表均應(yīng)良好接地。如果是低阻信號(hào)源,應(yīng)保證輸入信號(hào)不超過(guò)CMOS集成電路的電源電壓范圍(CXXX系列為7~15V,C4000系列為3~18V),既VSS≤Vi≤VDD。如果輸入信號(hào)一定要超過(guò)CMOS集成電路的電源電壓范圍,則應(yīng)在輸入端加一個(gè)限流電阻,使輸入電流不超過(guò)5mA,以避免CMOS集成電路內(nèi)部的保護(hù)二極管燒毀。

若信號(hào)源和CMOS集成電路用兩組電源,開(kāi)機(jī)時(shí),應(yīng)先接同CMOS集成電路電源,后接通信號(hào)源電源。關(guān)機(jī)時(shí),應(yīng)先關(guān)信號(hào)源電源,后關(guān)CMOS集成電路電源。

三、CMOS集成電路的保護(hù)措施

因?yàn)镃MOS集成電路輸入阻抗極高,隨機(jī)的靜電積累很可能使電路引出端任意兩端的電壓超過(guò)MOS管柵擊穿電壓,從而引起電路損壞。所以,CMOS集成電路不用時(shí)應(yīng)把電路的外引線全部短路,或放在導(dǎo)電的屏蔽容器內(nèi),以防被靜電擊穿。

CMOS集成電路的互換。在使用中有些CMOS集成電路是可以直接換用。如國(guó)產(chǎn)CC4000可與國(guó)外產(chǎn)品CD4000、MC14000系列直接代換。

對(duì)于那些管腳排列和封裝形式完全一致,但電參數(shù)有所不同的CMOS集成電路,換用時(shí)要十分注意。如國(guó)產(chǎn)CC4000和CXXX中有些品種,它們的工作電壓有所差異,CC4000為3~18V、CXXX為7~15V。換用時(shí)要考慮到電源供電及負(fù)載能力問(wèn)題。另外,對(duì)于那些封裝形式及管腳排列不同的CMOS集成電路,一般不能直接代換。如果需要換用,則應(yīng)做一些相應(yīng)的變換使兩者功能相同的引出端一一對(duì)應(yīng)。

焊CMOS集成塊。先找一塊比集成塊稍大的鋁箔和一塊平整的泡沫塑料。鋁箔平放在塑料泡沫上,將CMOS集成塊垂直插入泡沫塑料后隨即拔起,使鋁箔附在集成塊上以使引腳全部短路。然后將集成塊插入線路板的規(guī)定位置,像焊其它集成塊那樣焊接,焊好后撕去鋁箔即可。

四、CMOS電路焊接注意事項(xiàng)

CMOS集成電路由于輸入電阻很高,因此極易接受靜電電荷。為了防止產(chǎn)生靜電擊穿,生產(chǎn)CMOS時(shí),在輸入端都要加上標(biāo)準(zhǔn)保護(hù)電路,但這并不能保證絕對(duì)安全,因此使用CMOS集成電路時(shí),必須采取以下預(yù)防措施。

①存放CMOS集成電路時(shí)要屏蔽,一般放在金屬容器中,也可以用金屬箔將引腳短路。

②CMOS集成電路可以在很寬的電源電壓范圍內(nèi)提供正常的邏輯功能,但電源的上限電壓(即使是瞬態(tài)電壓)不得超過(guò)電路允許極限值、…電源的下限電壓(即使是瞬態(tài)電壓)不得低于系統(tǒng)工作所必需的電源電壓最低值Vmin,更不得低于VSS。

③焊接CMOS集成電路時(shí),一般用20W內(nèi)熱式電烙鐵,而且烙鐵要有良好的接地線。也可以利用電烙鐵斷電后的余熱快速焊接。禁止在電路通電的情況下焊接。

④為了防止輸入端保護(hù)二極管因正向偏置而引起損壞,輸入電壓必須處在VDD 和VSS之間,即VSS

⑤調(diào)試CMOS電路時(shí),如果信號(hào)電源和電路板用兩組電源,則剛開(kāi)機(jī)時(shí)應(yīng)先接通電路板電源,后開(kāi)信號(hào)源電源。關(guān)機(jī)時(shí)則應(yīng)先關(guān)信號(hào)源電源,后斷電路板電源。即在CMOS本身還沒(méi)有接通電源的情況下,不允許有輸入信號(hào)輸入。

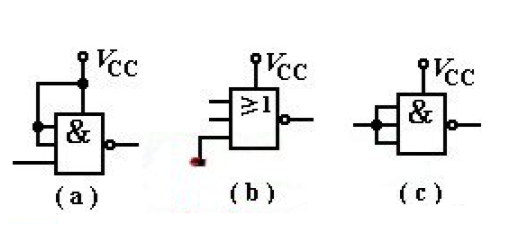

⑥ 多余輸入端絕對(duì)不能懸空。否則不但容易受外界噪聲干擾,而且輸入電位不定,破壞了正常的邏輯關(guān)系,也消耗不少的功率。因此,應(yīng)根據(jù)電路的邏輯功能需要分別情況加以處理。例如:與門和與非門的多余輸入端應(yīng)接到VDD或高電平;或門和或非門的多余輸入端應(yīng)接到VSS或低電平;如果電路的工作速度不高,不需要特別考慮功耗時(shí),也可以將多余的輸入端和使用端并聯(lián)。如上圖所示。

以上所說(shuō)的多余輸入端,包括沒(méi)有被使用但已接通電源的CMOS電路所有輸入端。例如,一片集成電路上有4個(gè)與門,電路中只用其中一個(gè),其它三個(gè)門的所有輸入端必須按多余輸入端處理。

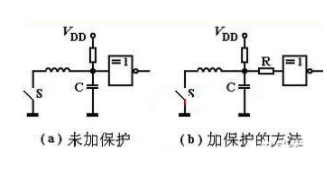

⑦輸入端連接長(zhǎng)線時(shí),由于分布電容和分布電感的影響,容易構(gòu)成LC振蕩,可能使輸入保護(hù)二極管損壞,因此必須在輸入端串接一個(gè)10~20kΩ的保護(hù)電阻R,如上圖所示。

⑧CMOS電路裝在印刷電路板上時(shí),印刷電路板上總有輸入端,當(dāng)電路從機(jī)器中拔出時(shí),輸入端必然出現(xiàn)懸空,所以應(yīng)在各輸入端上接入限流保護(hù)電阻,如圖T309所示。如果要在印刷電路板上安裝CMOS集成電路,則必須在與它有關(guān)的其它元件安裝之后再裝CMOS電路,避免CMOS器件輸入端懸空。

⑨插拔電路板電源插頭時(shí),應(yīng)該注意先切斷電源,防止在插拔過(guò)程中燒壞CMOS的輸入端保護(hù)二極管。

五、CMOS數(shù)字集成電路的特點(diǎn)

1.靜態(tài)功耗低:電源電壓VDD=5V的中規(guī)模電路的靜態(tài)功耗小于100μW,從而有利于提高集成度和封裝密度,降低成本,減小電源功耗。

2.電源電壓范圍寬:4000系列CMOS電路的電源電壓范圍為3~18V,從而使選擇電源的余地大,電源設(shè)計(jì)要求低。

3.輸入阻抗高:正常工作的CMOS集成電路,其輸入端保護(hù)二極管處于反偏狀態(tài),直流輸入阻抗可大于100MΩ,在工作頻率較高時(shí),應(yīng)考慮輸入電容的影響。

4. 扇出能力強(qiáng):在低頻工作時(shí),一個(gè)輸出端可驅(qū)動(dòng)50個(gè)以上的CMOS器件的輸入端,這主要因?yàn)镃MOS器件的輸入電阻高的緣故。

5.抗干擾能力強(qiáng):CMOS集成電路的電壓噪聲容限可達(dá)電源電壓的45%,而且高電平和低電平的噪聲容限值基本相等。

6.邏輯擺幅大:空載時(shí),輸出高電平VOH》VDD-0.05V,輸出低電平VOL

7. CMOS集成電路還有較好的溫度穩(wěn)定性和較強(qiáng)的抗輻射能力。

不足之處是,一般CMOS器件的工作速度比TTL集成電路低,功耗隨工作頻率的升高而顯著增大。

六、CMOS數(shù)字集成電路使用注意事項(xiàng)

1.電源連接和選擇:VDD端接電源正極,VSS端接電源負(fù)極(地)。絕對(duì)不許接錯(cuò),否則器件因電流過(guò)大而損壞。對(duì)于電源電壓范圍為3V~18V系列器件。如CC4000系列,實(shí)驗(yàn)中VDD通常接+5V電源,VDD電壓選在電源變化范圍的中間值,例如電源電壓在8~12V之間變化,則選擇VDD=10V較恰當(dāng)。

注意:CMOS器件在不同的VDD值下工作時(shí),其輸出阻抗、工作速度和功耗等參數(shù)都有所變化,設(shè)計(jì)中須考慮。

2.輸入端處理:多余輸入端不能懸空。應(yīng)按邏輯要求接VDD或接VSS,以免受干擾造成邏輯混亂,甚至還會(huì)損壞器件。對(duì)于工作速度要求不高,,而要求增加帶負(fù)載能力時(shí),可把輸入端并聯(lián)使用。

對(duì)于安裝在印刷電路板上的CMOS器件,為了避免輸入端懸空,在電路板的輸入端應(yīng)接入限流電阻RP和保護(hù)電阻R,當(dāng)VDD=+5V時(shí),RP取5.1KΩ,R一般取100KΩ~1MΩ。

3.輸出端處理:輸出端不允許直接接VDD或VSS,否則將導(dǎo)致器件損壞,除三態(tài)(TS)器件外,不允許兩個(gè)不同芯片輸出端并聯(lián)使用,但有時(shí)為了增加驅(qū)動(dòng)能力,同一芯片上的輸出端可以并聯(lián)。

4.對(duì)輸入信號(hào)VI的要求:VI的高電平VIH

5.CMOS器件的輸入端和VSS之間接有保護(hù)二極管,除了電平變換器等一些接口電路外,輸入端和正電源VDD之間也接有保護(hù)二極管,因此,在正常運(yùn)轉(zhuǎn)和焊接CMOS器件時(shí),一般不會(huì)因感應(yīng)電荷而損壞器件。但是,在使用CMOS數(shù)字集成電路時(shí),輸入信號(hào)的低電平不能低于(VSS-0.5V),除某些接口電路外,輸入信號(hào)的高電平不得高于(VDD+0.5V),否則可能引起保護(hù)二極管導(dǎo)通,甚至損壞進(jìn)而可能使輸入級(jí)損壞。

-

集成電路

+關(guān)注

關(guān)注

5381文章

11381瀏覽量

360849 -

CMOS

+關(guān)注

關(guān)注

58文章

5680瀏覽量

235136 -

MOS

+關(guān)注

關(guān)注

32文章

1245瀏覽量

93469

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字集成電路-電路、系統(tǒng)與設(shè)計(jì) 免費(fèi)下載

常用的數(shù)字集成電路簡(jiǎn)介

CMOS數(shù)字集成電路是什么?CMOS數(shù)字集成電路有什么特點(diǎn)?

數(shù)字集成電路設(shè)計(jì)教學(xué)大綱

數(shù)字集成電路簡(jiǎn)介

數(shù)字集成電路的類別

數(shù)字集成電路分類及特點(diǎn)

數(shù)字集成電路_什么是數(shù)字集成電路

數(shù)字集成電路版圖提取

CMOS數(shù)字集成電路:分析與設(shè)計(jì)(第3版)

CD4000系列CMOS數(shù)字集成電路芯片資料合集免費(fèi)下載

IC設(shè)計(jì)基礎(chǔ)教程之數(shù)字集成電路基本單元與版圖的詳細(xì)資料概述

CMOS數(shù)字集成電路的特點(diǎn)和資料詳細(xì)概述

CMOS數(shù)字集成電路的特點(diǎn)和資料詳細(xì)概述

評(píng)論