來自復旦大學微電子學院的消息,該校周鵬團隊針對具有重大需求的3-5納米節點晶體管技術,驗證了雙層溝道厚度分別為0.6 /1.2納米的圍柵多橋溝道晶體管(GAA,Gate All Around),實現了高驅動電流和低泄漏電流的融合統一,為高性能低功耗電子器件的發展提供了新的技術途徑。

相關成果以《0.6/1.2納米溝道厚度的高驅動低泄漏電流多橋溝道晶體管》(High Drive and Low Leakage Current MBC FET with Channel Thickness 1.2nm/0.6nm)為題在第66屆國際電子器件大會(IEDM,International Electron Device Meeting)上北京時間12月16日在線發布。IEDM是微電子器件領域的國際頂級會議,是國際學術界和頂尖半導體公司的研發人員發布先進技術和最新進展的重要窗口。

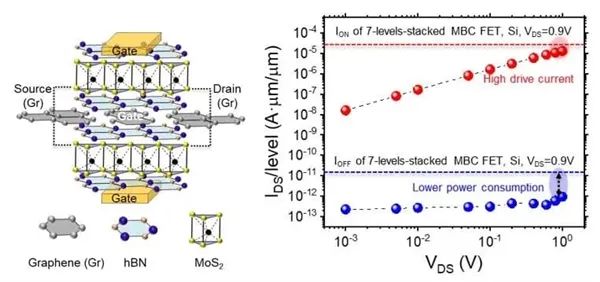

隨著集成電路制造工藝進入到5納米技術節點以下,傳統晶體管微縮提升性能難以為繼,技術面臨重大革新。采用多溝道堆疊和全面柵環繞的新型多橋溝道晶體管乘勢而起,利用GAA結構實現了更好的柵控能力和漏電控制,被視為3-5納米節點晶體管的主要候選技術。現有工藝已實現了7層硅納米片的GAA多橋溝道晶體管,大幅提高驅動電流,然而隨著堆疊溝道數量的增加,漏電流也隨之增加,導致的功耗不可忽視。

雙橋溝道晶體管示意圖及其性能圖

針對上述問題,團隊設計并制備出了超薄圍柵雙橋溝道晶體管,利用二維半導體材料優秀的遷移率,和圍柵增強作用的特點,驅動電流與普通MoS2晶體管相比提升超過400%,室溫下可達到理想的亞閾值擺幅(60mV/dec)。同時由于出色的靜電調控與較大的禁帶寬度,可有效降低漏電流。該器件驅動電流與7疊層硅GAA晶體管可相比擬,漏電流卻只有硅器件的1.9%,降低了兩個數量級,在未來高性能低功耗晶體管技術應用領域具有廣闊的應用前景。

該項研究工作主要由博士生黃曉合和劉春森完成,得到了微電子學院教授張衛的指導,獲得了國家自然科學基金杰出青年科學基金、應急重點項目及上海市集成電路重點專項等項目的資助,以及復旦大學專用集成電路與系統國家重點實驗室的支持。

責任編輯:xj

原文標題:3nm、5nm關鍵技術:復旦大學成功驗證實現GAA晶體管

文章出處:【微信公眾號:微波射頻網】歡迎添加關注!文章轉載請注明出處。

-

集成電路

+關注

關注

5382文章

11396瀏覽量

360955 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

5nm

+關注

關注

1文章

342瀏覽量

26054 -

3nm

+關注

關注

3文章

230瀏覽量

13965

原文標題:3nm、5nm關鍵技術:復旦大學成功驗證實現GAA晶體管

文章出處:【微信號:mwrfnet,微信公眾號:微波射頻網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰

臺積電產能爆棚:3nm與5nm工藝供不應求

AI芯片驅動臺積電Q3財報亮眼!3nm和5nm營收飆漲,毛利率高達57.8%

臺積電3nm制程需求激增,全年營收預期上調

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

消息稱臺積電3nm/5nm將漲價,終端產品或受影響

三星電子:加快2nm和3D半導體技術發展,共享技術信息與未來展望

臺積電3nm工藝迎來黃金期,蘋果等巨頭推動需求飆升

臺積電擴增3nm產能,部分5nm產能轉向該節點

低功耗 高性能M0芯片亮點(1~3): 低功耗 寬電壓 PWM (無須擔心耗電問題!)

3nm、5nm關鍵技術:為高性能低功耗電子器件發展提供新技術途徑

3nm、5nm關鍵技術:為高性能低功耗電子器件發展提供新技術途徑

評論