FinFET晶體管架構(gòu)是當今半導體行業(yè)的主力軍。但是,隨著器件的持續(xù)微縮,短溝道效應迫使業(yè)界引入新的晶體管架構(gòu)。在本文中,IMEC的3D混合微縮項目總監(jiān)Julien Ryckaert勾勒出了向2nm及以下技術(shù)節(jié)點發(fā)展的演進之路。在這條令人振奮的道路上,他介紹了Nanosheet晶體管,F(xiàn)orksheet器件和CFET。其中一部分內(nèi)容已在2019 IEEE國際電子器件會議(IEDM)上發(fā)表。

FinFET:今天最先進的晶體管

在每一代新技術(shù)上,芯片制造商都能夠?qū)⒕w管規(guī)格微縮0.7倍,從而實現(xiàn)15%的性能提升,50%的面積減小,40%的功耗降低以及35%的成本降低。幾年前,業(yè)界為了維持這種微縮路徑,從“老式”平面MOSFET過渡到FinFET晶體管架構(gòu)。在FinFET中,源極和漏極之間的溝道為fin的形式。柵極環(huán)繞該3D溝道,可從溝道的3個側(cè)面進行控制。這種多柵極結(jié)構(gòu)可以抑制在柵極長度降低時帶來的短溝道效應。

出色的短溝道控制能力至關(guān)重要,因為它奠定了器件微縮的基礎,允許更短的溝道長度和更低的工作電壓。

2012年,首款商用22nm FinFET面世。從那時起,F(xiàn)inFET體系結(jié)構(gòu)進行了持續(xù)的改進,以提高性能并減小面積。例如,F(xiàn)inFET的3D特性允許增加fin片高度,從而在相同的面積上獲得更高的器件驅(qū)動電流。如今,業(yè)界正在加快生產(chǎn)的10nm / 7nm芯片也是基于FinFET。在最先進的節(jié)點的標準單元大多是6T單元高度,也就是是每個器件最多擁有2根fin。

Nanosheet:器件進化第一步

但是,隨著工藝微縮至5nm節(jié)點,F(xiàn)inFET架構(gòu)可能不再是主流。在溝道長度小到一定值時,F(xiàn)inFET結(jié)構(gòu)又無法提供足夠的靜電控制。最重要的是,向低軌標準單元的演進需要向單fin器件過渡,即使fin高度進一步增加,單fin器件也無法提供足夠的驅(qū)動電流。

隨著技術(shù)節(jié)點的不斷變化,半導體行業(yè)并不急于轉(zhuǎn)向其他晶體管架構(gòu)。一些公司甚至可能決定在某些節(jié)點停留更長的時間。但是,仍然存在需要最新的“通用” CMOS解決方案的應用,例如機器學習,大數(shù)據(jù)分析和數(shù)據(jù)中心服務器。通過這種通用CMOS解決方案,可以在相同技術(shù)節(jié)點中使用相同的晶體管架構(gòu)來實現(xiàn)芯片上所有的功能。

在這里,Nanosheet可以來幫助解圍。Nanosheet可以被視為FinFET器件的自然演變版本。想象一下將FinFET的溝道水平切割成多個單獨Nanosheet溝道,柵極也會完全環(huán)繞溝道。與FinFET相比,Nanosheet的這種GAA特性提供了出色的溝道控制能力。同時,溝道在三維中的極佳分布使得單位面積的有效驅(qū)動電流得以優(yōu)化。

從FinFET到Nanosheet的自然演變。

需要微縮助推器

在6T和5T的低單元高度下,向Nanosheet器件的遷移變得最佳,因為在這種情況下,fin的減少會降低傳統(tǒng)基于FinFET的單元中的驅(qū)動電流。

但是,如果不引入結(jié)構(gòu)化微縮助推器(如埋入式電源軌和環(huán)繞式接觸),就無法將單元高度從6T減小到5T。

電源軌為芯片的不同組件提供電源,并且一般由BEOL中Mint和M1層提供。但是,它們在那里占據(jù)了很大的空間。在嵌入式電源軌結(jié)構(gòu)中,電源軌埋在芯片的前段,以幫助釋放互連的布線資源。此外,它們?yōu)椴捎霉?jié)距微縮而增加BEOL電阻的技術(shù)提供了較低的電阻局部電流分布。BEOL沒有電源軌后,可以將標準單元的高度從6T進一步降低到5T。

下一步:縮小p和n之間的間距

隨著走向更小的軌道高度的旅程的繼續(xù),單元高度的進一步減小將要求標準單元內(nèi)nFET和pFET器件之間的間距更小。但是,對于FinFET和Nanosheet而言,工藝限制了這些n和p器件之間的間距。例如,在FinFET架構(gòu)中,通常在n和p之間需要2個dummy fin的間距,這最多消耗總可用空間的40-50%。

為了擴大這些器件的可微縮性,IMEC最近提出了一種創(chuàng)新的架構(gòu),稱為Forksheet器件。Forksheet可以被認為是Nanosheet的自然延伸。

與Nanosheet相比,現(xiàn)在溝道由叉形柵極結(jié)構(gòu)控制,這是通過在柵極圖案化之前在p和nMOS器件之間引入“介電墻”來實現(xiàn)的。該墻將p柵溝槽與n柵溝槽物理隔離,從而允許更緊密的n到p間距。

從FinFET到Nanosheet再到Forksheet的自然演變。

用于制造Forksheet的工藝流程與用于制造Nanosheet的工藝流程相似,僅增加一些額外的工藝步驟。n和p之間的介電隔離還具有一些工藝優(yōu)勢,例如填充功函數(shù)金屬的工藝更簡化。在此基礎上,由于大幅減少了n到p的間距,預計該Forksheet具有更佳的面積和性能的可微縮性。

Forksheet工藝流程中的關(guān)鍵步驟,即有源區(qū)形成后“介電墻”的形成步驟。

-

半導體

+關(guān)注

關(guān)注

334文章

27033瀏覽量

216393 -

IC設計

+關(guān)注

關(guān)注

37文章

1292瀏覽量

103773 -

晶體管

+關(guān)注

關(guān)注

77文章

9637瀏覽量

137864

發(fā)布評論請先 登錄

相關(guān)推薦

分布式通信的原理和實現(xiàn)高效分布式通信背后的技術(shù)NVLink的演進

云數(shù)據(jù)庫“再進化”,OB Cloud如何打造云時代的數(shù)據(jù)底座?

探索手機震動馬達的種類與應用:技術(shù)演進與市場趨勢

應用驅(qū)動協(xié)議演進,擁抱智能創(chuàng)新技術(shù)

差壓表的技術(shù)演進與實際應用探討

藍牙傳輸技術(shù)的演進與發(fā)展

數(shù)字EDA賦能RISC-V落地演進技術(shù)研討會成功舉辦

華為CloudMSE引領(lǐng)Gi-LAN智能化演進,擁抱5.5G新時代

半導體發(fā)展的四個時代

半導體發(fā)展的四個時代

汽車激光雷達:競爭格局和技術(shù)演進

藍牙定位技術(shù):演進與廣泛應用

駕馭創(chuàng)造的力量: 生成式 AI 時代的 MLOps 演進

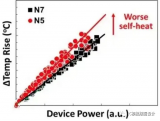

FinFET工藝之self-heating概念介紹

后FinFET時代的技術(shù)演進說明

后FinFET時代的技術(shù)演進說明

評論