在高速PCB設(shè)計(jì)中,“信號(hào)”始終是工程師無(wú)法繞開(kāi)的一個(gè)知識(shí)點(diǎn)。不管是在設(shè)計(jì)環(huán)節(jié),還是在測(cè)試環(huán)節(jié),信號(hào)質(zhì)量都值得關(guān)注。在本文中,我們主要來(lái)了解下影響信號(hào)質(zhì)量的5大問(wèn)題。

根據(jù)目前工作的結(jié)論,信號(hào)質(zhì)量常見(jiàn)的問(wèn)題主要表現(xiàn)在五個(gè)方面:過(guò)沖,回沖,毛刺,邊沿,電平。

01過(guò)沖

過(guò)沖圖

過(guò)沖帶來(lái)的問(wèn)題是容易造成器件損壞,過(guò)沖過(guò)大也容易對(duì)周?chē)男盘?hào)造成串?dāng)_。造成過(guò)沖大的原因是不匹配,消除的方法有始端串電阻或末端并阻抗(或電阻)。

02毛刺

毛刺圖

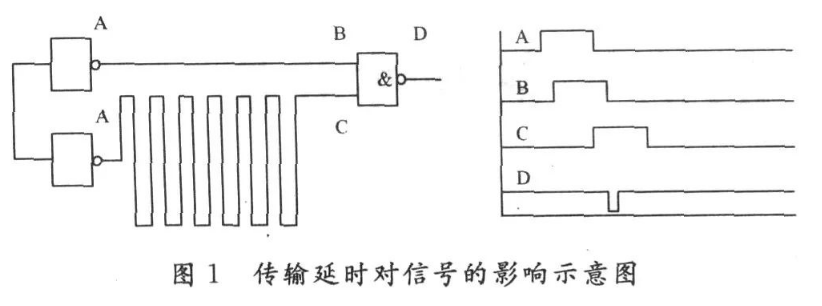

毛刺作用在高速器件上,容易造成誤觸發(fā)、控制信號(hào)控制錯(cuò)誤或時(shí)鐘信號(hào)相位發(fā)生錯(cuò)誤等問(wèn)題,毛刺脈沖帶來(lái)的問(wèn)題多發(fā)生在單板工作不穩(wěn)定或器件替代后出現(xiàn)問(wèn)題。造成毛刺的原因很多,比如邏輯冒險(xiǎn),串?dāng)_、地線反彈等,其消除的方法也不盡相同。

03邊沿

邊沿圖

邊沿速度緩慢發(fā)生在信號(hào)線上時(shí),會(huì)造成數(shù)據(jù)采樣錯(cuò)誤。其產(chǎn)生原因通常是輸出端容性負(fù)載過(guò)大(負(fù)載數(shù)量過(guò)多),輸出是三態(tài)時(shí)充(放)電電流小等原因。

審核編輯:符乾江

-

電平

+關(guān)注

關(guān)注

5文章

359瀏覽量

39857 -

信號(hào)

+關(guān)注

關(guān)注

11文章

2780瀏覽量

76643 -

電力電子

+關(guān)注

關(guān)注

29文章

559瀏覽量

48844 -

毛刺

+關(guān)注

關(guān)注

0文章

29瀏覽量

15653

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速PCB設(shè)計(jì)指南

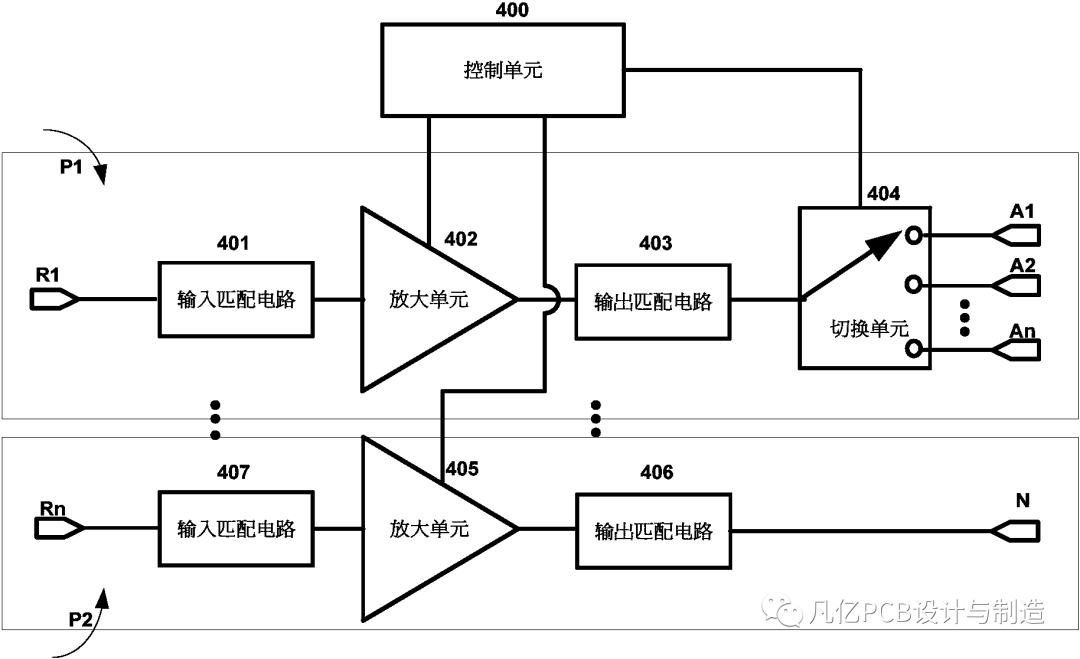

專(zhuān)業(yè)PCB設(shè)計(jì),高速PCB設(shè)計(jì),PCB設(shè)計(jì)外包, PCB Layout,PCB Design,PCB畫(huà)板公司,PCB設(shè)計(jì)公司,迅安通科技公司介紹

PCB設(shè)計(jì)與PCB制板的緊密關(guān)系

高速pcb與普通pcb的區(qū)別是什么

高速pcb布線規(guī)則有哪些

多層pcb設(shè)計(jì)如何過(guò)孔的原理

高速PCB設(shè)計(jì),信號(hào)完整性問(wèn)題你一定要清楚!

分析高速PCB設(shè)計(jì)信號(hào)完整性問(wèn)題形成原因及方法解決

分析高速數(shù)字PCB設(shè)計(jì)信號(hào)完整性解決方法

【2023電子工程師大會(huì)】高速PCB設(shè)計(jì)與驗(yàn)證分析ppt

EMC之PCB設(shè)計(jì)技巧

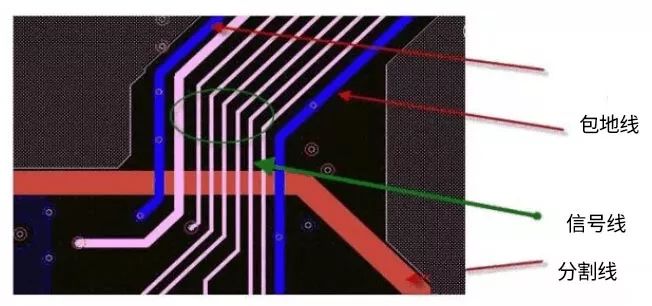

在高速電路設(shè)計(jì)中,如何應(yīng)對(duì)PCB設(shè)計(jì)中信號(hào)線的跨分割

高速PCB設(shè)計(jì)中的射頻分析與處理方法

高速PCB設(shè)計(jì):影響信號(hào)質(zhì)量的幾大問(wèn)題

高速PCB設(shè)計(jì):影響信號(hào)質(zhì)量的幾大問(wèn)題

評(píng)論