第 1 部分討論了逐次逼近寄存器 (SAR) 模數轉換器 (ADC),正如其中所述,模擬傳感器信號鏈面臨著高精度挑戰:多個增益、信號調節和復雜的模擬濾波級,全部都會饋送至 SAR-ADC;因此可能會導致模擬錯誤。設計人員也可能最終得到一個昂貴的元件密集型 PC 板解決方案。

此外,從超低傳感器信號開始,信號鏈中每個模擬級的輸出都會產生誤差,進而在轉換器的數字輸出端表現為低信噪比 (SNR) 和高失真誤差。此類系統的設計人員需要退后一步,重新思考高精度傳感器 ADC 范式。 若要解決高精度傳感器系統的相關問題,可選擇一種 ADC 拓撲,將小傳感器信號快速進行數字化,并以數字方式實現增益和濾波等噪聲模擬功能。這就是三角積分 (Δ?) ADC 的作用。 本文以來自 Analog Devices 的AD4110-1通用輸入模數前端為例,簡要介紹 Δ? ADC 的基本功能和內部模數轉換機制。在此基礎上,文中會深入探究周圍的信號鏈,并為合適的數據采集系統提供一些關鍵規格。

Δ? ADC 的結構

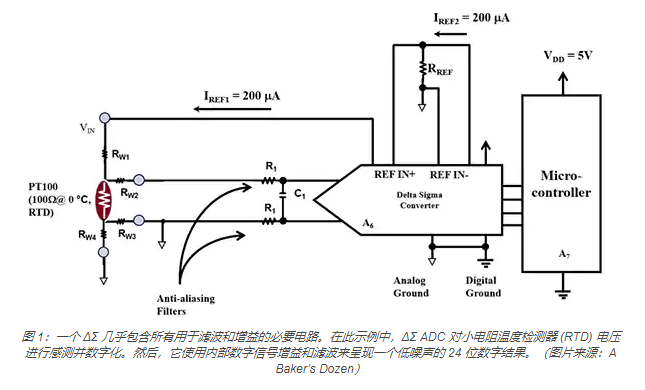

就在世紀之交之前,Δ? ADC 搶走了模擬技術的主導地位。隨著 Δ? 先進技術的廣泛普及,主要的模擬信號和計算過程開始扎根于數字領域。Δ? ADC 集成電路 (IC) 檢查發現,超過 80% 的硅片空間用于執行數字功能。以數字電路為主的附帶收獲是穩健性和小尺寸。 這是怎么可能實現的?最初是低壓模擬信號的直接數字化。進入數字領域后,數字電路幾乎可以完全取代模擬濾波,同時還可以執行任何需要的增益功能(圖 1)。數字電路也隨著每個半導體工藝節點而縮小。

在圖 1 中,24 位 Δ? ADC 系統由一個模擬輸入、一個中央數字引擎和一個數字 I/O 端子組成。轉換器獲取低壓 RTD 信號,并通過數字濾波產生模擬輸入的完整 24 位數字表示。這里沒有通常在 SAR-ADC 電路中占主導地位的模擬增益模塊,唯一的模擬濾波器是 R1和 C1的組合。是的,這是一個簡單、便宜的一階濾波器!

Δ? ADC 的工作原理

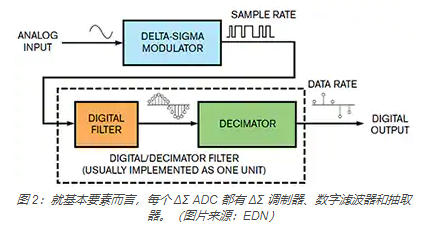

Δ? ADC 的基本拓撲具有一個與數字濾波器串聯的 Δ? 調制器。除了這種基本拓撲外,大多數 Δ? ADC 還具有各種其他功能。但是,所有 Δ? 轉換器都具有這種基本核心(圖 2)。

在圖 2 中,輸入可以是正弦波或 DC;此處將重點討論正弦波輸入。Δ? 調制器將單周期正弦波數字化為 1 位流。Δ? 調制器輸出采樣頻率為 Fs。盡管 1 位調制器轉換似乎會產生高量化噪聲,但實際上信號噪聲已“整形”為較高的頻率。這樣便為數字濾波器輸出端的低噪聲、高分辨率轉換鋪平了道路。

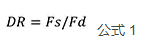

在調制器的輸出端,數字濾波器會累加 Δ? 調制器的 1 位結果并執行濾波器計算。數字濾波器輸出信號以數字方式反射模擬輸入信號,同時繼續采用輸出頻率 Fs。現在,該信號僅留在數字域中。數字低通濾波器或抽取濾波器會衰減高頻噪聲并減慢輸出數據速率 1/Fd。數字/抽取濾波器對調制器的 1 位代碼流進行采樣和濾波,使其成為較慢的多位代碼。 雖然多數轉換器只有一個采樣率,但 Δ? 轉換器卻有兩個:輸入采樣頻率 (Fs) 和輸出數據頻率 (Fd)。根據公式 1,這兩個頻率變量的比值定義系統抽取率 (DR):

Δ? 調制器

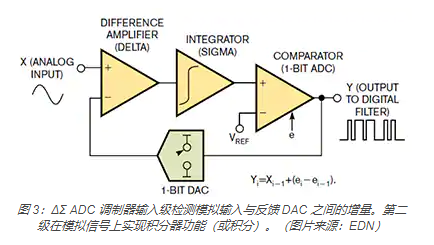

Δ? 調制器通過產生 1 位代碼流來執行實際的模數轉換。此過程從差分放大器開始(圖 3)。

在圖 3 中,差分放大器(三角)將模擬信號傳輸到積分器(積分)。在積分器的輸出端,比較器以極高的采樣率 (1/Fs) 區分積分器的輸出與電壓基準 (VREF)。此外,比較器會將 1 位流提供給 1 位數模轉換器 (DAC)。然后,調制器會測量模擬輸入信號與反饋 DAC 的模擬輸出之間的差值。

Δ? >調制器通過積分器和 DAC 反饋回路的作用將噪聲整形為更高的頻率。圖 3 中的公式(右下方)顯示了傳遞方程:Yi= Xi-1+ (ei– ei-1)。調制器通過量化噪聲 (ei) 將輸入信號 (Xi) 數字化為 1 位輸出代碼 (Yi)。具體來說,調制器的輸出 (Yi) 等于輸入 (Xi-1) 加上量化噪聲 (ei– ei-1)。該公式將量化噪聲顯示為當前誤差 (ei) 減去調制器先前誤差 (ei-1) 的差值。

數字和抽取濾波器

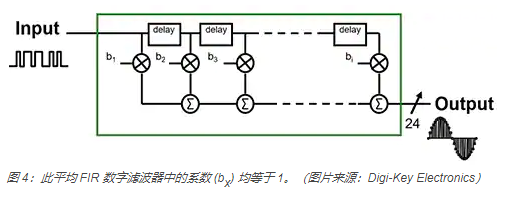

平均化是一種數字濾波形式,常用于低速工業 Δ? ADC 中。幾乎所有工業 Δ? ADC 都包含一類稱為 sinc濾波器的平均濾波器,它們使用線性相位有限沖激響應 (FIR),后者是一種數字低通濾波器(圖 4)。

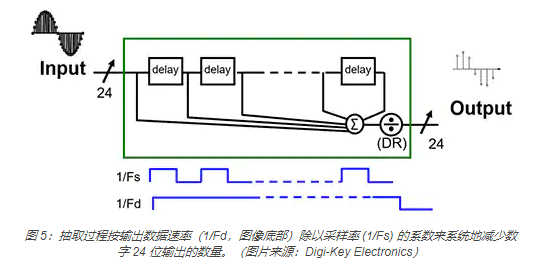

在圖 4 中,調制器輸出位流是此數字濾波器的輸入,而調制器的采樣時鐘確定延遲時間。圖 4 的 FIR 濾波器系數 (bx) 均等于 1。利用這種平均算法,FIR 數字濾波器可生成圖 3 中模擬輸入的低噪聲、24 位數字表示,并且以調制器的采樣率 (1/Fs) 進行采樣。然后,抽取濾波器使用 DR 降低輸出數據速率。 在文獻中,“抽取”一詞是指系統性清除不需要士兵的軍事行為。在數字電子器件中,抽取使用相同的概念來通過 DR 降低數字信號的輸出數據速率 (1/Fd)。為此,快速而數字化的方法是系統性丟棄一些數字濾波器的輸出樣本(圖 5)。

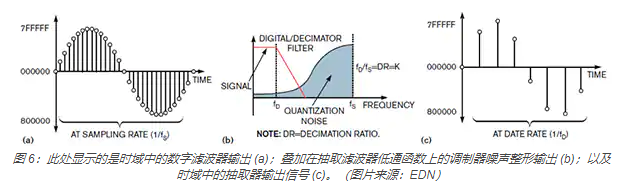

根據公式 1,圖 5 中的抽取過程按 DR 抽取輸出數據速率 (1/Fd)。 通過數字和抽取濾波器的事件可有效降低 Δ? ADC 噪聲(圖 6)。

圖 6 顯示了通過數字/抽取濾波器時的數字信號。數字濾波器 24 位輸出(圖 6(a))的運行速率與調制器采樣率 (1/Fs) 相同。調制器已經將量化噪聲整形為較高的頻率(圖 6(b)),因此數字/抽取濾波器會捕獲輸出信號的低頻部分。抽取濾波器(圖 6(c))輸出產生原始模擬信號的低頻數字表示。

數字擴展

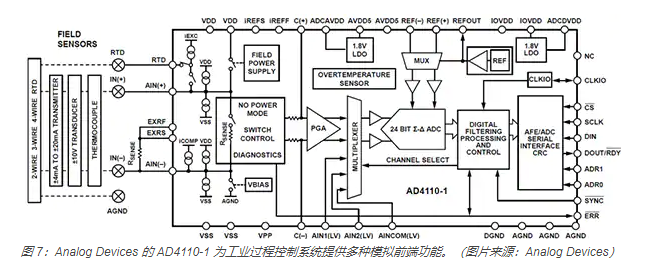

Δ? ADC 主要存在于數字域。現在,可以輕松添加數字可編程增益級、電流源、短路或開路輸入信號指示器,以及各種串行輸出接口(圖 7)。

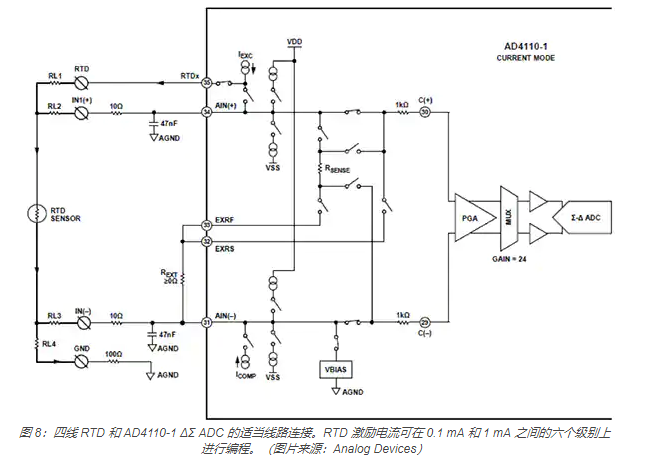

如圖 7 所示,Analog Devices的 AD4110-1 Δ? ADC 具有許多數字增強功能,包括可編程輸入端子、診斷功能和靈活的數據速率。輸入就緒型傳感器接口包括 RTD 和熱電偶溫度傳感器。 AD4110-1 具有 Δ? ADC 的基本核心,但該器件的數字加重功能支持一系列數字使能功能,從而讓 AD4110-1 現已成為通用模擬前端 (AFE)。 與標準 Δ? ADC 一樣,AD4110-1 能夠將來自熱電偶、RTD 和電橋的極低電壓進行數字化。雖然這些功能通常需要額外的激勵電路,但 AD4110-1 已將它們集成在電路板上。 例如,RTD 需要一個精密電流源,并且該電流源與轉換器的電壓基準成比例(圖 8)。

在圖 8 中,AD4110-1 包含一個激勵電流,該電流可以使用轉換器的 PGA_RTD_CTRL 寄存器,在 0.1 mA 和 1 mA 之間的六個級別上進行編程。RTD 電阻的激勵電流來自引腳 35。轉換器通過引腳 34 與 31 高阻抗輸入感測 RTD 兩端的電壓降。AD4110-1 可編程增益放大器 (PGA) 提供 0.2 至 24 V/V 的 16 個可編程增益。利用此功能,設計人員可以進一步將輸入傳感器補充到 AD4110-1 輸入范圍。其他輔助功能包括上拉/下拉電流以感測裸線的存在(對熱電偶有用),以及增益校準和校正系數。

總結

Δ? ADC 采用了前端調制器、FIR 數字濾波器和抽取濾波器,可消除復雜的模擬前端電路,并能提供經過數字平均的高分辨率、低噪聲數字輸出信號。由于大部分電路均采用數字形式,因此可以通過先進的數字工藝節點輕松擴展,在保持較小的占位空間和低電路板復雜度的同時,增加更多的功能。 Analog Devices 的 AD4110-1 Δ? ADC 充分利用了這種 ADC 架構的特性。AD4110-1 具有 Δ? ADC 的基本核心,但該器件的數字加重功能支持一系列數字使能功能,從而讓 AD4110-1 現已成為通用 AFE,并且能真正直接用于 RTD 和熱電偶。 來源:Digi-Key

責任編輯:xj

原文標題:模擬基礎知識:三角積分 (Δ?) ADC 及其數字功能的利用方式

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

-

SAR

+關注

關注

3文章

414瀏覽量

45898 -

adc

+關注

關注

98文章

6438瀏覽量

544097

原文標題:模擬基礎知識:三角積分 (Δ?) ADC 及其數字功能的利用方式

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺談電動機三角接法是什么意思?舉例分析

三相電機三角形連接有哪些參數關系?

什么是三相電機三角形接法?定義是什么?

AMC1204-Q1針對電流分流測量的20MHz,二階,隔離型三角積分調制器數據表

三角波發生器的組成和應用

三角形連接和星形連接的基本概念和特點

三相負載與三角聯結的關系

三角形連接線電流和相電流的關系

軟啟動與星三角啟動的區別在哪里

變壓器“三角形接線”和“星形接線”接法詳解

基于激光三角測距法的激光雷達原理

三角積分(Δ?) ADC及其數字功能的利用方式

三角積分(Δ?) ADC及其數字功能的利用方式

評論