上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號(hào)線通過一個(gè)電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個(gè)基本的作用都是相同的,只是在不同應(yīng)用場合中會(huì)對(duì)電阻的阻值要求有所不同,從而也引出了諸多新的概念,本節(jié)我們就來小談一下這些內(nèi)容。

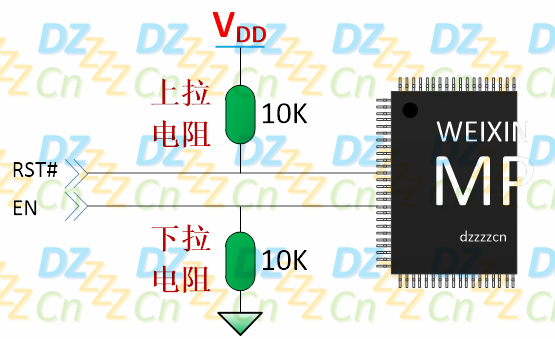

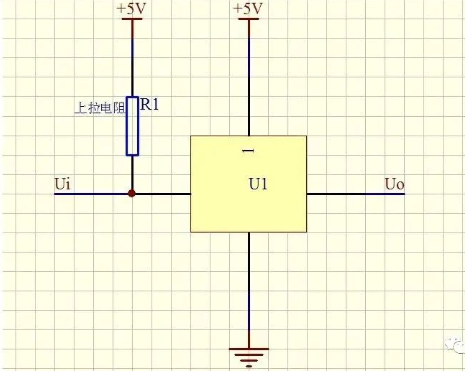

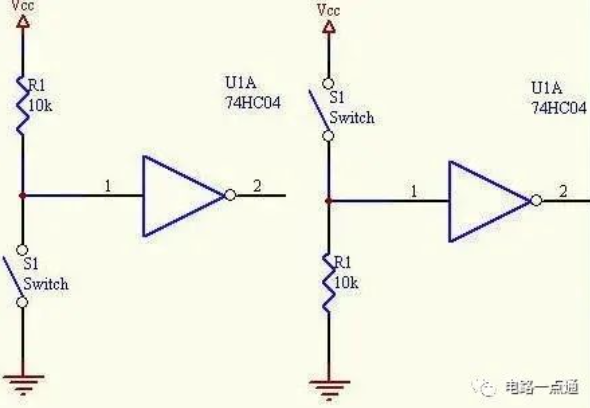

如果拉電阻用于輸入信號(hào)引腳,通常的作用是將信號(hào)線強(qiáng)制箝位至某個(gè)電平,以防止信號(hào)線因懸空而出現(xiàn)不確定的狀態(tài),繼而導(dǎo)致系統(tǒng)出現(xiàn)不期望的狀態(tài),如下圖所示:

在實(shí)際應(yīng)用中,10K歐姆的電阻是使用數(shù)量最多的拉電阻。需要使用上拉電阻還是下拉電阻,主要取決于電路系統(tǒng)本身的需要,比如,對(duì)于高有效的使能控制信號(hào)(EN), 我們希望電路系統(tǒng)在上電后應(yīng)處于無效狀態(tài),則會(huì)使用下拉電阻。

假設(shè)這個(gè)使能信號(hào)是用來控制電機(jī)的,如果懸空的話,此信號(hào)線可能在上電后(或在運(yùn)行中)受到其它噪聲干擾而誤觸發(fā)為高電平,從而導(dǎo)致電機(jī)出現(xiàn)不期望的轉(zhuǎn)動(dòng),這肯定不是我們想要的,此時(shí)可以增加一個(gè)下拉電阻。

而相應(yīng)的,對(duì)于低有效的復(fù)位控制信號(hào)(RST#),我們希望上電復(fù)位后處于無效狀態(tài),則應(yīng)使用上拉電阻。

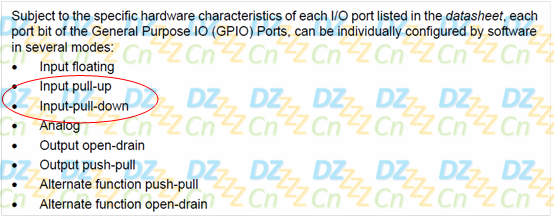

大多數(shù)具備邏輯控制功能的芯片(如單片機(jī)、FPGA等)都會(huì)集成上拉或下拉電阻,用戶可根據(jù)需要選擇是否打開,STM32單片機(jī)GPIO模式即包含上拉或下拉,如下圖所示(來自ST數(shù)據(jù)手冊(cè)):

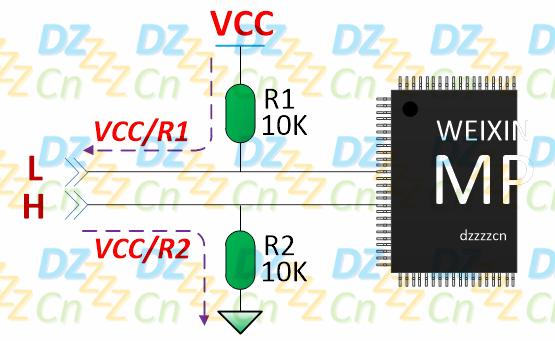

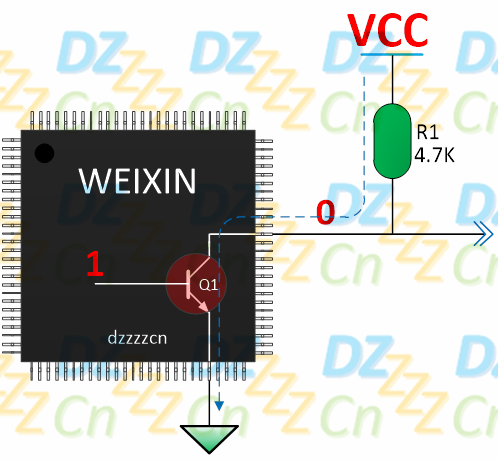

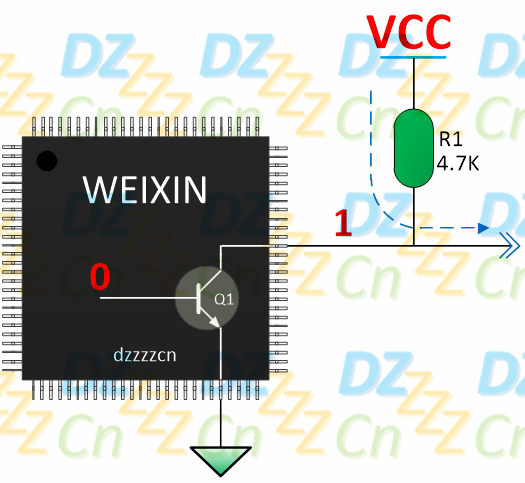

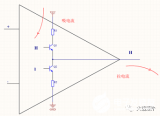

根據(jù)拉電阻的阻值大小,我們還可以分為強(qiáng)拉或弱拉(weak pull-up/down),芯片內(nèi)部集成的拉電阻通常都是弱拉(電阻比較大),拉電阻越小則表示電平能力越強(qiáng)(強(qiáng)拉),可以抵抗外部噪聲的能力也越強(qiáng)(也就是說,不期望出現(xiàn)的干擾噪聲如果要更改強(qiáng)拉的信號(hào)電平,則需要的能量也必須相應(yīng)加強(qiáng)),但是拉電阻越小則相應(yīng)的功耗也越大,因?yàn)檎P盘?hào)要改變信號(hào)線的狀態(tài)也需要更多的能量,在能量消耗這一方面,拉電阻是絕不會(huì)有所偏頗的,如下圖所示:

對(duì)于上拉電阻R1而言,控制信號(hào)每次拉低L都會(huì)產(chǎn)生VCC/R1的電流消耗(沒有上拉電阻則電流為0),相應(yīng)的,對(duì)于下拉電阻R2而言,控制信號(hào)每次拉高H也會(huì)產(chǎn)生VCC/R2R 電流消耗(本文假設(shè)高電平即為VCC)。

強(qiáng)拉與弱拉之間沒有嚴(yán)格說多少歐姆是強(qiáng)弱的分界,一般我們使用的拉電阻都是弱拉,這樣我們?nèi)匀豢梢允褂猛獠靠刂菩盘?hào)將已經(jīng)上/下拉的信號(hào)線根據(jù)需要進(jìn)行電平的更改。

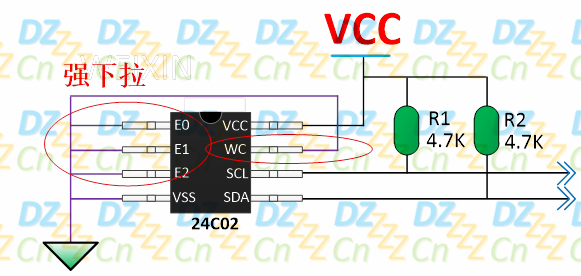

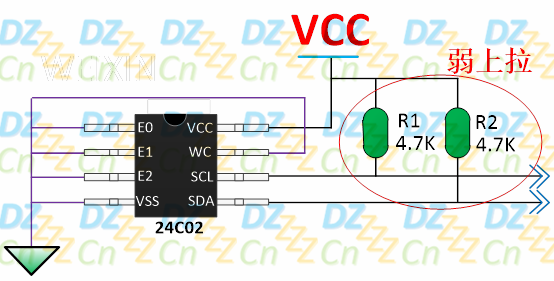

強(qiáng)拉電阻的極端就是零歐姆電阻,亦即將信號(hào)線直接與電源或地相連接,比如,對(duì)于EEPROM存儲(chǔ)芯片24C02應(yīng)用電路,如下圖所示:

其中,E0,E1,E2(地址配置位)在應(yīng)用中通常都是直接強(qiáng)上拉到電源VCC,或強(qiáng)下拉到GND,因?yàn)榇鎯?chǔ)芯片的地址在系統(tǒng)運(yùn)行過程中是不會(huì)再發(fā)生變化的,同樣,芯片的寫控制引腳WC(Write Control)也被強(qiáng)下拉到GND。

拉電阻作為輸出(或輸入輸出)時(shí)牽涉到的知識(shí)點(diǎn)會(huì)更多一些,但本質(zhì)的功能也是將電平箝位,最常見的輸出上拉電阻出現(xiàn)在開集(Open Collector,OC)或開漏(Open Drain,OD)結(jié)構(gòu)的引腳。

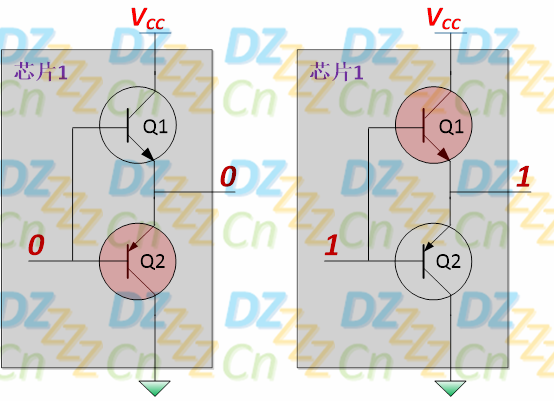

我們有很多芯片的輸出引腳是推挽輸出結(jié)構(gòu)(Output Push-Pull),如下圖所示(還有一種反相輸出的結(jié)構(gòu),本質(zhì)也是一樣的):

推挽輸出結(jié)構(gòu)引腳的特點(diǎn)是:無論引腳輸出高電平“H”還是低電平“L”,都有比較強(qiáng)的驅(qū)動(dòng)能力(輸入或輸出電流能力)!

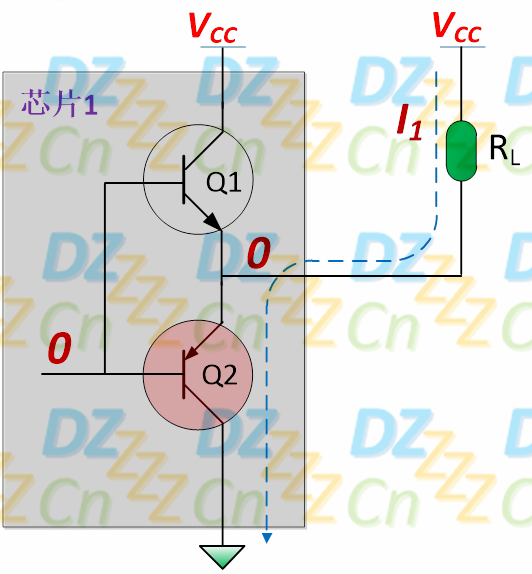

當(dāng)推挽輸出結(jié)構(gòu)的控制信號(hào)為低電平“L”時(shí),Q1截止Q2導(dǎo)通,電流I1由電源VCC經(jīng)負(fù)載RL與三極管Q2流向公共地,我們稱此電流為灌電流(Sink Current),也就是外部電流灌入芯片內(nèi)部,如下圖所示:

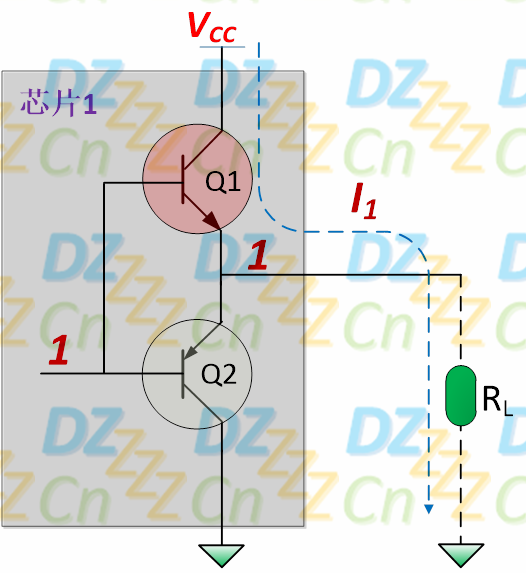

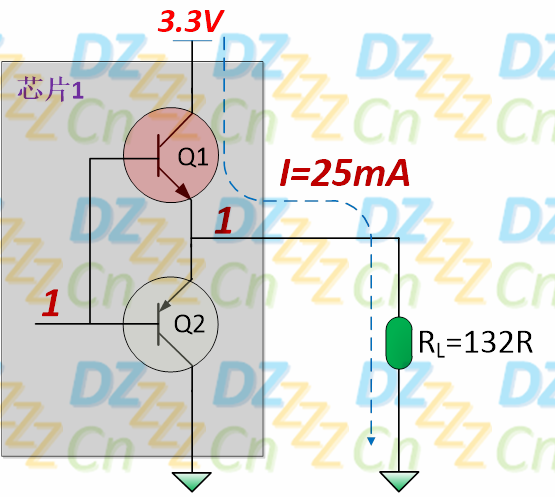

相應(yīng)的,當(dāng)推挽輸出結(jié)構(gòu)的控制信號(hào)為高電平“H”時(shí),Q1導(dǎo)通Q2截止,電流I1由電源VCC經(jīng)三極管Q1與負(fù)載RL流向公共地,我們稱此電流為拉電流(Source Current),也就是芯片內(nèi)部可以向外提供的電流(所以稱之為“源電源”),從另一個(gè)角度講,也就是外電路可以從芯片中拉走多少電流,如下圖所示:

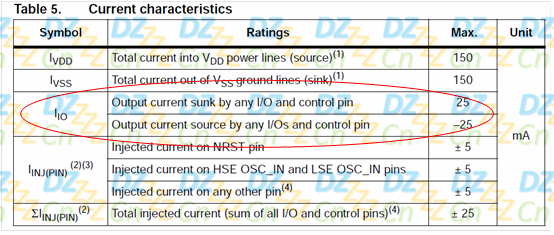

灌電流能力與拉電流能力也稱為芯片引腳的驅(qū)動(dòng)能力。對(duì)于任何給定的芯片,引腳的驅(qū)動(dòng)能力都是有限的,如下圖所示為STM32單片機(jī)的IO引腳電流驅(qū)動(dòng)能力(來自ST數(shù)據(jù)手冊(cè)):

由上表可知,STM32的IO引腳的驅(qū)動(dòng)能力為25mA,負(fù)號(hào)“-”表示電流的方向,灌與拉的電流方向是相反的(表中SUNK為SINK的過去分詞)

由于芯片引腳的驅(qū)動(dòng)能力都是有限的,如果引腳驅(qū)動(dòng)的負(fù)載比較重,將可能導(dǎo)致輸出電平不正確(無法輸出預(yù)定的電平),如下圖所示:

假定芯片的供電電壓為3.3V(忽略晶體管飽和壓降),則輸出最大電流25mA時(shí),負(fù)載RL的值約為132歐姆(3.3V/25mA),如果負(fù)載值小于132歐姆,則相應(yīng)輸出電流會(huì)更大(超過25mA),但是芯片引腳只能提供最大25mA的電流,因此,輸出電平將會(huì)下降(老板你只給我2500月薪,我就只能干2500的活,你要我干更多的活得開更多的工資,一個(gè)道理)

一般情況下,這種驅(qū)動(dòng)重負(fù)載(小電阻)的電路連接是不會(huì)燒毀內(nèi)部晶體管的,因?yàn)閮?nèi)部也是有限流電阻的,換句話講,就算輸出引腳對(duì)地短路,輸出電流也不會(huì)超過最大的驅(qū)動(dòng)能力(除非是不正規(guī)的芯片),當(dāng)然,在實(shí)際應(yīng)用過程中盡量不要超出引腳的驅(qū)動(dòng)能力。

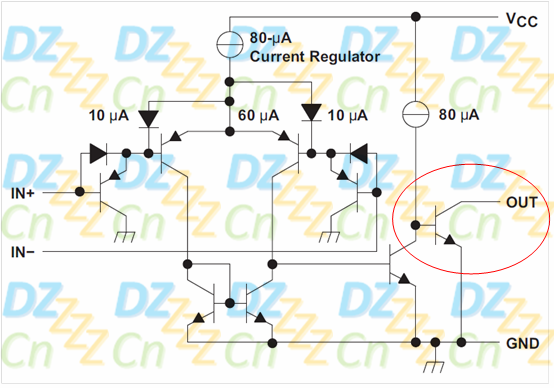

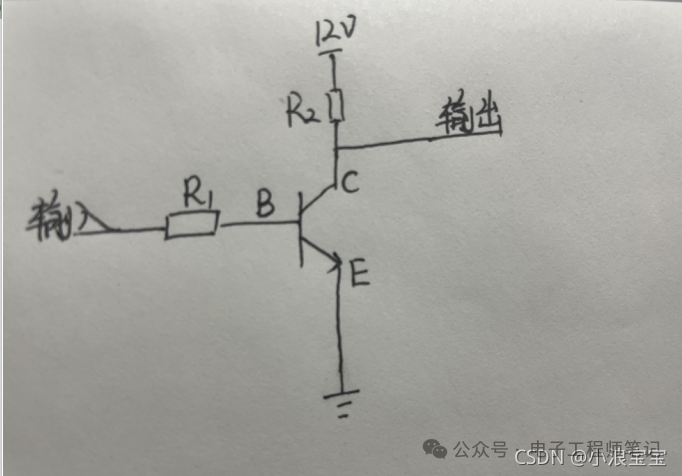

而OC(OD)的引腳輸出結(jié)構(gòu)有所不同(OC結(jié)構(gòu)存在于三極管,而OD結(jié)構(gòu)存在于場效管,下面以O(shè)C輸出結(jié)構(gòu)為例,OD輸出結(jié)構(gòu)的原理是一致的),如下圖所示:

當(dāng)三極管Q1的驅(qū)動(dòng)控制信號(hào)為高電平“H”時(shí),Q1飽和導(dǎo)通,將對(duì)應(yīng)輸出引腳拉為低電平“L”,如下圖所示:

但是當(dāng)控制驅(qū)動(dòng)信號(hào)為低電平“L”時(shí),三極管Q1截止,如果沒有外部上拉電阻的話,該引腳相當(dāng)于懸空(高阻態(tài)),無法輸出高電平,也就是說,OC/OD結(jié)構(gòu)輸出的引腳沒有拉電流(向外部電路提供電流)能力。因此,我們通常都會(huì)將OC/OD引腳通過外接電阻上拉到電源電壓VCC,這樣引腳輸出高電平時(shí)的拉電流就直接由電源VCC提供,如下圖所示:

大多數(shù)比較器芯片的輸出都是OD/OC輸出結(jié)構(gòu),如下圖所示(來自TI比較器LM393數(shù)據(jù)手冊(cè)):

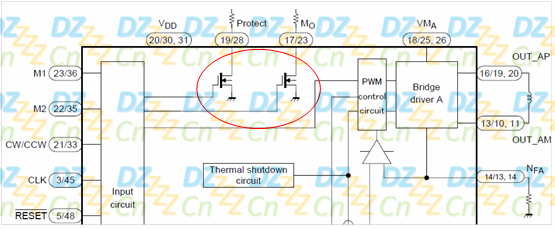

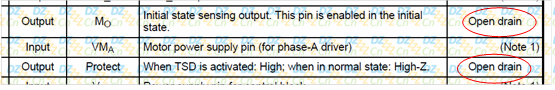

很多芯片或模塊向外反饋系統(tǒng)狀態(tài)的信號(hào)引腳也是這種結(jié)構(gòu),這樣用戶就可以根據(jù)電路系統(tǒng)實(shí)際需要將電平上拉到對(duì)應(yīng)的電源電壓VCC,就可以省略電平轉(zhuǎn)換了,如下圖所示(來自東芝步進(jìn)電機(jī)控制芯片TB6560數(shù)據(jù)手冊(cè)):

I2C(Inter Integrated Circuit,內(nèi)部集成電路)總線也是典型的OD輸出結(jié)構(gòu)的應(yīng)用,如下圖所示:

其中,SCL與SDA都是OD輸出結(jié)構(gòu)輸出,這樣的好處是可以作為雙向數(shù)據(jù)總線(也稱“線或Wire-OR”功能)。

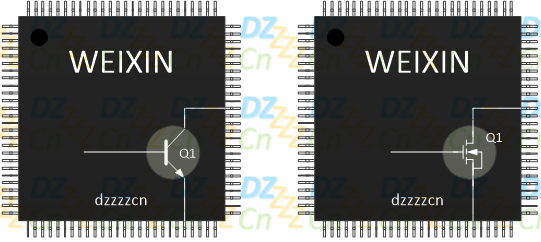

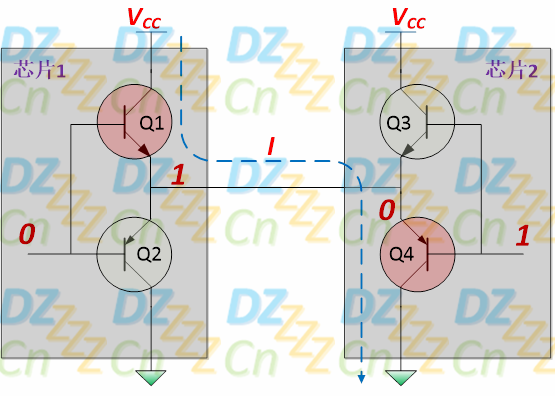

如果芯片引腳使用之前描述的推挽結(jié)構(gòu),則兩個(gè)或多個(gè)芯片的引腳連接時(shí)將如下圖所示:

假設(shè)如上圖所示芯片的輸出分別為0與1,則兩者直接相互連接后,會(huì)有非常大的電流自電源VCC經(jīng)Q1與Q4到公共地,雖然大多數(shù)情況下不至于燒芯片,但也會(huì)引起很大的功率消耗,同時(shí)也會(huì)導(dǎo)致數(shù)據(jù)沖突(芯片1總會(huì)試圖將數(shù)據(jù)線拉高,而芯片2則會(huì)試圖將數(shù)據(jù)線拉低,我們稱之為數(shù)據(jù)沖突或總線沖突,表示雙方都在搶占總線)

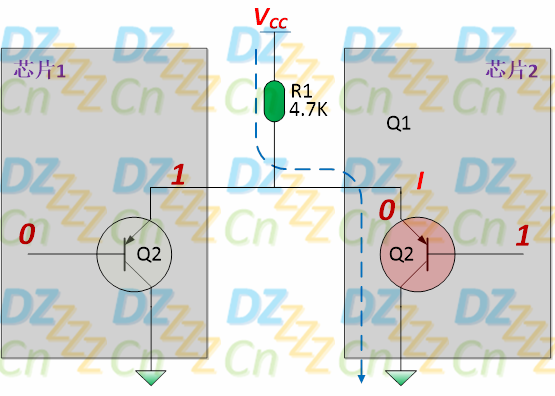

如果使用OC/OD輸出結(jié)構(gòu),則相應(yīng)的電路如下圖所示:

此時(shí),無論兩個(gè)芯片的引腳輸出什么狀態(tài),都不會(huì)引起數(shù)據(jù)沖突,配合各自芯片內(nèi)部的數(shù)據(jù)識(shí)別電路及仲裁系統(tǒng),雙方都可以主動(dòng)給另一方發(fā)送信息,也就是說,任何一方都可以將信號(hào)線拉高或拉低,而不會(huì)影響起數(shù)據(jù)沖突。

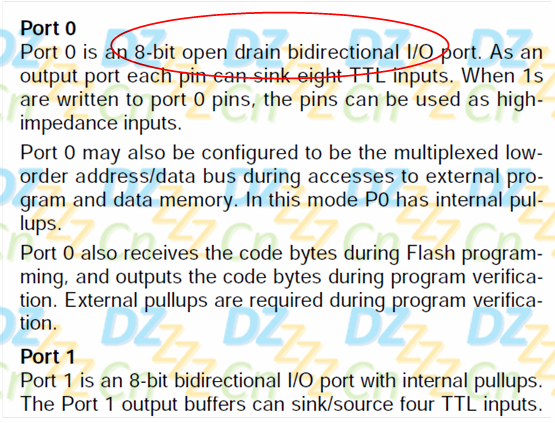

我們所熟悉的51單片機(jī)P0口也是OD結(jié)構(gòu),如下圖所示(來自ATMEL單片機(jī)AT89C51數(shù)據(jù)手冊(cè)):

這樣我們可以使用同一個(gè)P0口,再配合多個(gè)片選信號(hào)即可訪問多個(gè)外掛的存儲(chǔ)芯片。

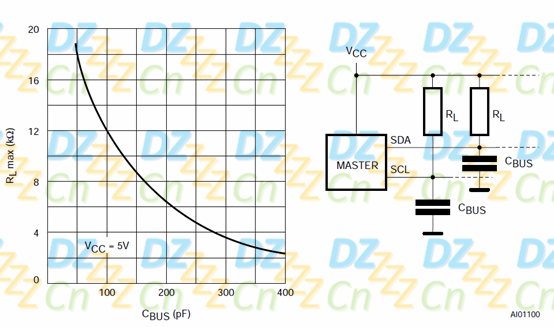

前面所述上拉電阻的阻值對(duì)輸入引腳引起的功耗同樣適用于輸出拉電阻,因此拉電阻不宜太小,但在輸出信號(hào)速度比較快的電路下,拉電阻也不宜太大,如下圖所示為I2C總線上拉電阻的參考最大值(來自ST存儲(chǔ)芯片 AT24C02數(shù)據(jù)手冊(cè))。

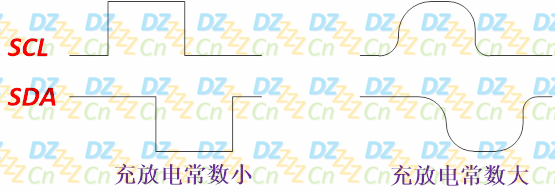

在總線上總會(huì)有些雜散電容CBUS,這些電容與上拉電阻RL形成了一個(gè)RC充放電電路,上拉電阻越大則充放電常數(shù)越大,這樣會(huì)把原先比較陡峭的數(shù)據(jù)邊沿變得平緩,如下圖所示:

嚴(yán)重的情況下將導(dǎo)致數(shù)據(jù)無法正常識(shí)別,這樣我們只能進(jìn)一步優(yōu)化電路參路,或降低通訊的速率。

原文標(biāo)題:上拉電阻與下拉電阻詳解

文章出處:【微信公眾號(hào):玩轉(zhuǎn)單片機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

453文章

50396瀏覽量

421789 -

電阻

+關(guān)注

關(guān)注

86文章

5467瀏覽量

171654 -

電流

+關(guān)注

關(guān)注

40文章

6750瀏覽量

131860

原文標(biāo)題:上拉電阻與下拉電阻詳解

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文讓你讀懂上拉電阻與下拉電阻

一文讓你讀懂上拉電阻與下拉電阻

評(píng)論