在ISE中,可以很方便地生成RTL模塊的實(shí)例化模板,Vivado其實(shí)也有這個(gè)功能,只是要通過Tcl命令實(shí)現(xiàn),而且這個(gè)命令隱藏的比較深。以Vivado 2020.2為例,在菜單下選擇Tools,點(diǎn)擊其中的XHub Stores,確保Design Utilities被安裝,如下圖所示,因?yàn)檫@個(gè)命令就位于其中。

該命令要在Elaborated Design階段執(zhí)行,因此,要先打開ElaboratedDesign。該命令提供了多個(gè)選項(xiàng),包括:

-verilog:生成Verilog模板

-vhdl:生成VHDL模板

-stub:生成實(shí)體部分

-cell:指定針對(duì)哪個(gè)單元生成實(shí)例化模板

我們看一下具體使用方法,以Vivado自帶的例子工程wavegen為例。打開Elaborated Design,執(zhí)行如下圖所示的4條腳本。

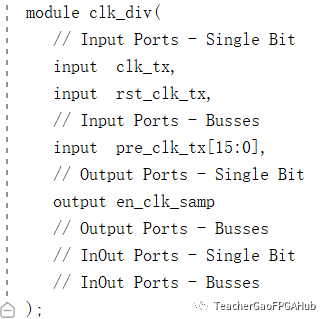

代碼第2行會(huì)生成如下圖所示內(nèi)容(-stub -verilog):

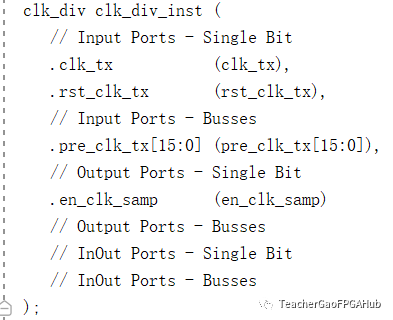

代碼第3行會(huì)生成如下圖所示內(nèi)容(-template -verilog):

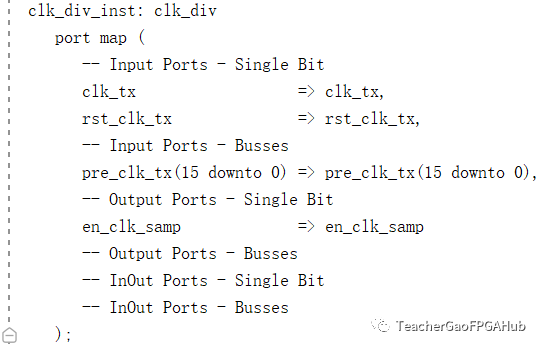

代碼第4行會(huì)生成如下圖所示內(nèi)容(-template -vhdl)

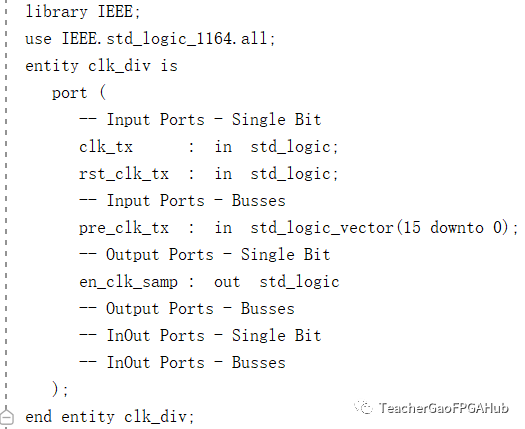

代碼第5行會(huì)生成如下圖所示內(nèi)容(-stub -vhdl)

原文標(biāo)題:如何生成實(shí)例化模板

文章出處:【微信公眾號(hào):Lauren的FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

模板

+關(guān)注

關(guān)注

0文章

108瀏覽量

20554 -

代碼

+關(guān)注

關(guān)注

30文章

4751瀏覽量

68357

原文標(biāo)題:如何生成實(shí)例化模板

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

A0到A4的圖框只要一個(gè)圖紙模板就搞定了?

不同領(lǐng)域中AI大模型的應(yīng)用實(shí)例

如何用C++創(chuàng)建簡(jiǎn)單的生成式AI模型

如何在tc377啟動(dòng)軟件時(shí)檢查SSH實(shí)例的內(nèi)存是否已初始化?

STM32cubeMX 6.10.0使用LL庫(kù)生成定時(shí)器模板報(bào)錯(cuò)的原因?

使用SDK5生成工程模板程序時(shí)老是出現(xiàn)錯(cuò)誤是為啥?

CW32F003E4芯片入門學(xué)習(xí):4.工程模板創(chuàng)建(使用例程或模板)

STM32L4R5生成工程模板時(shí),必須使用CubeMx,但是生成的程序編譯極慢為什么?

電源模塊測(cè)試數(shù)據(jù)一鍵導(dǎo)出,自定義報(bào)告模板

LabVIEW模板匹配位置信息導(dǎo)出

使用Jenkins和單個(gè)模板部署多個(gè)Kubernetes組件

如何使用CMW500測(cè)試頻譜模板

OpenCV邊緣模板匹配算法原理詳解

鴻蒙原生應(yīng)用/元服務(wù)開發(fā)-新版本端云一體化模板體驗(yàn)反饋

單個(gè)實(shí)例、多重實(shí)例和參數(shù)實(shí)例的區(qū)別

如何生成實(shí)例化模板?

如何生成實(shí)例化模板?

評(píng)論