和單片機一樣,FPGA開發板上也都會配有晶振用來生成板載時鐘。前一篇我們提到了小腳丫的固定板載時鐘頻率為12MHz,這個頻率實際上就是作為我們的時間參考基準。正如歌里唱的那樣:

嘀嗒嘀嗒嘀嗒嘀嗒

時針它不停在轉動

因此,小腳丫只要在通電之后,它的內部時鐘就會每隔83.8ns滴答一次。這個時間真的很快,連光速還沒來得及跑出小區大門就被掐斷了。那么問題來了:如果在某些應用場合中,我們不需要這么快的嘀嗒該怎么辦?比如,我們想讓小腳丫上的LED燈以可觀察的頻率閃爍,如1Hz,也就是1秒閃一下。

相信大家和我的想法一樣,就一個字:等。既然一秒鐘可以嘀嗒一千兩百萬次,那我們每次點亮LED之前就先等你跳一千兩百萬次好了,畢竟也不耗油。換句話說,就是把內部時鐘頻率放慢12,000,000倍。這個操作就叫做時鐘分頻,也就是我們今天要掌握的內容。

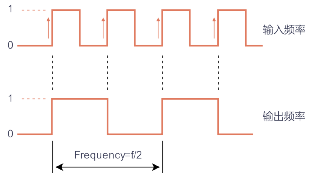

先說偶數分頻,也就是說將內部時鐘放慢的除數為偶數。在這里,我們只考慮占空比為50%的波形(高電平和低電平對半分)。圖1中,我們設定內部時鐘為我們的輸入頻率,也就是12MHz,那么如果想獲得一個6MHz的輸出頻率,只需要等第二次上沿信號即可,因此分頻除數為2。

圖1

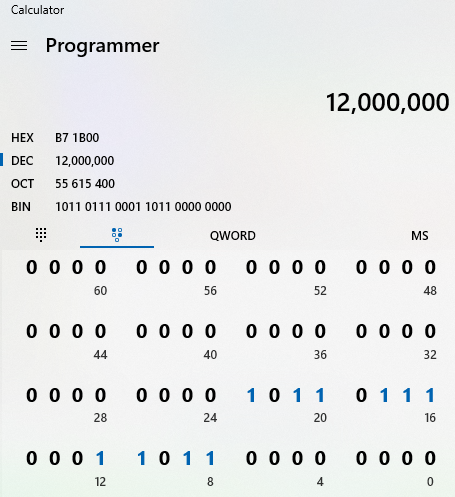

如果想得到更低的輸出頻率,比如1MHz,則除數調整12;如果1KHz,除數調成12000,依次類推。注意,這種方法只對除數為偶數的情況下才管用!以下是生成1Hz輸出的代碼,于是我們將除數調成了12,000,000。

moduleclkdivider(clock_in,clock_out);inputclock_in;outputregclock_out;reg[23:0]counter=24'd0;parameter DIVISOR = 24'd12000000;always@(posedgeclock_in)begincounter<=?counter?+?24'd1;if(counter>=(DIVISOR-1))counter<=?24'clock_out<=?(counter2 )?1'b1:1'b0;//條件賦值endendmodule

在代碼中我們注意到了這一行代碼:

reg[23:0] counter=24’0

這個實際上就是用于存儲小腳丫固定時鐘頻率的一個數據格式,至于為什么是24位寬直接參考圖2就可以。打開你們電腦里的計算器,調成碼農模式即可。

圖2

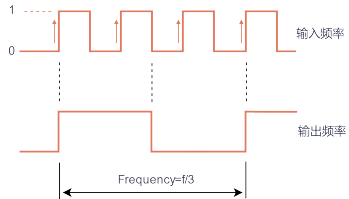

再說奇數分頻。比如說我們想獲得一個4MHz的頻率,按道理說我們把分頻除數調成3即可。而實際上奇數分頻的故事還是稍微多一點。我們看一下圖3就明白了。

圖3

不難發現,當除數為奇數時,此刻對應的時間為內部時鐘的下沿,如果僅靠上沿觸發的話,此時輸出是不會改變的。所以奇數分頻需要經歷上沿觸發和下沿觸發才能完成。還好,在Verilog里,我們先不用研究邊沿觸發的構造原理,只需要通過行為級描述即可直接完成指令:

always@(posedgeclk)//上沿觸發always @(negedge clk) //下沿觸發

現在我們來看一個分頻倍數為3的例子。圖3中,不論輸出信號是高電平還是低電平,都只涵蓋了兩個邊沿信號,也就是說,不論是上沿還是下沿時鐘,我們只需要分別等待2次觸發后進行賦值即可。

moduleclk_div3(clk,clk_out);inputclk;outputclk_out;:0]pos_count,neg_count;wire [1:0] r_nxt;always@(posedgeclk)//處理上沿時鐘觸發部分==2)//等待輸入時鐘上沿觸發2次=0;elsepos_count <= pos_count +1;always@(negedgeclk)//處理下沿時鐘觸發部分==2) //等待輸入時鐘下沿觸發2次=0;else=neg_count+1;=((pos_count==2)|(neg_count==2));//每等待2次觸發后進行賦值endmodule

了解了3倍分頻之后,如何實現通用的奇數分頻自然也就不在話下了,這一部分就交給愿意動手嘗試的朋友們去自行練習了。

最后,我們的任務是,讓小腳丫上的L1-L4這四個燈以2Hz的頻率閃爍,另外四個燈L5-L8分別以1Hz的頻率閃爍,看看能否實現呢?

責任編輯:xj

原文標題:基于FPGA的數字電路實驗6:時序邏輯電路之時鐘分頻

文章出處:【微信公眾號:FPGA入門到精通】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21677瀏覽量

601992 -

電路

+關注

關注

172文章

5852瀏覽量

171933 -

數字

+關注

關注

1文章

1693瀏覽量

51274

原文標題:基于FPGA的數字電路實驗6:時序邏輯電路之時鐘分頻

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序邏輯電路:時鐘分頻

時序邏輯電路:時鐘分頻

評論