STM32是ST(意法半導體)公司推出的基于ARM內核Cortex-M3的32位微控制器系列。Cortex-M3內核是為低功耗和價格敏感的應用而專門設計的,具有突出的能效比和處理速度。通過采用Thumb-2高密度指令集,Cortex-M3內核降低了系統存儲要求,同時快速的中斷處理能夠滿足控制領域的高實時性要求,使基于該內核設計的STM32系列微控制器能夠以更優越的性價比,面向更廣泛的應用領域。

STM32系列微控制器為用戶提供了豐富的選擇,可適用于工業控制、智能家電、建筑安防、醫療設備以及消費類電子產品等多方位嵌入式系統設計。STM32系列采用一種新型的存儲器擴展技術——FSMC,在外部存儲器擴展方面具有獨特的優勢,可根據系統的應用需要,方便地進行不同類型大容量靜態存儲器的擴展。

PART 2 FMSC 內部結構

2.1

FSMC技術優勢

①支持多種靜態存儲器類型。STM32通過FSMC可以與SRAM、ROM、PSRAM、NORFlash和NANDFlash存儲器的引腳直接相連。

②支持豐富的存儲操作方法。FSMC不僅支持多種數據寬度的異步讀/寫操作,而且支持對NOR/PSRAM/NAND存儲器的同步突發訪問方式。

③支持同時擴展多種存儲器。FSMC的映射地址空間中,不同的BANK是獨立的,可用于擴展不同類型的存儲器。當系統中擴展和使用多個外部存儲器時,FSMC會通過總線懸空延遲時間參數的設置,防止各存儲器對總線的訪問沖突。

④支持更為廣泛的存儲器型號。通過對FSMC的時間參數設置,擴大了系統中可用存儲器的速度范圍,為用戶提供了靈活的存儲芯片選擇空間。

⑤支持代碼從FSMC擴展的外部存儲器中直接運行,而不需要首先調入內部SRAM。

2.2

FSMC 內部結構

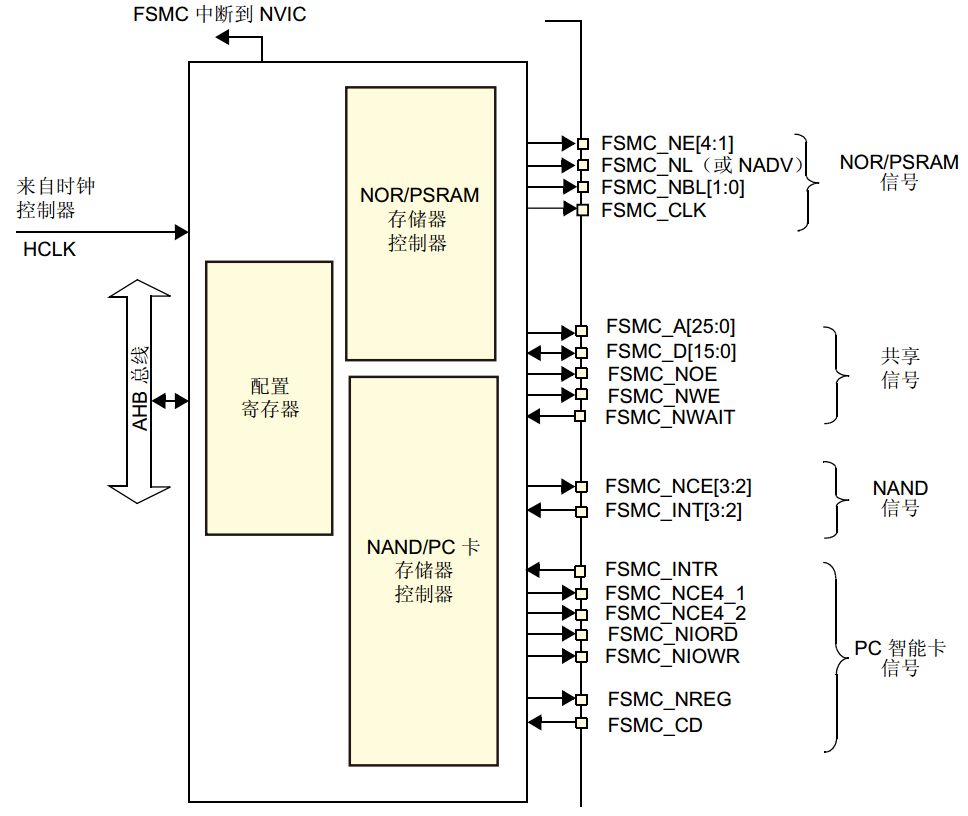

STM32微控制器之所以能夠支持NORFlash和NANDFlash這兩類訪問方式完全不同的存儲器擴展,是因為FSMC內部實際包括NORFlash和NAND/PCCard兩個控制器,分別支持兩種截然不同的存儲器訪問方式。在STM32內部,FSMC的一端通過內部高速總線AHB連接到內核Cortex-M3,另一端則是面向擴展存儲器的外部總線。

內核對外部存儲器的訪問信號發送到AHB總線后,經過FSMC轉換為符合外部存儲器通信規約的信號,送到外部存儲器的相應引腳,實現內核與外部存儲器之間的數據交互。FSMC起到橋梁作用,既能夠進行信號類型的轉換,又能夠進行信號寬度和時序的調整,屏蔽掉不同存儲類型的差異,使之對內核而言沒有區別。

2.3

FSMC映射地址空間

FSMC管理1GB的映射地址空間。該空間劃分為4個大小為256MB的BANK,每個BANK又劃分為4個64MB的子BANK,如表1所列。FSMC中的2個控制器管理的映射地址空間不同。NORFlash控制器管理第1個BANK,NAND/PCCard控制器管理第2~4個BANK。

由于兩個控制器管理的存儲器類型不同,擴展時應根據選用的存儲設備類型確定其映射位置。其中,BANK1的4個子BANK擁有獨立的片選線和控制寄存器,可分別擴展一個獨立的存儲設備,而BANK2~BANK4只有一組控制寄存器。

PART 3 FSMC擴展外部SRAM配置

3.1

FSMC擴展外部SRAM配置

在STM32與FPGA進行通信的時候,FPGA其實可以看做STM32外部的SRAM。因此相應的配置可以參考對外部SRAM的配置。

SRAM/ROM、NORFlash和PSRAM類型的外部存儲器都是由FSMC的NORFlash控制器管理的,擴展方法基本相同,其中NORFlash最為復雜。通過FSMC擴展外部存儲器時,除了傳統存儲器擴展所需要的硬件電路外,還需要進行FSMC初始化配置。

FSMC提供大量、細致的可編程參數,以便能夠靈活地進行各種不同類型、不同速度的存儲器擴展。外部存儲器能否正常工作的關鍵在于:用戶能否根據選用的存儲器型號,對配置寄存器進行合理的初始化配置。

3.2

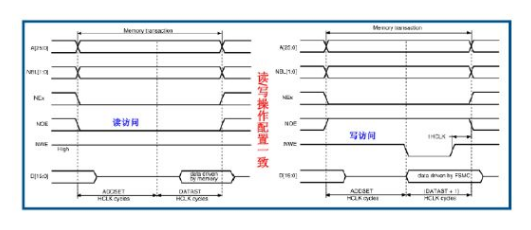

讀寫時序控制

異步通信模式1:SRAM/CRAM

3.3

配置存儲器基本特征

通過對FSMC特殊功能寄存器FSMC_BCRi(i為子BANK號,i=1,…,4)中對應控制位的設置,FSMC根據不同存儲器特征可靈活地進行工作方式和信號的調整。根據選用的存儲器芯片確定需要配置的存儲器特征,主要包括以下方面:

①存儲器類型(MTYPE)是SRAM/ROM、PSRAM,還是NORFlaSh;

②存儲芯片的地址和數據引腳是否復用(MUXEN),FSMC可以直接與AD0~AD15復用的存儲器相連,不需要增加外部器件;

③存儲芯片的數據線寬度(MWID),FSMC支持8位/16位兩種外部數據總線寬度;

④對于NORFlash(PSRAM),是否采用同步突發訪問方式(BURSTEN);

⑤對于NORFlash(PSRAM),NWAIT信號的特性說明(WAITEN、WAITCFG、WAITPOL);

⑥對于該存儲芯片的讀/寫操作,是否采用相同的時序參數來確定時序關系(EXTMOD)。

3.4

配置存儲器時序參數

FSMC通過使用可編程的存儲器時序參數寄存器,拓寬了可選用的外部存儲器的速度范圍。FSMC的SRAM控制器支持同步和異步突發兩種訪問方式。

選用同步突發訪問方式時,FSMC將HCLK(系統時鐘)分頻后,發送給外部存儲器作為同步時鐘信號FSMC_CLK。

此時需要的設置的時間參數有2個:

①HCLK與FSMC_CLK的分頻系數(CLKDIV),可以為2~16分頻;

②同步突發訪問中獲得第1個數據所需要的等待延遲(DATLAT)。

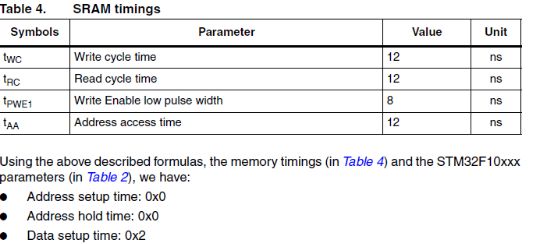

對于異步突發訪問方式,FSMC主要設置3個時間參數:地址建立時間(ADDSET)、數據建立時間(DATAST)和地址保持時間(ADDHLD)。FSMC綜合了SRAM/ROM、PSRAM和NORFlash產品的信號特點,定義了4種不同的異步時序模型。選用不同的時序模型時,需要設置不同的時序參數,如表2所列。

在實際擴展時,根據選用存儲器的特征確定時序模型,從而確定各時間參數與存儲器讀/寫周期參數指標之間的計算關系;利用該計算關系和存儲芯片數據手冊中給定的參數指標,可計算出FSMC所需要的各時間參數,從而對時間參數寄存器進行合理的配置。

PART 4 STM32擴展外部SRAM實例

4.1

難點解析

4.1.1 數據傳輸自動化

第一個角度理解STM32有FSMC(其實其他芯片基本都有類似的總線功能),FSMC的好處就是你一旦設置好之后,WR(寫)、RD(讀)、DB0-DB15這些控制線和數據線,都是FSMC自動控制的。打個比方,當你在程序中寫到:

*(volatileunsignedshortint*)(0x60000000)=val;

那么FSMC就會自動執行一個寫的操作,其對應的主控芯片的WE、RD這些腳,就會呈現出寫的時序出來(即WE=0,RD=1),數據val的值也會通過

DB0-15自動呈現出來(即FSMC-D0:FSMC-D15=val)。地址0x60000000會被呈現在數據線上(即A0-A25=0,地址線的對應最麻煩,要根據具體情況來。

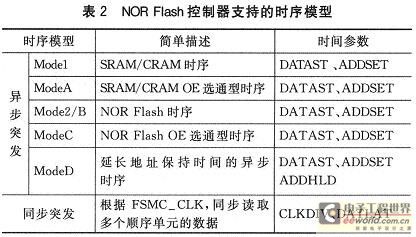

4.1.2 硬件連接

硬件平臺:(STM32F103VC+EP3C5E144C8N)

將圖中的IS61WV512BLL改為FPGA對應的接口即,可按照模式A-SRAM/PSRAM進行連接。

那么在硬件上面,我們需要做的,僅僅是MCU和LCD控制芯片的連接關系:

WE-WR,均為低電平有效

RD-RD,均為低電平有效

FSMC-D0-15接LCDDB0-15

FSMC_NE1--CS接PD7

連接好之后,讀寫時序都會被FSMC自動完成。但是還有一個很關鍵的問題,就是RS沒有接因為在FSMC里面,根本就沒有對應RS。怎么辦呢?這個時候,有一個好方法,就是用某一根地址線來接RS。

比如我們選擇了A16這根地址線來接,那么當我們要寫寄存器(備注:此處應為數據)的時候,我們需要RS,也就是A16(RS為高)置高。軟件中怎么做呢?也就是將FSMC要寫的地址改成0x60010000,如下:

*(volatileunsignedshortint*)(0x60010000)=val;

這個時候,A16在執行其他FSMC的同時會被拉高,因為A0-A18要呈現出0x60010000。0x60010000里面的Bit17=1,就會導致A16為1。要讀數據(備注:此處為寄存器)時,地址由0x60010000改為了0x60000000,這個時候A16就為0了。

RS問題:RS為0表示;讀寫寄存器;RS為1,讀寫數據RAM;

4.2

STM32固件對FSMC進行初始化配置

ST公司為用戶開發提供了完整、高效的工具和固件庫,其中使用C語言編寫的固件庫提供了覆蓋所有標準外設的函數,使用戶無需使用匯編操作外設特性,從而提高了程序的可讀性和易維護性。

STM32固件庫中提供的FSMC的SRAM控制器操作固件,主要包括1個數據結構和3個函數。

FSMC_NORSRAMInitStructure(調用庫函數)

RCC_Configuration();(時鐘選擇)

NVIC_Configuration();(中斷優先級)

FSMC_GPIO_Configuration();(連接IO口初始化)

FSMC_SRAM_Init();(FMSC配置)

4.3

其他人調試遇到問題點(摘錄)

項目中需要使用STM32和FPGA通信,使用的是地址線和數據線,在FPGA中根據STM32的讀寫模式A的時序完成寫入和讀取。之前的PCB設計中只使用了8跟數據線和8根地址線,調試過程中沒有發現什么問題,在現在的PCB中使用了8根地址線和16根數據線,數據寬度也改成了16位。

剛開始是讀取數據不正確,后來發現了問題,STM32在16位數據寬度下有個內外地址映射的問題,只需要把FPGA中的設定的地址乘以2在STM32中訪問就可以了,但是在寫操作的時候會出現寫當前地址的時候把后面的地址寫成0的情況,比如說我給FPGA中定義的偏移地址0x01寫一個16位數據,按照地址映射,在STM32中我把地址寫入0x02,。實際測試發現這個地址上的數據是對的,但是FPGA中0x02地址上的數據也變成了00。

塊1存儲區被劃分為4個NOR/PSRAM區,這四個區在內部地址上是連續排列的。但是實際上每個區共用的是同一組地址線與數據線,因此需要有內外的一個地址映射,因此在STM32中實際上有兩個地址,一個是在內部訪問的地址,另外一個是實際地址線輸出的地址。

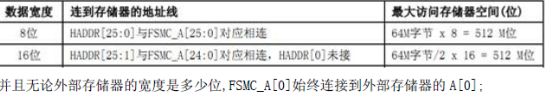

HADDR[27:0]對應的是需要轉換到外部存儲器的內部AHB地址線,其HADDR[27:26]位用于選擇四個存儲塊之一。HADDR[25:0]包含外部存儲器地址。HADDR是字節地址,而不同的外部存儲器數據長度也不一樣,因此在數據寬度為8位和16位時映射關系也不一樣。

在數據寬度為8位時HADDR[25:0]與FSMC_A[25:0]對應相連,這時候在STM32中訪問的地址和實際地址線產生的地址是一致的。而在16位數據寬度時HADDR[25:1]與FSMC_A[24:0]對應相連,HADDR[0]未接,這時候實際地址線上給出的地址為需要訪問的偏移地址的一半。

經過測試,發現寫數據時實際上是進行了多次寫入,導致把后面的地址也給寫上了,最終導致數據混亂,后來經過學長提醒,決定把訪問的地址定義為16位的,原來是32位的,經過測試問題解決。

所以這兒也算是長了經驗,因為我只用了8根地址線,為了避免可能的問題,地址最好定義成對應的位數。但是還是很納悶為什么之前八位數據線讀寫的時候沒有這個問題。

PART 5 結語

STM32作為新一代ARMCortex-M3核處理器,其卓越的性能和功耗控制能夠適用于廣泛的應用領域;而其特殊的可變靜態存儲技術FSMC具有高度的靈活性,對于存儲容量要求較高的嵌入式系統設計,能夠在不增加外部分立器件的情況下,擴展多種不同類型和容量的存儲芯片,降低了系統設計的復雜性,提高了系統的可靠性。

原文標題:FSMC | STM32與FPGA通信

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601856 -

通信

+關注

關注

18文章

5971瀏覽量

135857 -

存儲

+關注

關注

13文章

4263瀏覽量

85674 -

STM32

+關注

關注

2266文章

10871瀏覽量

354812 -

FSMC

+關注

關注

0文章

55瀏覽量

38110

原文標題:FSMC | STM32與FPGA通信

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析STM32 FSMC操作LCD的過程

求助100腳STM32的FSMC用法 與FPGA的FIFO通信

STM32的FSMC接口讀取FPGA的FIFO

基于FPGA和STM32的FSMC通信

FPGA MCU FSMC通信接口——NAND Flash模式

FPGA與STM32通過FSMC總線通信的實驗

STM32與FPGA通信中FSMC操作實例

STM32與FPGA通信中FSMC操作實例

評論