各種類型的Memory在FPGA設計中被廣泛使用,例如單端口RAM、簡單雙端口RAM、真雙端口RAM、單端口ROM以及雙端口ROM。這些RAM或ROM都可通過coe文件的形式定義其初始值。那么可能在實際應用中會出現這樣一種情形:設計的其他部分未做任何改動,只是更新RAM初始值。那么該如何操作更為方便呢?

如果采用傳統(tǒng)方式,先定義好coe文件,然后重新生成IP,這樣就必須重新執(zhí)行整個設計流程包括綜合、布局布線,編譯時間可想而知。但換個角度,細細分析一下,只是初始值改動,那么能否通過ECO(Engineering Change Order)的方式實現呢,就像更改觸發(fā)器初始值或者查找表的真值表內容一樣?答案是肯定的。這樣做好處也是顯而易見的:無需重新布局布線,只需更改RAM相關屬性,然后再次生成.dcp(這個不是必須的),最后生成.bit或.bin文件,這樣最大程度地繼承了原有設計,也最大程度地縮短了編譯時間。采用此方法的前提是RAM的規(guī)格要保持不變,這里的規(guī)格包括數據位寬和RAM深度。

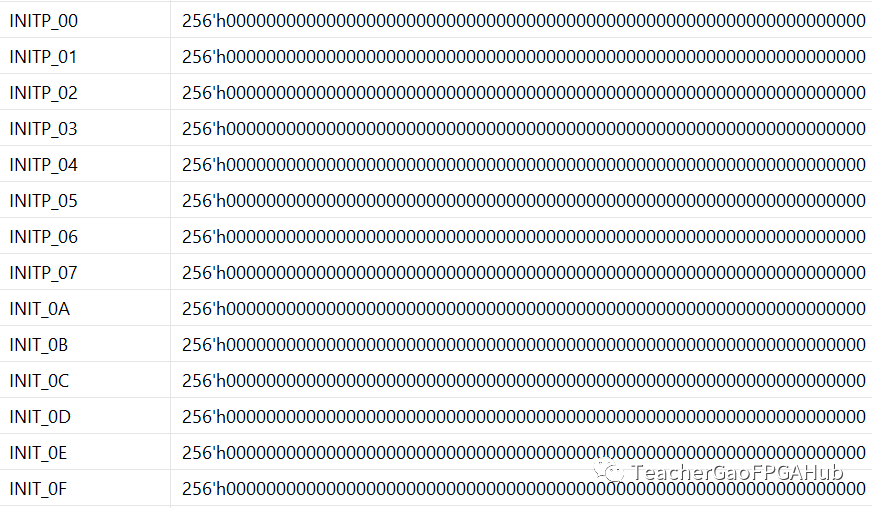

這里我們以Block RAM為例,先看看有哪些屬性與初始值密切相關,如下圖所示。基本上凡是以INIT打頭的屬性都與初始值相關。更新初始值本質上就是重新設定這些初始值。這些初始值是在IP生成階段根據coe內容被設定的。

第一步,根據更新后的coe文件生成一個同規(guī)格的IP,并對該IP執(zhí)行OOC綜合。

第二步,打開第一步生成的.dcp文件,找到相應的Block RAM,獲取上文提到的這些屬性對應的屬性值。

原文標題:ECO方式更新RAM/ROM初始值

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1626文章

21668瀏覽量

601864 -

ROM

+關注

關注

4文章

562瀏覽量

85676 -

RAM

+關注

關注

8文章

1367瀏覽量

114532

原文標題:ECO方式更新RAM/ROM初始值

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

手機中的ROM與內存的區(qū)別

ROM和RAM的主要區(qū)別

什么是RAM和ROM

ram存儲器和rom存儲器的區(qū)別是什么

外部存儲器是ROM還是RAM

rom和ram都是內存儲器嗎

易靈思SOC onchip RAM初始化

如何操作ECO方式更新RAM/ROM初始值更方便?

如何操作ECO方式更新RAM/ROM初始值更方便?

評論