濾波,屏蔽,接地;眾所周知是我們EMC設計的三大手法;其中接地設計是電子產品設計的一個重要問題!接地的目的如下:

A.接地可使我們的電路系統中的所有單元電路都有一個公共的參考0電位,也就是各個電路之間沒有電位差,保證電路系統能穩定的工作;

B.防止外部的電磁干擾。比如機殼接地;為瞬態干擾(ESD)提供了泄放通道;也可使因靜電感應而累積在機殼上的大量電荷通過大地泄放;如果電路有使用屏蔽罩或電路的屏蔽體,選擇合適的接地,就能獲得更好的屏蔽效果!

C.保證安全工作。當發生雷電(Surge)的電磁感應時,可避免電子設備損壞;

因此,接地對于EMS來說是抑制噪聲,防止干擾的主要方法。接地可以理解為一個等電位點或者等電位面是電子線路系統的基準電位,但不一定為大地電位;為了防止雷擊的損壞和保護產品&設備操作人員的安全,電子設備的機殼和供電系統的金屬構件再必須與大地相連接!而且要求接地電阻很小,不能超過規定值。

大多數產品都有要求接地;雖然接地可以是真正的接地,隔離或者浮地但接地的結構必須存在。接地我們有時會與為信號提供電流的回路相混淆。實際中大部分的問題是與PCB設計有關的;對于復雜系統的問題有時可以歸結為在模擬及數字電路之間提供參考連接及在PCB的地層和金屬外殼之間提供高頻連接的設計問題!

接地設計盡管是EMC設計中最重要的方面通常處理的問題并不容易直觀理解;其實每一個電路最終都要有一個參考接地源,電路設計首先考慮到的是接地設計,接地是使不希望的噪聲&干擾最小化 并對電路進行隔離劃分的一個重要方法。PCB的接地及鋪地銅設計降避免許多的噪聲問題,設計良好的接地系統就是以低的成本來防止不希望有的干擾及發射。比如對于高速數字電路中的地平面不完整,連接電纜后由于被地平面上的噪聲電壓驅動,就會產生EMI的問題!

首先分享對接地電流的看法:

A.一旦有電流流過一定的阻抗,就會產生一定的電壓降;利用歐姆定律在電子線路板上,就沒有OV電位電壓或電流的單位可能在微伏或微安級的范圍內,存在一個較小的有限值。

B.電流總是要返回其源頭來;回路可能有許多不同的路徑,每條路徑上的電流幅值不同,這會與該路徑的阻抗有關。不希望某些電流在其中某條路徑上流動,因此就需要在該路徑上要采取抑制措施!

因此在進行產品設計時;首先考慮到接地是最經濟的辦法。在設計階段若沒有考慮,就意味著該系統在EMC方面有可能會失敗。一個設計良好的接地系統;包含從電子線路的PCB設計,能從系統的角度防止EMI和EMS的問題才是關鍵的設計。

用下面的PCB鋪地及時鐘的接地設計案例進行分享關鍵設計:

電子產品中PCB布線鋪地的設計,對于目前低成本的物聯網及智能產品來說是眾多的設計工程師采用的方法;由于產品系統中需要有晶振推動的MCU/CPU高頻工作;PCB的鋪地設計能給系統EMC設計帶來優勢!

雙面板PCB系統鋪地的理論和分析;鋪銅地對EMI有什么影響?

鋪地好的方面:

注意信號線的PCB板邊緣的走線 如果鋪地;這個信號線對外的信號耦合就減小了;PCB鋪銅地在PCB板的邊緣的地方就要有;鋪銅鋪在信號線之間,它就能降低信號間的串擾,串擾中的EMI輻射是跟它間接的關系的!如果兩個都能達到或者做到了 EMI效果就會好!鋪地不是每個地方按面積來數的,地要有目標的去鋪設才會有好的作用的!

我的觀點:PCB有鋪銅的條件,且這個鋪銅是有作用的,如果能提升EMI的性能;可建議采用PCB鋪地銅的法則!

注意點:

在這個設計上要鋪地就要保證信號的鋪地平面與系統的參考地電位的阻抗要足夠小;否則這個鋪地就會對輻射干擾或抗輻射干擾都會有影響!

對于高頻的應用電子產品線路;系統由于共模電流的干擾EMI的問題,我們在DC-DC直流電流輸出端以及功能電路的接口連接器端需要增加共模電感及其組合的LCM*C的EMI濾波器的設計;此時的PCB鋪地銅布局布線會對我們的高頻EMI就會帶來影響;分析參如下:

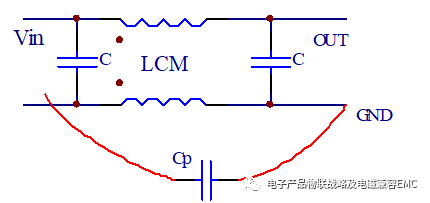

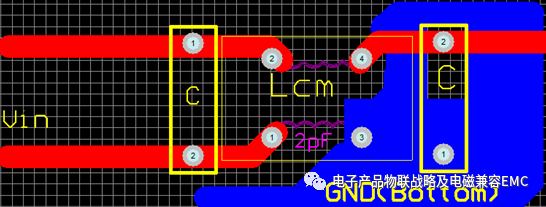

當電子線路中有共模電感的濾波設計時,前后級進行PCB鋪地銅設計時TOP層的走線與BOTTOM底層的PCB鋪地就會存在耦合電容Cp;高頻的騷擾信號就會通過耦合電容影響共模電感的噪聲阻抗性能;等效電路如下:

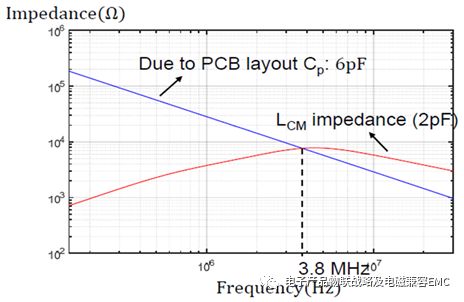

比如系統的設計LCM器件的雜散電容為2pF;其諧振頻率點在4MHZ左右;進行PCB的鋪地銅的設計由于PCB的布線,其輸入的走線與PCB的鋪地銅帶來有6pF的耦合電容參數;分析如下:

在其LCM的諧振點后就會降低其阻抗值-如上圖的頻率&阻抗特性曲線參考數據;在進行EMI測試時就會帶來高頻>4MHZ的高頻EMI的問題!

在進行PCB雙面板布線鋪銅地的設計時;在某些電路設計中改進PCB布局及走線就可以降低高頻的EMI電磁干擾;簡單優化的PCB設計參考如下:

注意:如果接地層存在噪聲耦合源,則接地層不應靠近敏感輸入電路。

對于雙面板的系統有時鐘信號是很普遍的;系統晶振時鐘頻率高,干擾諧波能量就強;干擾諧波除了從其輸入與輸出兩條布局布線傳導出來還會從空間輻射出來,若布局布線不合理,很容易產生很強的尖峰噪聲輻射問題,因此在PCB 板布局布線時對晶振和CLK 信號線布局非常重要,高頻時鐘信號需要能鏡像回流完整的鋪地銅的設計是很關鍵的。

時鐘源的布局布線簡單說明如下:

A.對于有源晶振:耦合電容應盡量靠近晶振的電源引腳,位置擺放順序:

按電源流入方向,依容值從大到小依次擺放,容值最小的電容最靠近引腳。

B.晶振的外殼必須接地,可將晶振信號源包地設計;防止向外輻射,也可以屏蔽外來信號對晶振的干擾。

C.晶振下面不要布其它走線,保證完全鋪地,同時在晶振的300mil范圍內不要布其它走線,防止晶振噪聲源耦合到其它布線、器件等影響性能。

D.時鐘信號的走線應盡量短,晶振不要放置在PCB板的邊緣!

如果電路板邊緣有復位及數據&地址信號線等等,PCB的板的邊緣都需要進行鋪地銅的設計;保證關鍵信號線的地回流路徑的鏡像對稱性設計。

因此,對于PCB雙面板的鋪銅地不是每個地方按面積來鋪設的,鋪地要有目標的去鋪設才能有好的作用,不正確的鋪地設計反而會惡化系統的EMC性能。

審核編輯:何安

-

接地

+關注

關注

7文章

757瀏覽量

45627 -

EMC設計

+關注

關注

5文章

257瀏覽量

39393

發布評論請先 登錄

相關推薦

電子產品結構與導熱材料解決方案

電子產品方案開發公司常用的15個單片機經典電路分享!

如何運用TRIZ解決電子產品的過熱問題?

安規電容的出現對電子產品的重要性

安規電容的出現對電子產品的重要性

測電子產品輻射的儀器叫什么

壓敏電阻能解決電子產品漏電問題嗎?

壓敏電阻能解決電子產品漏電問題嗎?

蔡司工業CT檢測設備在數碼電子產品中的作用

接地設計是電子產品設計的一個重要問題

接地設計是電子產品設計的一個重要問題

評論