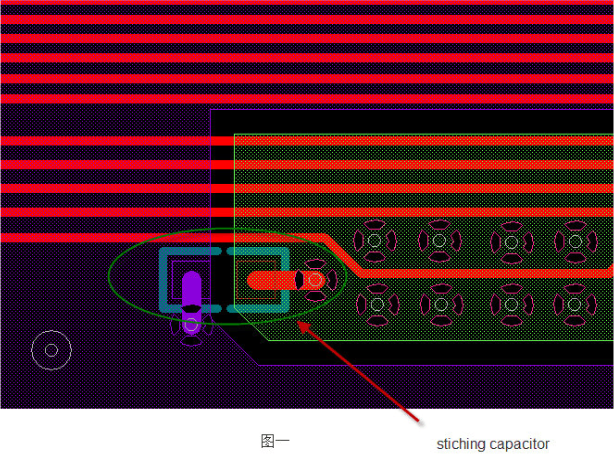

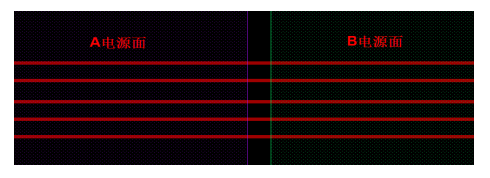

在PCB設(shè)計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現(xiàn)從一個電源面跨接到另一個電源面,這種現(xiàn)象我們就叫做信號跨分割。

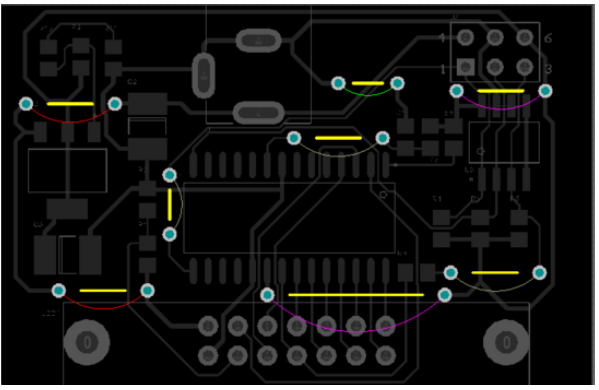

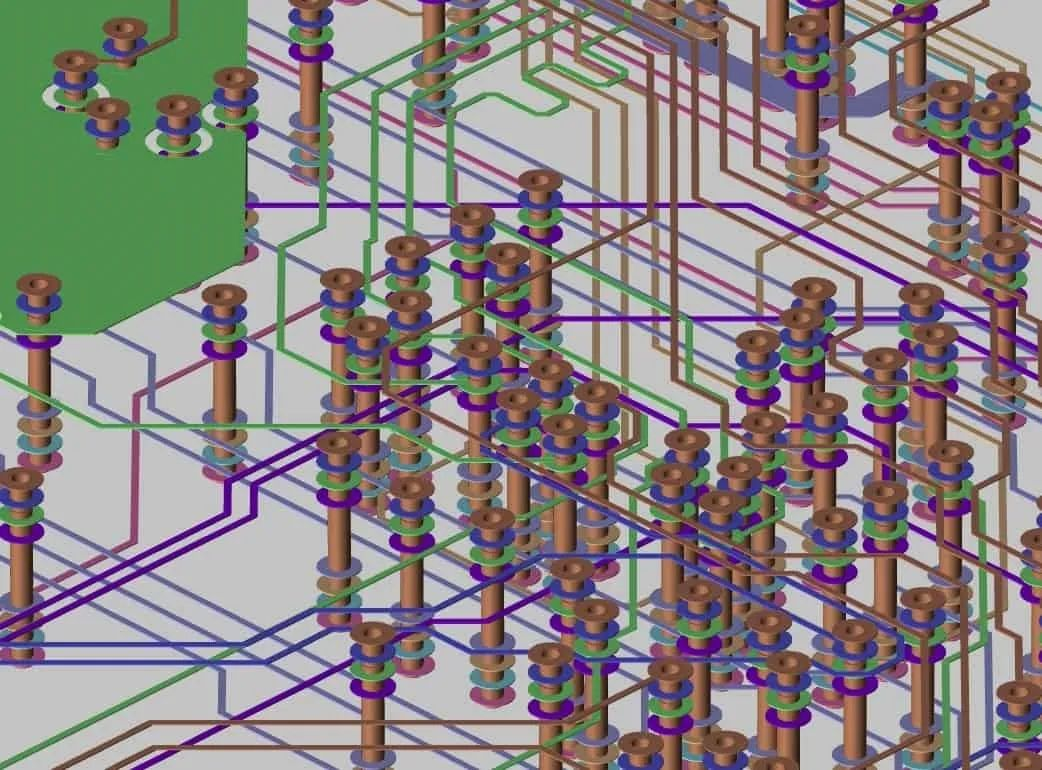

跨分割現(xiàn)象示意圖

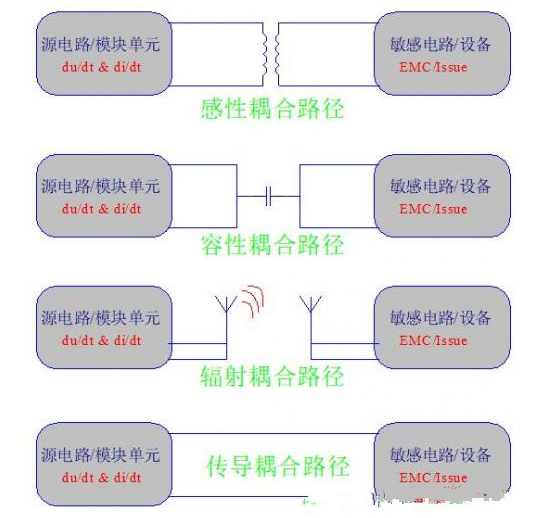

跨分割,對于低速信號可能沒有什么關(guān)系,但是在高速數(shù)字信號系統(tǒng)中,高速信號是以參考平面作為返回路徑,就是回流路徑。當參考平面不完整的時候,會出現(xiàn)如下不良影響:

a.會導致走線的的阻抗不連續(xù);

b.容易使信號之間發(fā)生串擾;

c.會引發(fā)信號之間的反射;

d.增大電流的環(huán)路面積、加大環(huán)路電感,使輸出的波形容易振蕩;

e.增加向空間的輻射干擾,同時容易受到空間磁場的影響;

f.加大與板上的其它電路產(chǎn)生磁場耦合的可能性;

g.環(huán)路電感上的高頻壓降構(gòu)成共模輻射源,并通過外接電纜產(chǎn)生共模輻射。

因此,PCB布線要盡可能靠近一個平面,并避免跨分割。若必須跨分割或者無法靠近電源地平面,這些情況僅允許在低速信號線中存在。

PCB設(shè)計中跨分割的處理

如果在PCB設(shè)計中不可避免的出現(xiàn)了跨分割,又該如何處理呢?這種情況下,需要對分割進行縫補,為信號提供較短的回流通路,常見的處理方式有添加縫補電容和跨線橋接。

1.縫補電容(Stiching Capacitor)

通常在信號跨分割處擺放一個0402或者0603封裝的瓷片電容,電容的容值在0.01uF或者是0.1 uF,如果空間允許,可以多添加幾個這樣的電容;同時盡量保證信號線在縫補電容 200mil 范圍內(nèi),距離越小越好;而電容兩端的網(wǎng)絡(luò)分別對應(yīng)信號穿過的參考平面的網(wǎng)絡(luò),見下圖中電容兩端連接的網(wǎng)絡(luò),兩種顏色高亮的兩種不同網(wǎng)絡(luò):

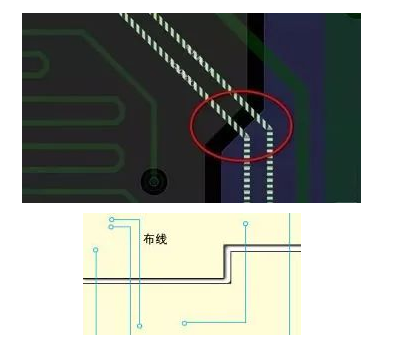

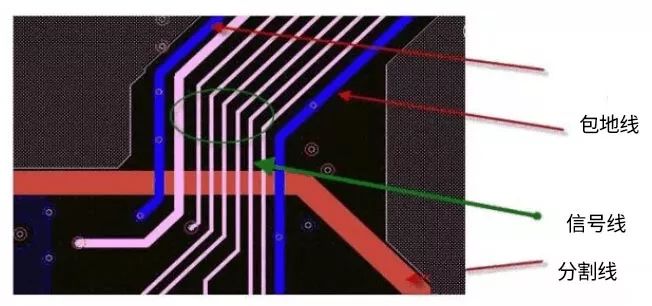

2.跨線橋接

常見的就是在信號層對跨分割的信號“包地處理”,也可能包的是其他網(wǎng)絡(luò)的信號線,這個個“包地”線盡量粗,這種處理方式,參考下圖。

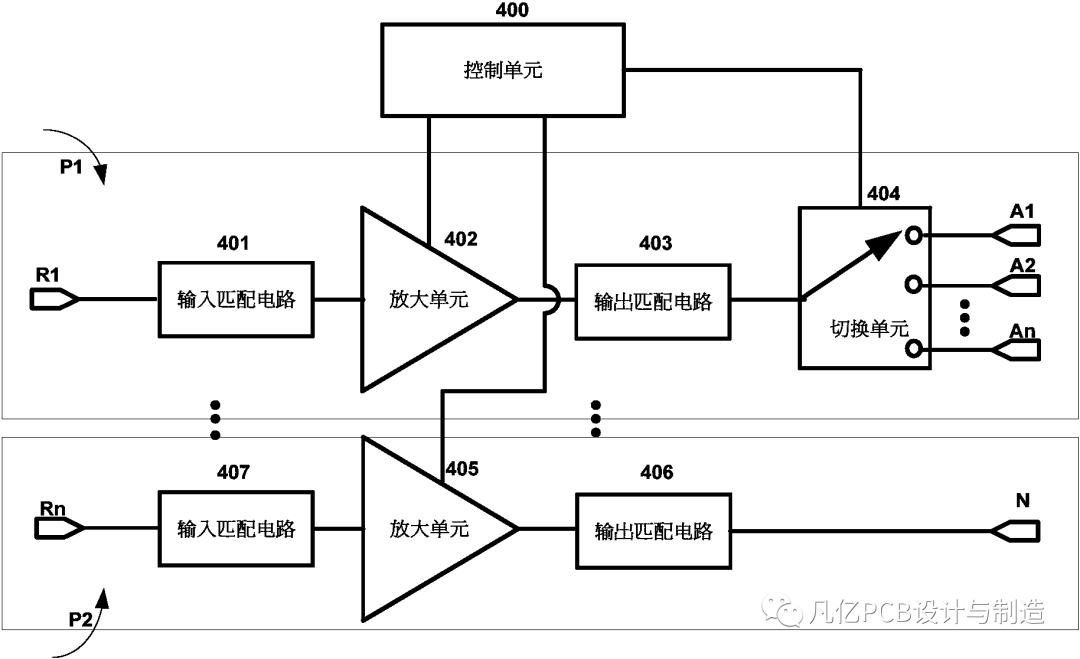

知識擴展:高速信號布線技巧

1. 多層布線

高速信號布線電路往往集成度較高,布線密度大,采用多層板既是布線所必須的,也是降低干擾的有效手段。合理選擇層數(shù)能大幅度降低印板尺寸,能充分利用中間層來設(shè)置屏蔽,能更好地實現(xiàn)就近接地,能有效地降低寄生電感,能有效縮短信號的傳輸長度,能大幅度地降低信號間的交叉干擾等。

2. 引線彎折越少越好

高速電路器件管腳間的引線彎折越少越好。高速信號布線電路布線的引線最好采用全直線,需要轉(zhuǎn)折,可用45°折線或圓弧轉(zhuǎn)折,這種要求在低頻電路中僅僅用于提高鋼箔的固著強度,而在高速電路中,滿足這一要求卻可以減少高速信號對外的發(fā)射和相互間的耦合,減少信號的輻射和反射。

3. 引線越短越好

高速信號布線電路器件管腳間的引線越短越好。引線越長,帶來的分布電感和分布電容值越大,對系統(tǒng)的高頻信號的通過產(chǎn)生很多的影響,同時也會改變電路的特性阻抗,導致系統(tǒng)發(fā)生反射、振蕩等。

4. 引線層間交替越少越好

高速電路器件管腳間的引線層間交替越少越好。所謂“引線的層間交替越少越好”,是指元件連接過程中所用的過孔越少越好。據(jù)測,一個過孔可帶來約0.5pf的分布電容,導致電路的延時明顯增加,減少過孔數(shù)能顯著提高速度。

5. 注意平行交叉干擾

高速信號布線要注意信號線近距離平行走線所引入的“交叉干擾”,若無法避免平行分布,可在平行信號線的反面布置大面積“地”來大幅度減少干擾。

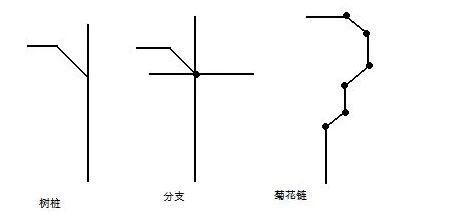

6. 避免分枝和樹樁

高速信號布線應(yīng)盡量避免分枝或者形成樹樁(Stub)。樹樁對阻抗有很大影響,可以導致信號的反射和過沖,所以我們通常在設(shè)計時應(yīng)避免樹樁和分枝。采用菊花鏈的方式布線,將對信號的影響降低。

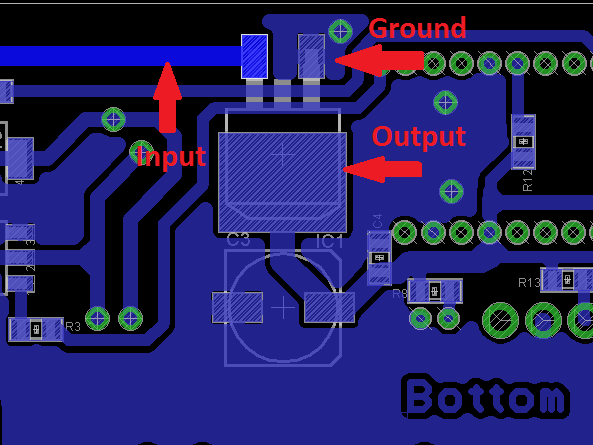

7. 信號線盡量走在內(nèi)層

高頻信號線走在表層容易產(chǎn)生較大的電磁輻射,也容易受到外界電磁輻射或者因素的干擾。將高頻信號線布線在電源和地線之間,通過電源和底層對電磁波的吸收,所產(chǎn)生的輻射將減少很多。

審核編輯:何安

-

pcb

+關(guān)注

關(guān)注

4317文章

23004瀏覽量

396256

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計中的爬電距離:確保電路板安全可靠

pcb設(shè)計中如何設(shè)置坐標原點

PCB設(shè)計與PCB制板的緊密關(guān)系

PCB設(shè)計中的常見問題有哪些?

多層pcb設(shè)計如何過孔的原理

什么是PCB扇孔,PCB設(shè)計中對PCB扇孔有哪些要求

PCB信號跨分割線需要怎么處理?

PCB設(shè)計信號線跨分割會有什么影響

PCB設(shè)計中,如何設(shè)置跳線

PCB設(shè)計中EMI傳導干擾該如何處理?

高速PCB設(shè)計中的射頻分析與處理方法

PCB設(shè)計中跨分割的處理

PCB設(shè)計中跨分割的處理

評論