本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

信號(hào)完整性是指高速產(chǎn)品設(shè)計(jì)中由互連線引起的所有問(wèn)題。包括以下幾部分:

時(shí)序

噪聲

電磁干擾(EMI)

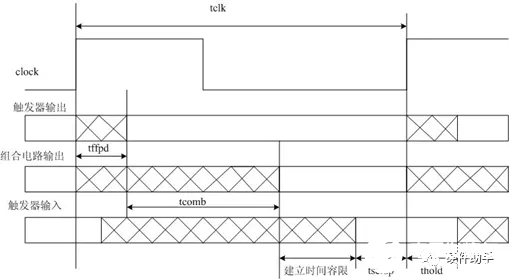

數(shù)據(jù)采樣過(guò)程通常是由時(shí)鐘信號(hào)的上升或者下降沿來(lái)觸發(fā)的。數(shù)據(jù)必須及時(shí)的到達(dá)接收端并且在接收器件開(kāi)始鎖存之前穩(wěn)定為一個(gè)非模糊的邏輯狀態(tài)。任何數(shù)據(jù)的延遲或者波形的畸變將導(dǎo)致數(shù)據(jù)傳輸?shù)氖 r(shí)序是高速系統(tǒng)的一切,信號(hào)時(shí)序取決于信號(hào)傳播的物理長(zhǎng)度引起的延遲,同時(shí)取決于抵達(dá)閥值時(shí)波形的形狀。信號(hào)波形畸變的原因可能有很多的原因。主要的包括建立時(shí)間Tsu、保持時(shí)間Th、輸出延時(shí)Tco、電路的線延遲Tdelay、時(shí)鐘延時(shí)Tpd等。

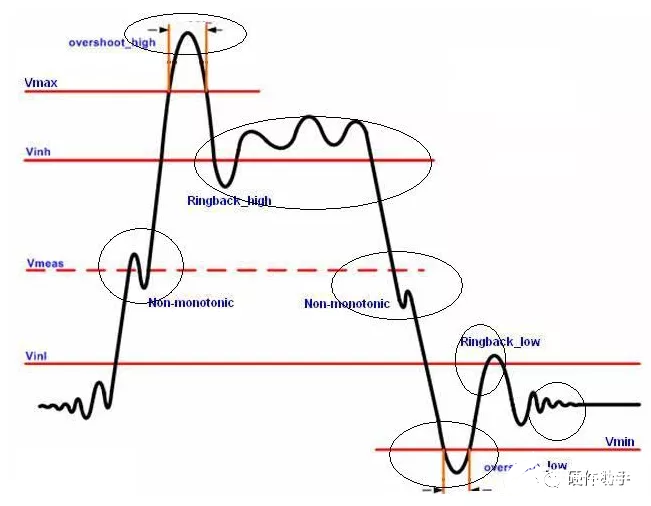

噪聲問(wèn)題具體來(lái)說(shuō)有很多種形式,例如:振鈴、反射、近端串?dāng)_、開(kāi)關(guān)噪聲、非單調(diào)性、地彈,電源反彈、衰減、容性負(fù)載、靈敏度、有損線等等。

與噪聲有關(guān)的問(wèn)題都可以從以下四個(gè)方面考慮:

單一網(wǎng)絡(luò)信號(hào)的完整性:在一個(gè)信號(hào)的信號(hào)路徑和返回路徑上由于阻抗突變引起的反射與失真。

兩個(gè)或多個(gè)網(wǎng)絡(luò)的串?dāng)_:多個(gè)信號(hào)通路之間耦合的互電容、互電感。

電源和地分配中的軌道塌陷:電源和地網(wǎng)絡(luò)中的阻抗壓降。

來(lái)自整個(gè)系統(tǒng)的電磁干擾輻射:來(lái)自元件、系統(tǒng)、外界的電磁干擾。

針對(duì)第一種情況,由于互聯(lián)線的阻抗發(fā)生變化,導(dǎo)致反射和失真(包括阻抗突變、反射、振鈴、ISI、時(shí)序等),解決的方法是:

使用均勻傳輸線;

進(jìn)行阻抗匹配。

針對(duì)第二種情況,由于兩個(gè)互連網(wǎng)絡(luò)之間的互容和互感引起容性耦合和感性耦合,而其中感性耦合占主導(dǎo)作用,對(duì)于感性耦合主導(dǎo)的噪聲,我們常常把這種串?dāng)_歸為開(kāi)關(guān)噪聲、△I噪聲、dI-dt噪聲、地彈、同步開(kāi)關(guān)噪聲(SSN)、同步開(kāi)關(guān)輸出噪聲(SSO減小信號(hào)之間的串?dāng)_的方法如下:

采用介電質(zhì)常數(shù)比較小的材料;

減小互連線的長(zhǎng)度,互連線越長(zhǎng),串?dāng)_越嚴(yán)重;

增加線之間的距離。

只要存在兩個(gè)電路,就會(huì)由于互容,一個(gè)電路的電壓產(chǎn)生電場(chǎng),影響另一個(gè)電路;只要存在兩個(gè)電流回路,就會(huì)有互感,一個(gè)回路的電流產(chǎn)生磁場(chǎng),影響另一個(gè)回路。

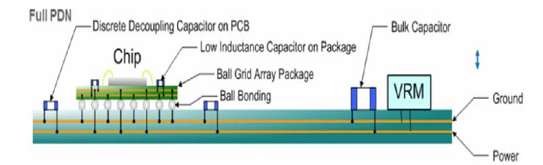

針對(duì)第三種情況,由于電壓越來(lái)越低,功耗越來(lái)越大,電源噪聲容限越來(lái)越小。因此在設(shè)計(jì)時(shí)要求電源阻抗低,地阻抗低,電源和地之間的阻抗低!所謂的低阻抗,在低頻時(shí)取決于電源線的電感,中頻時(shí)取決于板級(jí)的旁路電容,高頻時(shí)取決于片內(nèi)的分布電容陣列。具體的方法是:

相鄰電源和地分配層平面的的介質(zhì)應(yīng)該盡可能的薄,以使它們緊緊地靠近;

低電感的去耦電容;

封裝時(shí)安排多個(gè)很短的電源和地引腳;

片內(nèi)加去耦電容。

針對(duì)第四種情況,電磁干擾問(wèn)題有三個(gè)方面:噪聲源、傳播路徑和天線。電磁干擾的強(qiáng)度和頻率正相關(guān),對(duì)于共模信號(hào),電磁干擾強(qiáng)度和頻率成正比。對(duì)于差模信號(hào),電磁干擾強(qiáng)度和頻率的平方成正比。

產(chǎn)生輻射的電壓源大多數(shù)來(lái)自電源分配網(wǎng)絡(luò)(由于PDN是電路板上最大的導(dǎo)體,因此也是最容易發(fā)射及接收噪聲),因此減少軌道塌陷也能降低輻射。解決的方法從如下三個(gè)方面入手:

首先從電路設(shè)計(jì)的角度解決;

其次從接口濾波的角度阻隔;

最后才從屏蔽的角度規(guī)避。

以上就是針對(duì)信號(hào)完整性的一個(gè)簡(jiǎn)單的介紹,詳細(xì)的內(nèi)容以及分類方法各不相同,但具體問(wèn)題的解決方法大都是相通的。

-

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1397瀏覽量

95383

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速電路設(shè)計(jì)與信號(hào)完整性分析

高速PCB的信號(hào)和電源完整性問(wèn)題研究

信號(hào)完整性與電源完整性-電源完整性分析

信號(hào)完整性與電源完整性-信號(hào)的串?dāng)_

什么是信號(hào)完整性

FPGA的sata接口設(shè)計(jì)時(shí)需要注意哪些問(wèn)題

保障信號(hào)完整性的設(shè)計(jì)策略剖析

高速PCB設(shè)計(jì),信號(hào)完整性問(wèn)題你一定要清楚!

電源完整性問(wèn)題是指什么?電源完整性分析

分析高速PCB設(shè)計(jì)信號(hào)完整性問(wèn)題形成原因及方法解決

使用LTspice解決信號(hào)完整性問(wèn)題

什么時(shí)候需要注意信號(hào)完整性問(wèn)題

什么時(shí)候需要注意信號(hào)完整性問(wèn)題

評(píng)論