Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上與 Zynq UltraScale+ MPSoC VCU(H.264/H.265 視頻編解碼器)連用。

因此,調試將不同于 MIG 等傳統 Xilinx DDR 控制器。

DDR PHY 與電路板調試:

Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。

這意味著您可以使用標準 MIG 示例設計來驗證您的電路板布局是否正確,并驗證 DDR 接口是否工作正常。

建議您參考 (PG150) 基于UltraScale 架構的 FPGA 內存 IP 產品指南,以獲得關于 DDR4 示例設計的更多信息,以及用于驗證內存接口的測試工作臺。

也可以查看(Xilinx 答復 68937),了解有關調試的更多詳情。

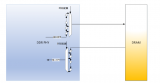

這只針對調試,而且我們不需要與設計的其余部分通信,因此建議禁用 AXI 接口(使用本機模式),并在高級選項卡中啟用高級流量生成器:

DDR 應用:

一旦 PHY 接口被驗證,如果還會出現問題,請嘗試切換到 PS-DDR,看看問題是否還會繼續。

這將表明該問題是一個 VCU 至內存的普通問題,還是一個出現在正在使用 Zynq UltraScale+ MPSoC VCU DDR 控制器的地方的特殊問題。

DDR 性能:

對于性能問題,可將板上的性能與 ZCU106 進行比較,也可以參考 (PG252) H.264/H.265 視頻編解碼器 (VCU) 產品指南。

審核編輯:何安

-

電路

+關注

關注

172文章

5849瀏覽量

171911

發布評論請先 登錄

相關推薦

撓性電路板和柔性多層電路板區別

電路板中:鋁基板與FR-4 PCB電路板有什么區別?

如何檢測電路板上的元件

電路板檢測工具都有什么

電路板測試是什么工作 電路板測試對身體有害嗎

如何制作電路板測試架

電路板測試工裝制作原理是什么

電路板測試步驟有哪些 電路板測試儀器有哪些

激光焊錫電路板:pcb外觀檢查的技巧

DDR PHY 與電路板調試

DDR PHY 與電路板調試

評論