原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處。

適用于板卡型號(hào):

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實(shí)驗(yàn)Vivado工程為“pwm_led”。

本文主要講解使用PWM控制LED,實(shí)現(xiàn)呼吸燈的效果。

1.實(shí)驗(yàn)原理

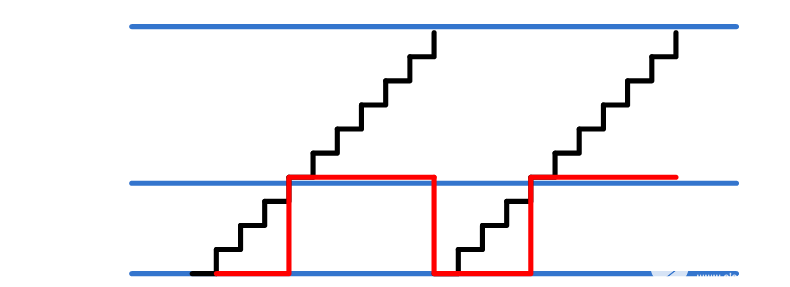

如下圖所示,用一個(gè)N比特的計(jì)數(shù)器,最大值可以表示為2的N次方,最小值0,計(jì)數(shù)器以“period”為步進(jìn)值累加,加到最大值后會(huì)溢出,進(jìn)入下一個(gè)累加周期。當(dāng)計(jì)數(shù)器值大于“duty”時(shí),脈沖輸出高,否則輸出低,這樣就可以完成圖中紅色線(xiàn)所示的脈沖占空比可調(diào)的脈沖輸出,同時(shí)“period”可以調(diào)節(jié)脈沖頻率,可以理解為計(jì)數(shù)器的步進(jìn)值。

PWM脈寬調(diào)制示意圖

PWM脈寬調(diào)制示意圖

不同的脈沖占空比的方波輸出后加在LED上,LED燈就會(huì)顯示不同的亮度,通過(guò)不斷地調(diào)節(jié)方波的占空比,從而實(shí)現(xiàn)LED燈亮度的調(diào)節(jié)。

2. 實(shí)驗(yàn)設(shè)計(jì)

PWM模塊設(shè)計(jì)非常簡(jiǎn)單,在上面的原理中已經(jīng)講到,這里不再說(shuō)原理。

| 信號(hào)名稱(chēng) | 方向 | 說(shuō)明 |

| clk | in | 時(shí)鐘輸入 |

| rst | in | 異步復(fù)位輸入,高復(fù)位 |

| period | in | PWM脈寬周期(頻率)控制。period = PWM輸出頻率 * (2 的N次方) / 系統(tǒng)時(shí)鐘頻率。顯然N越大,頻率精度越高。 |

| duty | in | 占空比控制,占空比 = duty / (2的N次方)* 100% |

PWM模塊(ax_pwm)端口

`timescale1ns/1psmoduleax_pwm#( parameterN=16//pwmbitwidth )(inputclk,inputrst,input[N-1:0]period, //pwmstepvalueinput[N-1:0]duty, //dutyvalueoutputpwm_out //pwmoutput);reg[N-1:0]period_r; //periodregisterreg[N-1:0]duty_r; //dutyregisterreg[N-1:0]period_cnt; //periodcounterregpwm_r;assignpwm_out=pwm_r;always@(posedgeclkorposedgerst)beginif(rst==1)begin period_r<={?N?{1'b0}}; ????????duty_r?<={?N?{1'b0}};endelsebegin ????????period_r?<=?period; ????????duty_r???<=?duty;endend//period?counter,?step?is?period?valuealways@(posedge?clk?orposedge?rst)beginif(rst==1) ????????period_cnt?<={?N?{1'b0}};else ????????period_cnt?<=?period_cnt?+?period_r;endalways@(posedge?clk?orposedge?rst)beginif(rst==1)begin ????????pwm_r?<=1'b0;endelsebeginif(period_cnt?>=duty_r) //ifperiodcounterisbiggerorequalstodutyvalue,thensetpwmvaluetohighpwm_r<=1'b1;else ????????????pwm_r?<=1'b0;endend

那么如何實(shí)現(xiàn)呼吸燈的效果呢?我們知道呼吸燈效果是由暗不斷的變亮,再由亮不斷的變暗的過(guò)程,而亮暗效果是由占空比來(lái)調(diào)節(jié)的,因此我們主要來(lái)控制占空比,也就是控制duty的值。

在下面的測(cè)試代碼中,通過(guò)設(shè)置period的值,設(shè)定PWM的頻率為200Hz,PWM_PLUS狀態(tài)即是增加duty值,如果增加到最大值,將pwm_flag置1,并開(kāi)始將duty值減少,待減少到最小的值,則開(kāi)始增加duty值,不斷循環(huán)。其中PWM_GAP狀態(tài)為調(diào)整間隔,時(shí)間為100us。

`timescale1ns/1psmodulepwm_test(input clk, //25MHzinput rst_n, //lowactive output led //high-off,low-on); localparamCLK_FREQ=25; //25MHzlocalparamUS_COUNT=CLK_FREQ; //1uscounterlocalparamMS_COUNT=CLK_FREQ*1000; //1mscounterlocalparamDUTY_STEP =32'd100000; //dutysteplocalparamDUTY_MIN_VALUE=32'h6fffffff; //dutyminimumvaluelocalparamDUTY_MAX_VALUE=32'hffffffff; //dutymaximumvalue localparamIDLE =0; //IDLEstatelocalparamPWM_PLUS =1;//PWMdutyplusstatelocalparamPWM_MINUS =2;//PWMdutyminusstatelocalparamPWM_GAP =3;//PWMdutyadjustmentgapwire pwm_out; //pwmoutputreg[31:0] period; //pwmstepvaluereg[31:0] duty; //dutyvaluereg pwm_flag; //dutyvalueplusandminusflag,0:plus;1:minusreg[3:0] state;reg[31:0] timer; //dutyadjustmentcounterassignled=~pwm_out;//ledlowactivealways@(posedgeclkornegedgerst_n)begin if(rst_n==1'b0) begin period <=32'd0; timer? <=32'd0; duty? <=32'd0; pwm_flag? <=1'b0; state? <=?IDLE; end else case(state) IDLE: begin period? <=32'd17179;//The?pwm?step?value,?pwm?200Hz(period?=?200*2^32/50000000) state?? <=?PWM_PLUS; duty??? <=?DUTY_MIN_VALUE; end PWM_PLUS?: begin if(duty?>DUTY_MAX_VALUE-DUTY_STEP) //ifdutyisbiggerthanDUTYMAXVALUEminusDUTY_STEP,begintominusdutyvalue begin pwm_flag <=1'b1; duty??? <=?duty?-?DUTY_STEP?; end else begin pwm_flag? <=1'b0; duty??? <=?duty?+?DUTY_STEP?; end state?? <=?PWM_GAP?; end PWM_MINUS?: begin if(duty?=US_COUNT*100)//adjustmentgapis100us begin if(pwm_flag) state<=?PWM_MINUS?; else state?<=?PWM_PLUS?; timer?<=32'd0; end else begin timer?<=?timer?+32'd1; end end default: begin state?<=?IDLE; end endcaseend//Instantiate?pwm?moduleax_pwm#(.N(32))ax_pwm_m0(.clk??????(clk),.rst??????(~rst_n),.period???(period),.duty?????(duty),.pwm_out??(pwm_out)); endmodule

3. 下載驗(yàn)證

生成bitstream,并下載bit文件,可以看到PL LED1燈產(chǎn)生呼吸燈效果。PWM是比較常用的模塊,比如風(fēng)扇轉(zhuǎn)速控制,電機(jī)轉(zhuǎn)速控制等等。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21669瀏覽量

601866 -

PWM

+關(guān)注

關(guān)注

114文章

5144瀏覽量

213409 -

Zynq

+關(guān)注

關(guān)注

9文章

608瀏覽量

47128 -

MPSoC

+關(guān)注

關(guān)注

0文章

198瀏覽量

24252 -

呼吸燈

+關(guān)注

關(guān)注

10文章

110瀏覽量

42704

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件

在米爾電子MPSOC實(shí)現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬(wàn)兆以太網(wǎng)推流

迅為iTOP-RK3568開(kāi)發(fā)板驅(qū)動(dòng)開(kāi)發(fā)指南-第十八篇 PWM

在米爾電子MPSOC實(shí)現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬(wàn)兆以太網(wǎng)推流

《DNK210使用指南 -CanMV版 V1.0》第十章 板卡信息實(shí)驗(yàn)

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

ALINX FPGA+GPU異架構(gòu)視頻圖像處理開(kāi)發(fā)平臺(tái)介紹

一個(gè)更適合工程師和研究僧的FPGA提升課程

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產(chǎn)品

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設(shè)計(jì)PCB的步驟詳解

采用UltraScale/UltraScale+芯片的DFX設(shè)計(jì)注意事項(xiàng)

針對(duì)UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(2)

針對(duì)UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸燈實(shí)驗(yàn)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸燈實(shí)驗(yàn)

評(píng)論