原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實(shí)驗(yàn)VIvado工程為“hdmi_out_test”。

前面我們介紹了led閃燈實(shí)驗(yàn),只是為了了解Vivado的基本開發(fā)流程,本章這個實(shí)驗(yàn)相對LED閃燈實(shí)驗(yàn)復(fù)雜點(diǎn),做一個HDMI輸出的彩條,這也是我們后面學(xué)習(xí)顯示、視頻處理的基礎(chǔ)。實(shí)驗(yàn)還不涉及到PS系統(tǒng),從實(shí)驗(yàn)設(shè)計可以看出如果要非常好的使用ZYNQ芯片,需要良好的FPGA基礎(chǔ)知識。

1. 硬件介紹

由于開發(fā)板上只有DP可以顯示,但卻是PS端的,PL端沒有HDMI的接口,因此我們采用AN9134的HDMI擴(kuò)展模塊實(shí)現(xiàn)HDMI顯示。將24位RGB編碼輸出TMDS差分信號。SIL9134功能強(qiáng)大,本實(shí)驗(yàn)只使用其中一小部分,將RGB24視頻數(shù)據(jù)顯示出來即可。

SI9134芯片需要通過I2C總線配置寄存器才能正常工作,從原理圖中可以看出I2C總線連接到PL端的IO,可以通過PL直接配置。

2. 程序設(shè)計

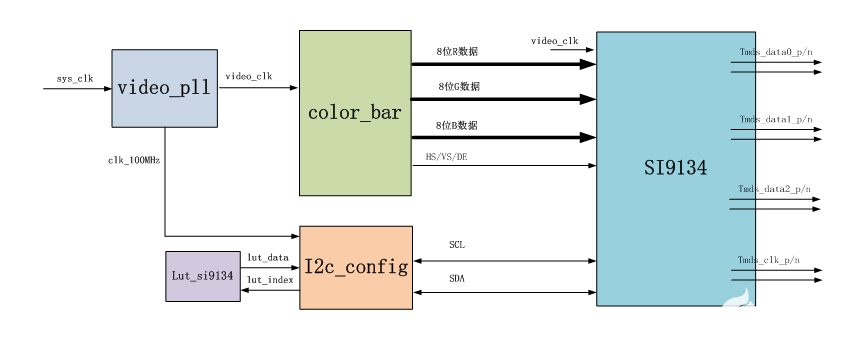

本實(shí)驗(yàn)實(shí)現(xiàn)通過HDMI顯示彩條,實(shí)驗(yàn)中設(shè)計了視頻時序發(fā)生和彩條發(fā)生模塊“color_bar.v”,I2C Master 寄存器配置模塊“i2c_config.v”,配置數(shù)據(jù)查找表模塊“l(fā)ut_si9134.v”。

具體代碼在這里不再一一介紹了,大家自己去看。下面針對每個模塊實(shí)現(xiàn)的功能給大家做一下簡介:

頂層模塊top.v是項(xiàng)目的頂層文件,主要是實(shí)例化4個子模塊(時鐘模塊vidio_pll, 彩條生成模塊color_bar和I2C配置模塊i2c_config和配置查找表模塊lut_si9134。

彩條產(chǎn)生模塊color_bar.v是產(chǎn)生8種顏色的VGA格式的彩條,彩條分別為白、黃、青、綠、紫、紅、藍(lán)和黑。產(chǎn)生分辨率為1920x1080刷新率為60Hz的彩條,也就是所謂的1080P的高清視頻圖像。所以這個模塊會輸出R(8位)G(8位)B(8位)圖像信號、行同步、列同步和數(shù)據(jù)有效信號。

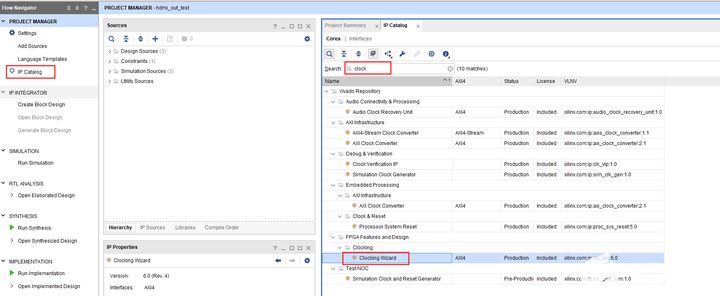

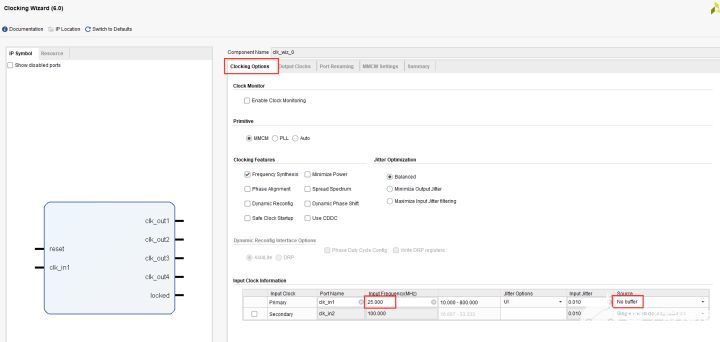

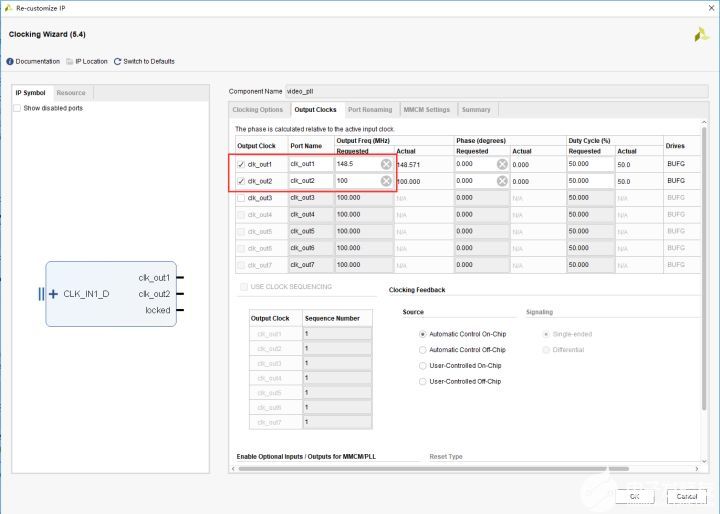

時鐘模塊video_pll調(diào)用的是一個Xilinx提供的時鐘IP,通過輸入的系統(tǒng)時鐘產(chǎn)生一個100Mhz時鐘和一個1080P的像素時鐘148.5Mhz。生成時鐘IP的方法是點(diǎn)擊Project Manager目錄下的IP Catalog,再選擇FPGA Features and Design->Clocking->Clocking Wizard圖標(biāo)。

3. 下載調(diào)試

保存工程并編譯生成bit文件,連接HDMI模塊到J15擴(kuò)展口,連接HDMI接口到HDMI顯示器,需要注意,這里使用1920x1080@60Hz,請確保自己的顯示器支持這個分辨率。

硬件連接圖(J15擴(kuò)展口)

下載后顯示器顯示如下圖像

4. 實(shí)驗(yàn)總結(jié)

本實(shí)驗(yàn)初步接觸到視頻顯示,涉及到視頻知識,這不是zynq學(xué)習(xí)的重點(diǎn),所以沒有詳細(xì)介紹,但zynq在視頻處理領(lǐng)域用途廣泛,需要學(xué)習(xí)者有良好的基礎(chǔ)知識。實(shí)驗(yàn)中僅僅使用PL來驅(qū)動HDMI芯片,包括I2C寄存器配置,當(dāng)然I2C的配置還是使用PS來配置比較合適。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601873 -

HDMI

+關(guān)注

關(guān)注

32文章

1664瀏覽量

151666 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

4945瀏覽量

97201 -

Zynq

+關(guān)注

關(guān)注

9文章

608瀏覽量

47128 -

MPSoC

+關(guān)注

關(guān)注

0文章

198瀏覽量

24252

發(fā)布評論請先 登錄

相關(guān)推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

在米爾電子MPSOC實(shí)現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬兆以太網(wǎng)推流

在米爾電子MPSOC實(shí)現(xiàn)12G SDI視頻采集H.265壓縮SGMII萬兆以太網(wǎng)推流

《DNK210使用指南 -CanMV版 V1.0》第十四章 按鍵輸入實(shí)驗(yàn)

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

【北京迅為】iTOP-i.MX6開發(fā)板使用手冊第四部分固件編譯第十四章非設(shè)備樹Android4.4系統(tǒng)編譯

才茂亮相第十四屆配電技術(shù)應(yīng)用大會

一個更適合工程師和研究僧的FPGA提升課程

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產(chǎn)品

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設(shè)計PCB的步驟詳解

采用UltraScale/UltraScale+芯片的DFX設(shè)計注意事項(xiàng)

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(2)

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十四章HDMI輸出實(shí)驗(yàn)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十四章HDMI輸出實(shí)驗(yàn)

評論