原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

1. 軟件環境

軟件開發環境基于Vivado 2020.1

2. 硬件環境

| 開發板型號 | 芯片型號 |

| AXU2CGA | xczu2cg-sfvc784-1-e |

| AXU2CGB | xczu2cg-sfvc784-1-e |

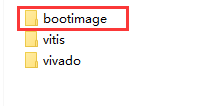

3. 批處理下載QSPI Flash

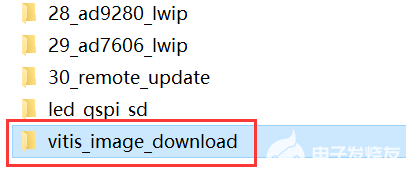

所有的工程目錄下都有個bootimage文件夾,存放了對應的BOOT.bin文件,可將此文件拷貝到Vitis_image_download文件夾,覆蓋原有的BOOT.bin。也可以把BOOT.bin放到SD卡啟動驗證功能

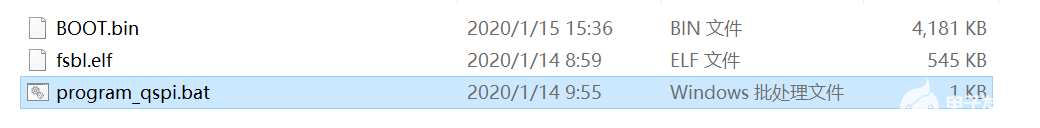

vitis_image_download文件夾在course_s2目錄下面,進入文件夾,右鍵點擊program_qspi.bat,打開編輯

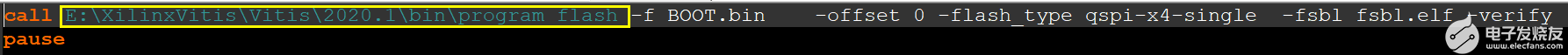

將program_flash路徑改成自己的軟件安裝路徑,保存并關閉。

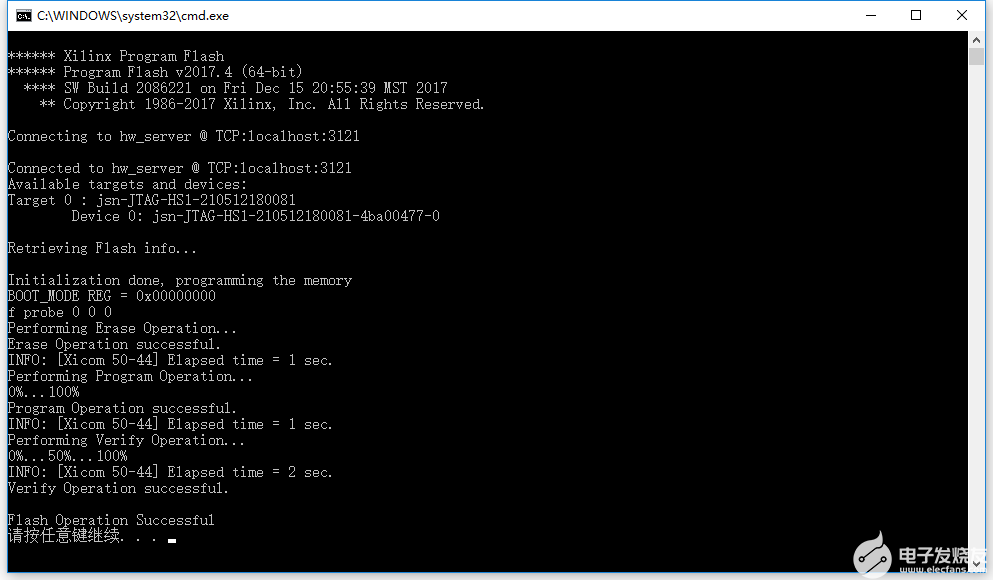

雙擊program_qspi.bat,即可下載BOOT.BIN到QSPI FLASH,建議用JTAG模式下載。

也可以采用SD卡啟動方法,把BOOT.bin文件拷貝到SD內啟動。

4. 批處理建立Vitis工程

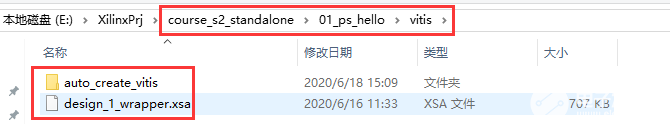

由于Vitis工程編譯后占用空間較大,因此為了節省大家寶貴的時間,我們提供了Vitis工程的批處理tcl腳本,在每個工程下都有個vitis文件夾,里面包含硬件描述文件xx.xsa,以及自動創建工程的腳本

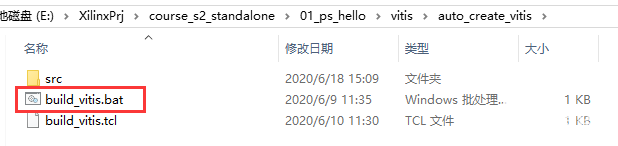

大家需要做的是編輯auto_create_vitis文件夾中的build_vitis.bat文件

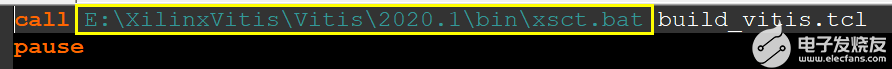

將黃色框中的xsct.bat路徑換成自己安裝的路徑,路徑為xx\Vitis\2020.1\bin\xsct.bat

保存之后,再雙擊build_vitis.bat就可以創建工程了

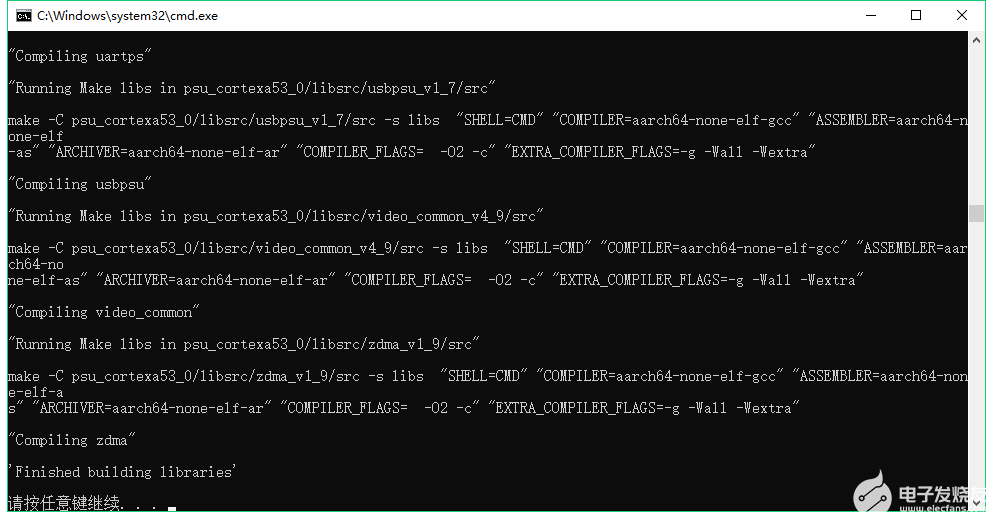

編譯結束,按任意鍵退出

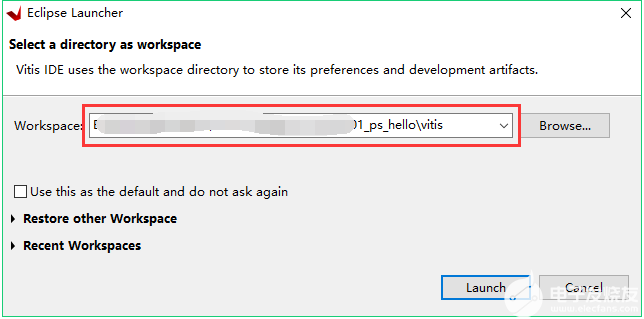

打開Vitis軟件,選擇工程路徑,Launch

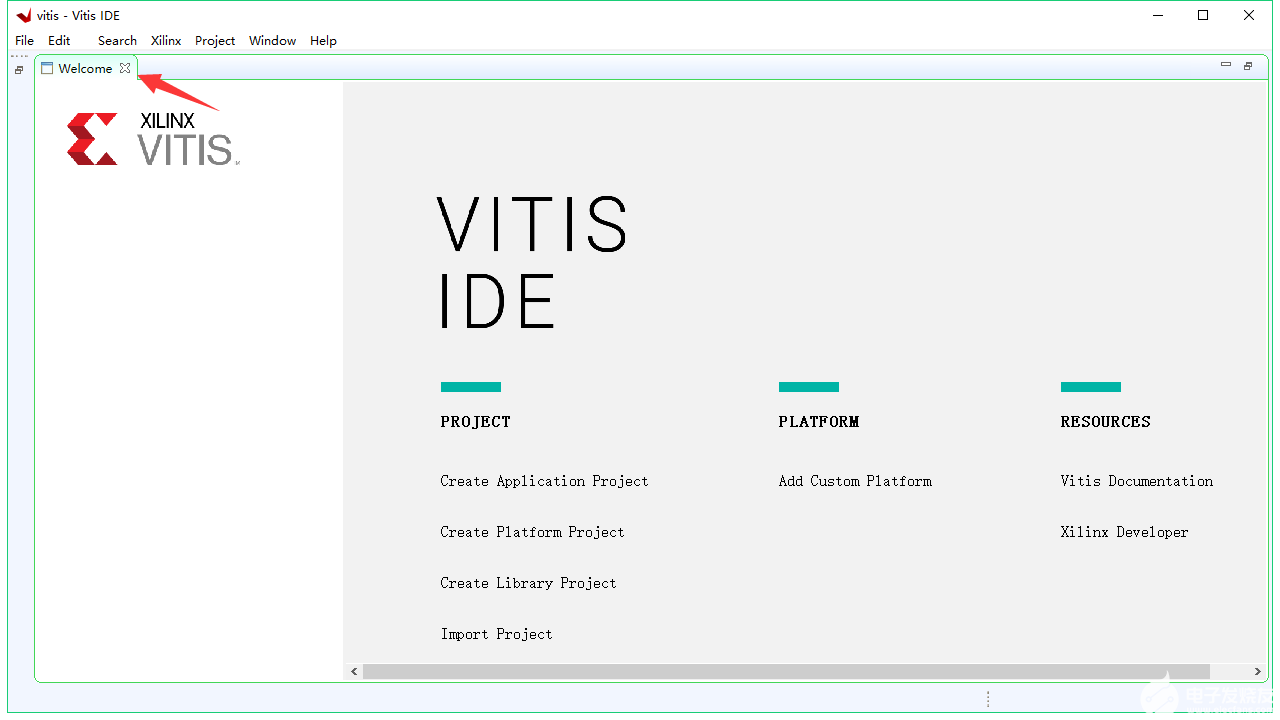

打開后,關閉Welcom界面

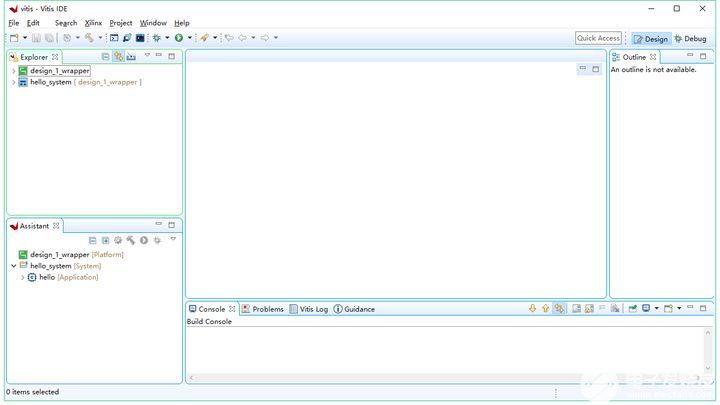

工程即可使用

-

FPGA

+關注

關注

1620文章

21506瀏覽量

598812 -

編譯

+關注

關注

0文章

646瀏覽量

32662 -

Zynq

+關注

關注

9文章

604瀏覽量

46996 -

MPSoC

+關注

關注

0文章

194瀏覽量

24187 -

Vitis

+關注

關注

0文章

145瀏覽量

7310

發布評論請先 登錄

相關推薦

達實智能亮相第十七屆高工鋰電產業峰會

南方測繪亮相第十七屆中國智慧城市大會

一個更適合工程師和研究僧的FPGA提升課程

FPGA的高速接口應用注意事項

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產品

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設計PCB的步驟詳解

針對UltraScale/UltraScale+芯片DFX應考慮的因素有哪些(2)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis準備工程及注意事項

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis準備工程及注意事項

評論