原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

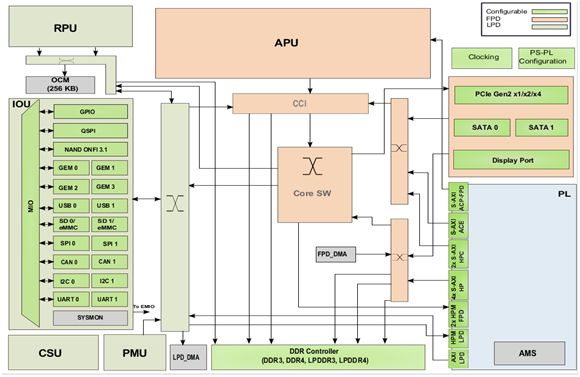

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目錄為“ps_hello/vivado”

軟件工程師工作內容

以下為軟件工程師負責內容。

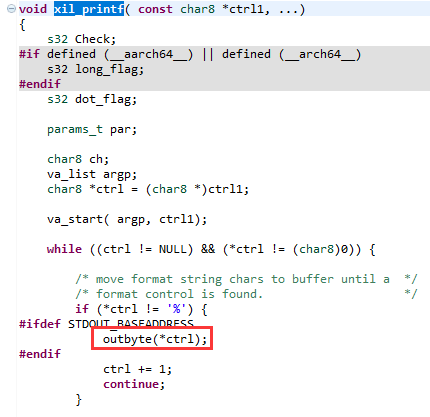

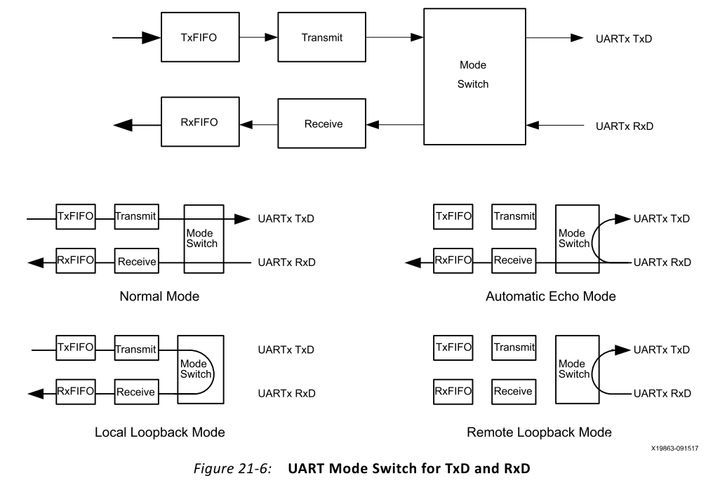

在前面的實驗中,大家或多或少會發現有打印信息的情況,主要是調用”xil_printf”或”printf”,但是通過什么打印信息呢?我們還記得打印信息之前設置了串口,是的,確實是串口,但這些函數是如何調用串口呢?其實我們可以在”xil_printf”函數定義中看到,注意outbyte函數就是調用UART打印的。

再進入outbye的函數,即可看到調用了PS端UART的函數,得以在串口中顯示。

除了打印信息之外,如果我們想用UART進行數據傳輸呢?本章便來介紹PS端UART的讀寫控制,實驗中,每隔1S向外發送一串字符,如果收到數據,產生中斷,并將收到的數據再發送出去。

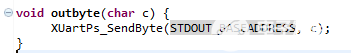

1.UART模塊介紹

以下是UART模塊的結構圖,TxFIFO和RxFIFO都為64字節。

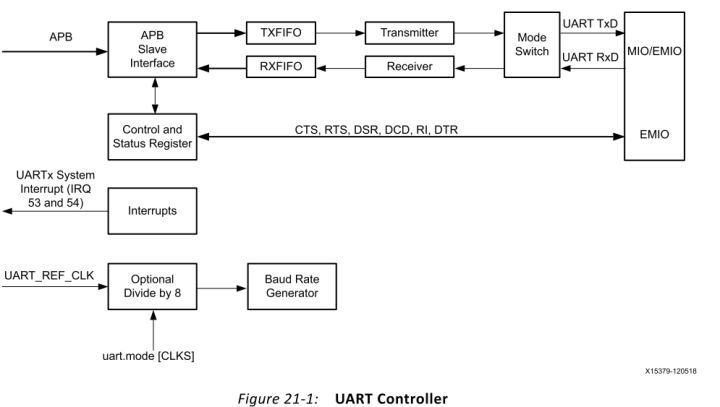

下圖為UART的四種模式

可以用remote loopback mode測試物理電路是否正常,使用API函數XUartPs_SetOperMode

2. Vitis程序開發

1) 本實驗流程如下:

主程序流程:

UART初始化設置UART模式設置數據格式設置中斷發送UART數據檢查是否收到數據如果收到,發送收到的數據,如果沒有,等待1秒鐘,繼續發數據

中斷程序流程:

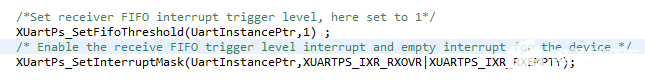

中斷初始化設置接收FIFO trigger中斷寄存器,設置為1,即收到一個數據就中斷打開接收trigger中斷REMPTY及接收FIFO空中斷RTRIG

中斷服務程序:

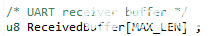

判斷狀態寄存器是trigger還是empty清除相應中斷trigger狀態讀取RxFIFO數據,empty狀態將接收標志ReceivedFlag置1

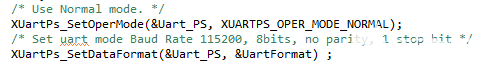

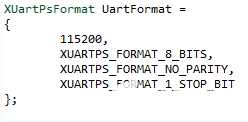

2) 在main函數中進行模式的設置,可以直接調用函數,設置為正常模式,數據格式設置為波特率115200,數據8bit,無校驗位,1bit停止位。UartFormat定義在uart_parameter.h中。

3) 中斷控制器程序初始化可參考按鍵中斷方式,用法類似。

4) 在main函數中將trigger level設置為1,打開trigger和empty中斷。

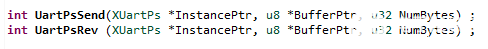

5) 數據的發送和接收函數參考了UARTPS的XUartPs_Send和XUartPs_Rev函數,但它們會打開某些中斷,不符合預期,因此做了修改。

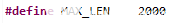

在接收緩存中設置了最大2000字節的緩沖,可以根據需要修改。

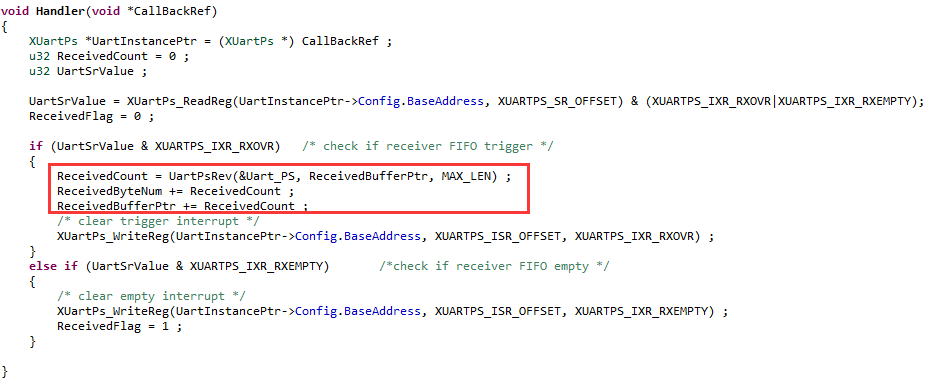

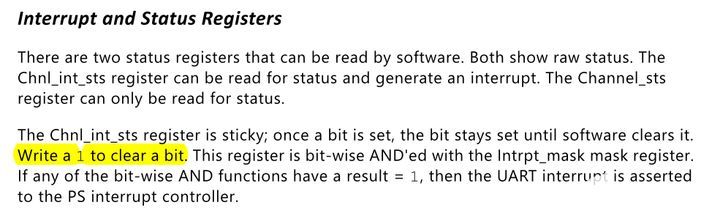

6) 在中斷服務程序中,將ReceivedBufferPtr指針地址和ReceivedByteNum加上接收到的個數,如果FIFO空了,將ReceivedFlag置為1。同時向中斷狀態寄存器寫數據,清除中斷。

Ug1085 UART清除中斷

Ug1085 UART清除中斷

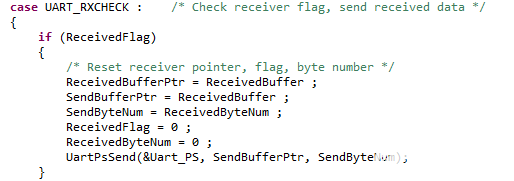

7) 在main函數中,將ReceivedFlag和ReceivedByteNum清零,ReceivedBufferPtr指針復位。

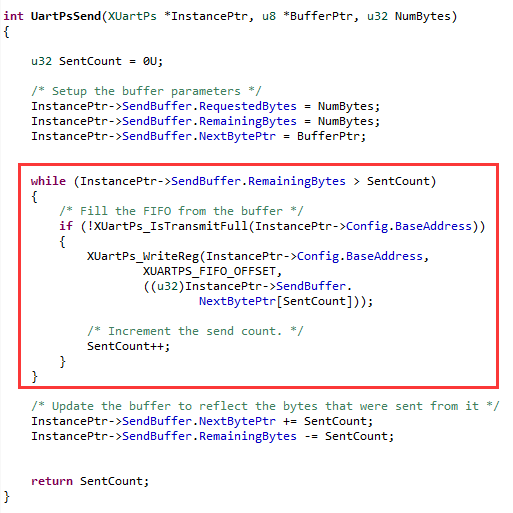

8) Uart發送函數中,判斷TxFIFO是否滿,否則繼續發送,直到計數達到NumBytes

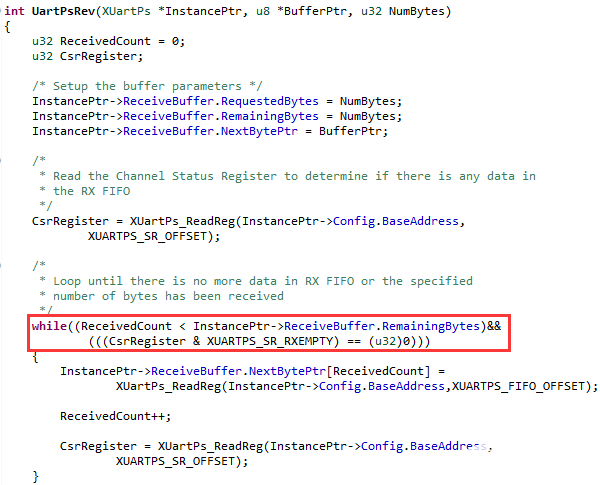

9) Uart接收函數中,判斷接收RxFIFO是否為空,否則繼續讀數據,NumBytes為需要讀取的數據個數,但如果接收的FIFO空了,計數沒有達到這個值,也會結束此函數。

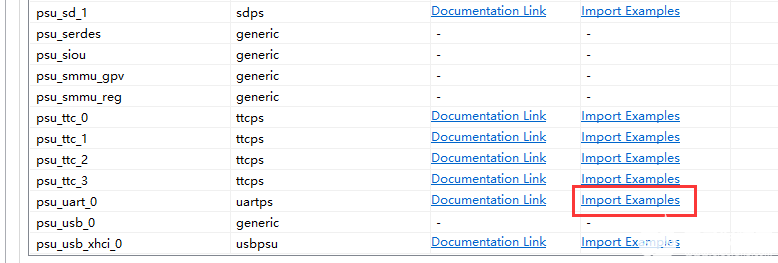

10) 除了自己寫程序外,還可以從system.mss中導入模塊的例子,參考Xilinx提供的程序,方便學習。

3. 板上驗證

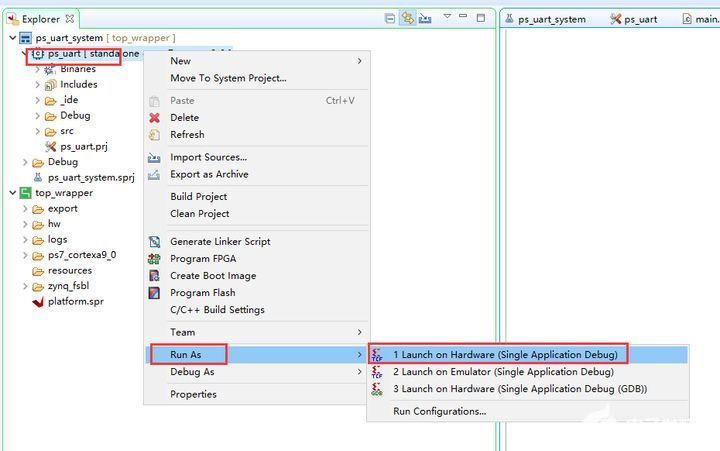

1) 接下來下載程序

2) 打開工程目錄下的串口調試工具

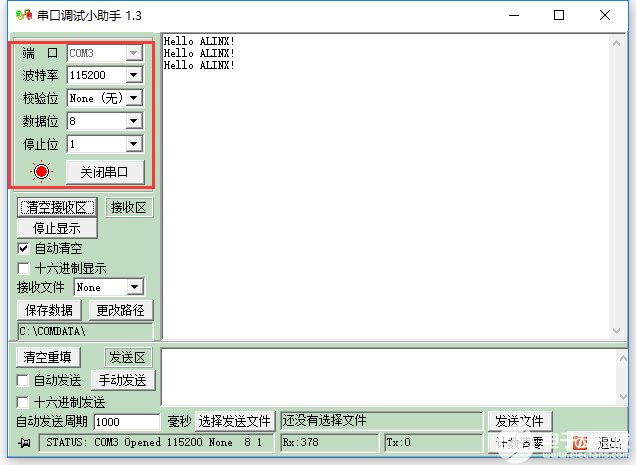

3) 設置好參數如下,打開串口,即可看到打印信息。

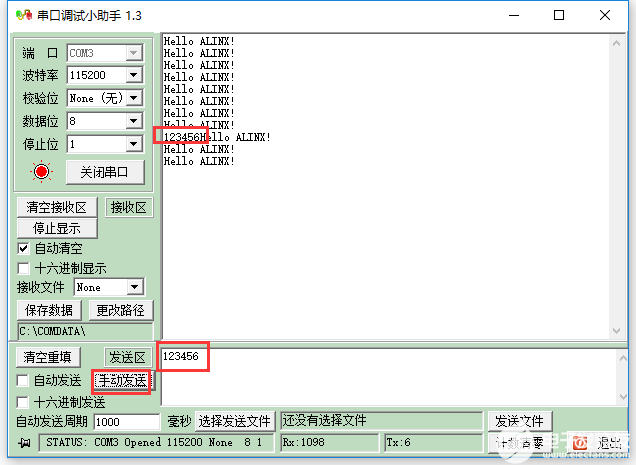

4) 在發送區填入數據,點擊手動發送,即可看到接收區的數據。

4. 總結

本章學習了UART的發送與接收,以及中斷的使用,希望大家能養成良好的習慣,多看文檔,理解原理,能對系統的認識有很大提高。

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601872 -

串口

+關注

關注

14文章

1543瀏覽量

76198 -

uart

+關注

關注

22文章

1227瀏覽量

101177 -

Zynq

+關注

關注

9文章

608瀏覽量

47128 -

MPSoC

+關注

關注

0文章

198瀏覽量

24252

發布評論請先 登錄

相關推薦

明德揚視頻分享點撥FPGA課程--第二十一章 ?矩陣鍵盤工程

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

第二十一講 組合邏輯電路中的競爭冒險

模擬電路網絡課件 第二十一節:場效應管與BJT放大電路的比較

閑話Zynq UltraScale+ MPSoC(連載1)

閑話Zynq UltraScale+ MPSoC(連載5)

Zynq UltraScale+ MPSoC的發售消息

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章 MPSoC芯片介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC的隔離設計示例

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART讀寫控制

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART讀寫控制

評論