原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實驗Vivado工程目錄為“ps_emio/vivado”。

實驗vitis工程目錄為“ps_emio/vitis”。

如果想用PS點亮PL的LED燈,該如何做呢?一是可以通過EMIO控制PL端LED燈,二是通過AXI GPIO的IP實現控制。本章介紹如何使用EMIO控制PL端LED燈的亮滅。同時也介紹了,利用EMIO連接PL端按鍵控制PL端LED燈。

1. 原理介紹

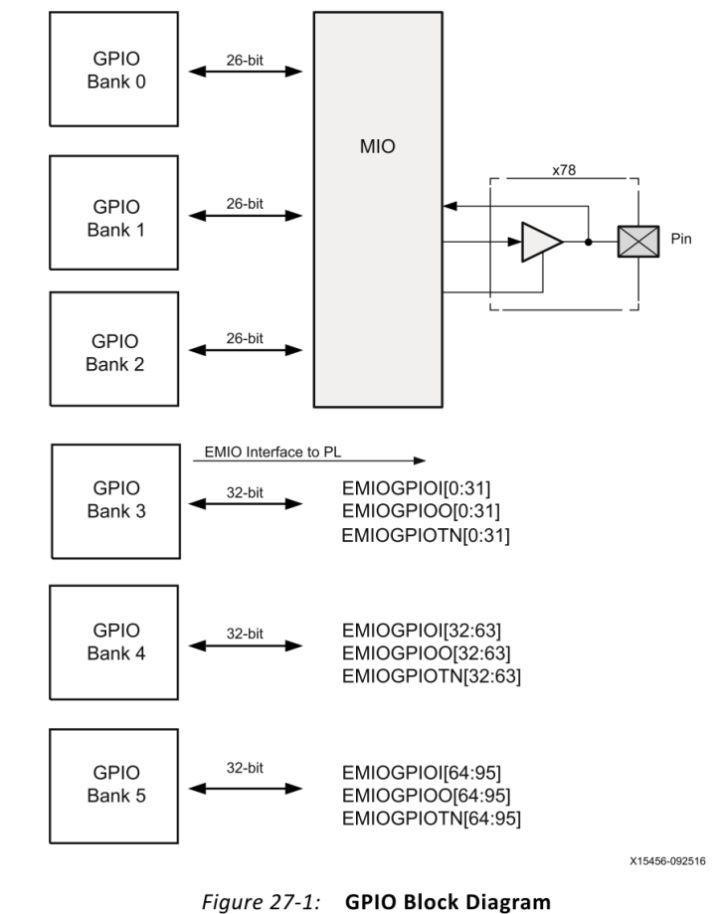

先來了解GPIO的BANK分布,從圖中可知BANK0~BANK2的MIO有78個。BANK3~BANK5的EMIO有96個,本章就是采用EMIO控制PL端LED。

以下為FPGA工程師負責內容。

2. Vivado工程建立

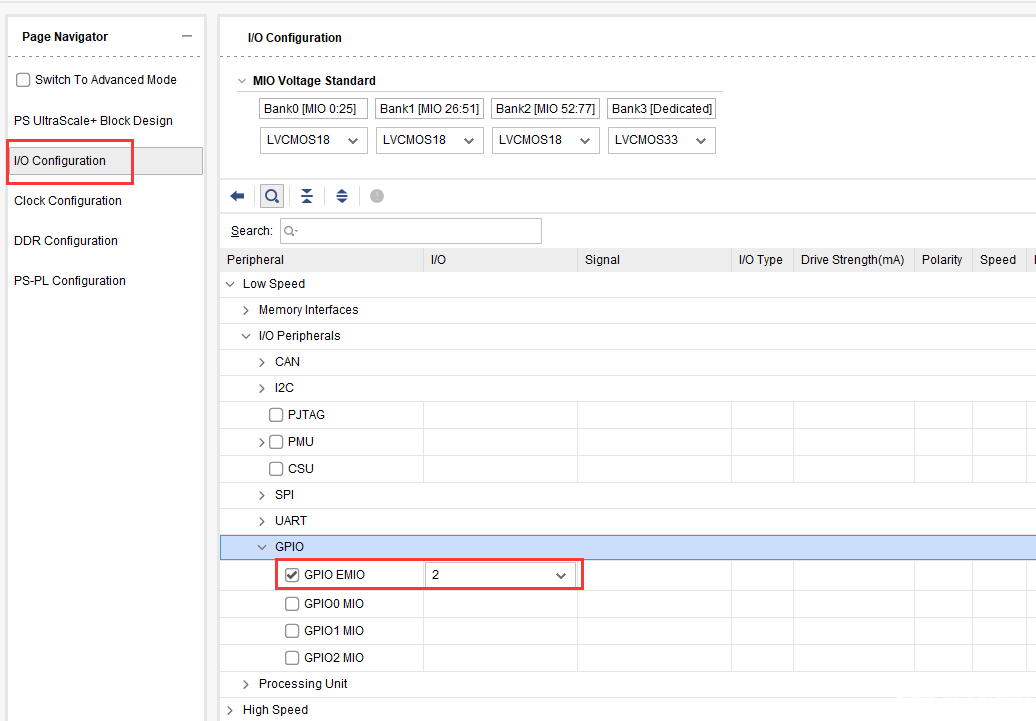

1)以ps_hello工程為基礎,另存為一個名為ps_emio的工程,打開ZYNQ配置,把GPIO EMIO勾選上。利用PL端的1個LED,1個按鍵,在MIO配置中選擇EMIO的位寬為2位,配置結束,點擊OK。

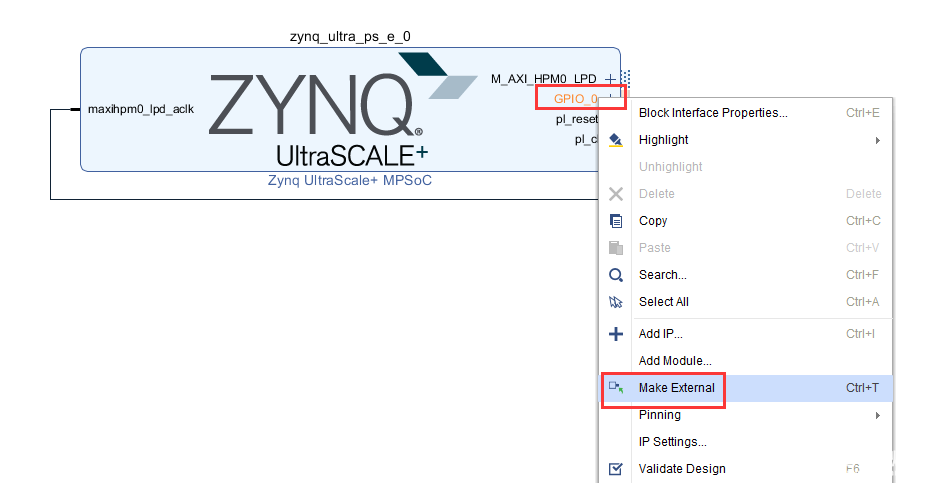

2)點擊多出的GPIO_0端口右鍵選擇Make External,將端口信號導出

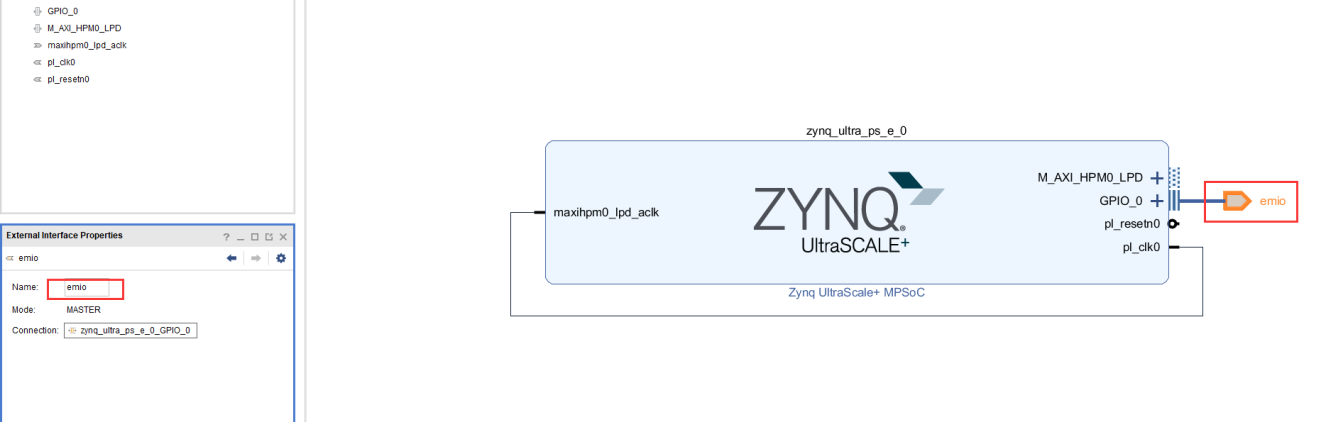

3)點擊引腳并修改引腳名稱為emio,也可以根據自己需求修改名稱。保存設計。

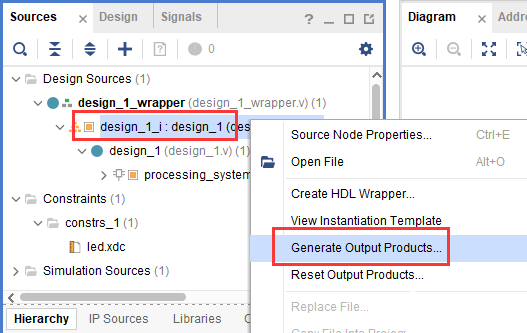

4)點擊xx.bd右鍵選擇Generate Output Products,重新生成輸出文件

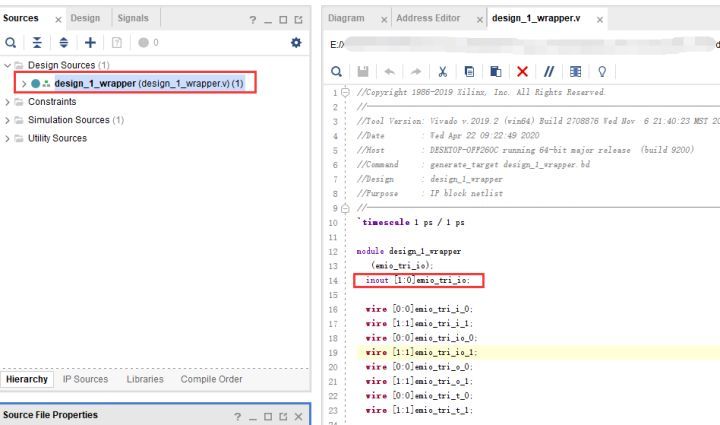

5)結束后,頂層文件會更新出新的管腳,下面需要對其進行引腳綁定

3. XDC文件約束PL管腳

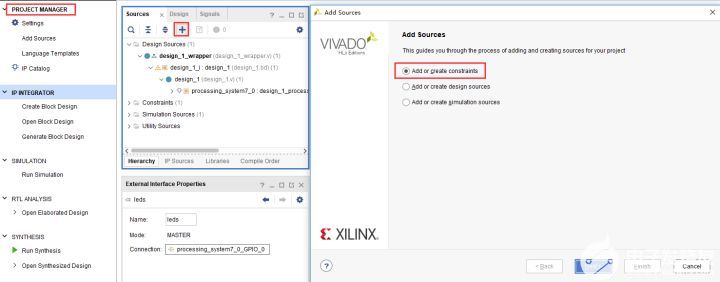

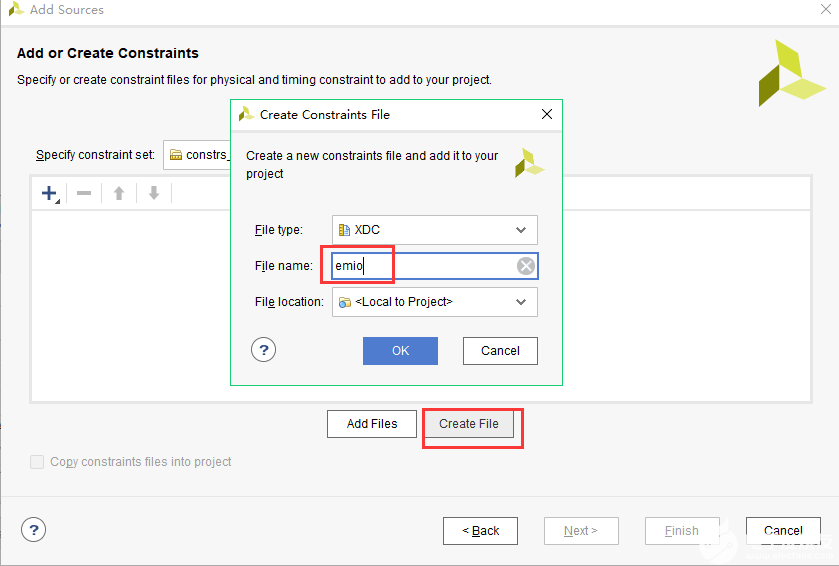

1)新建XDC文件,綁定PL端引腳

設置文件名稱為emio

2)emio.xdc添加一下內容,端口名稱一定要和頂層文件端口一致

| ##################Compress Bitstream############################set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]set_property IOSTANDARD LVCMOS33 [get_ports {emio_tri_io[*]}]#pl ledset_property PACKAGE_PIN W13 [get_ports {emio_tri_io[0]}]#pl keyset_property PACKAGE_PIN AA13 [get_ports {emio_tri_io[1]}] |

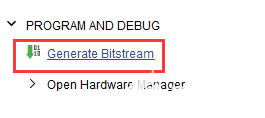

3)生成bit文件

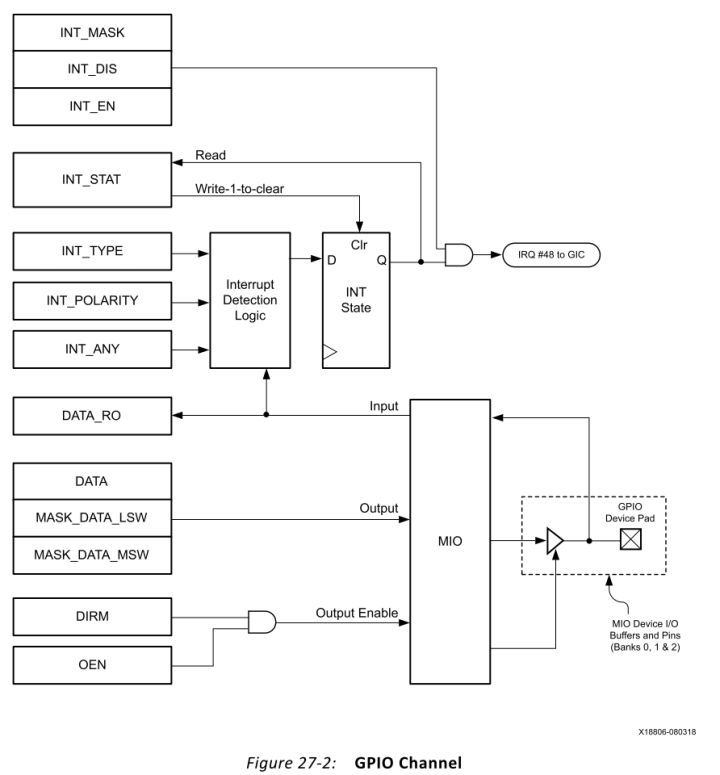

4)雖然說沒有用到PL端的邏輯,但是用到了PL端的引腳,因此導出硬件要選擇“Include bitstream”

軟件工程師工作內容

以下為軟件工程師負責內容。

4. Vitis程序編寫

4.1 EMIO點亮PL端LED燈

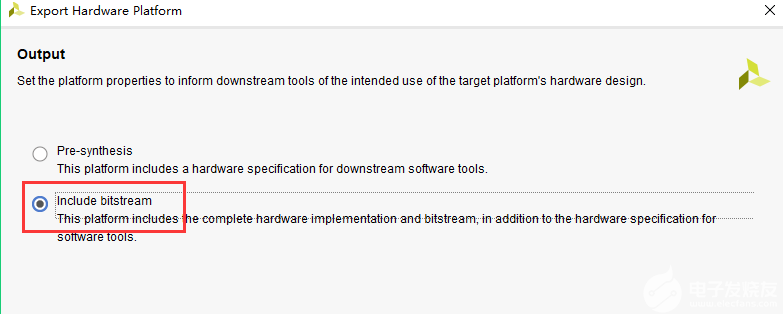

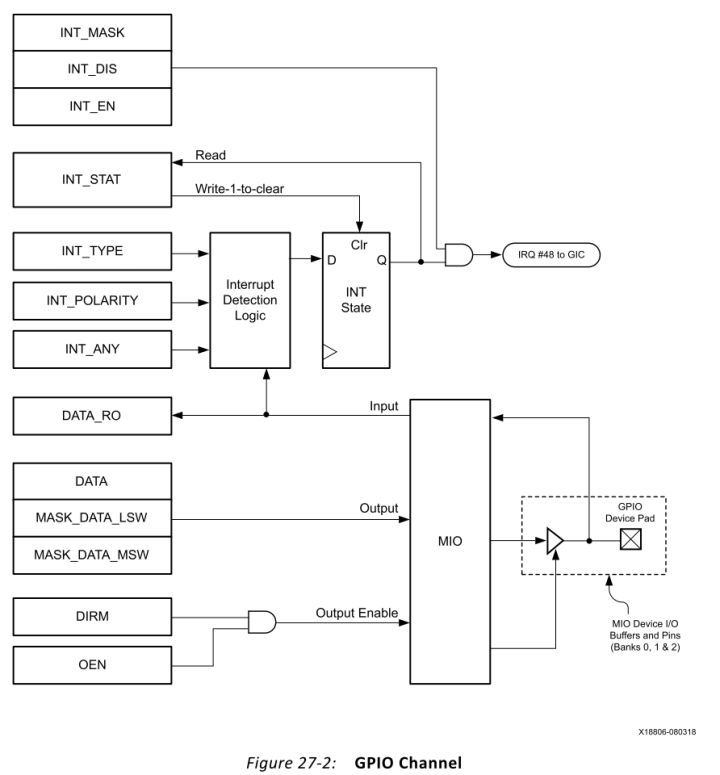

下圖為GPIO的控制框圖,實驗中會用到輸出部分的寄存器,數據寄存器DATA,數據掩碼寄存器MASK_DATA_LSW,MASK_DATA_MSW,方向控制寄存器DIRM,輸出使能控制器OEN。

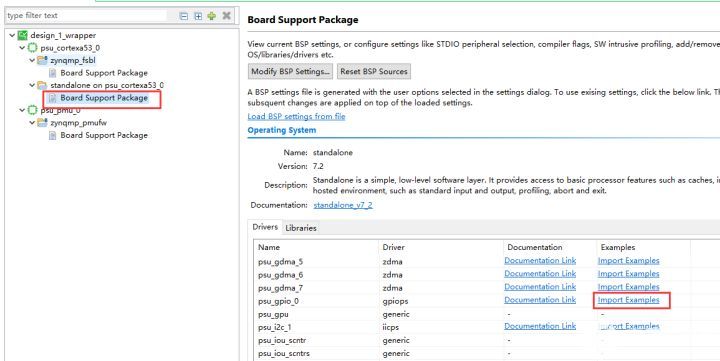

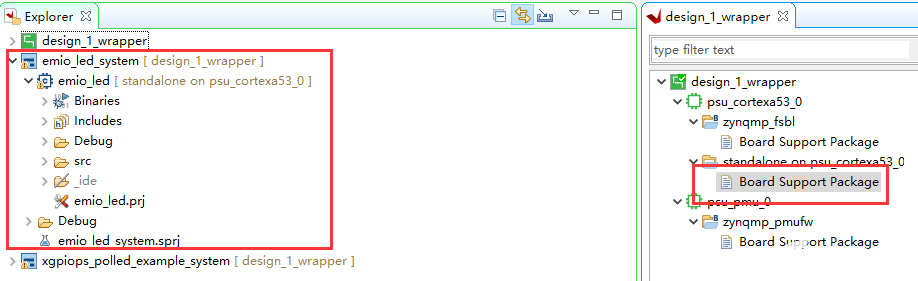

一開始編寫代碼可能會無從下手,我們可以導入Xilinx提供的example工程,在BSP里找到psu_gpio_0,點擊Import Examples

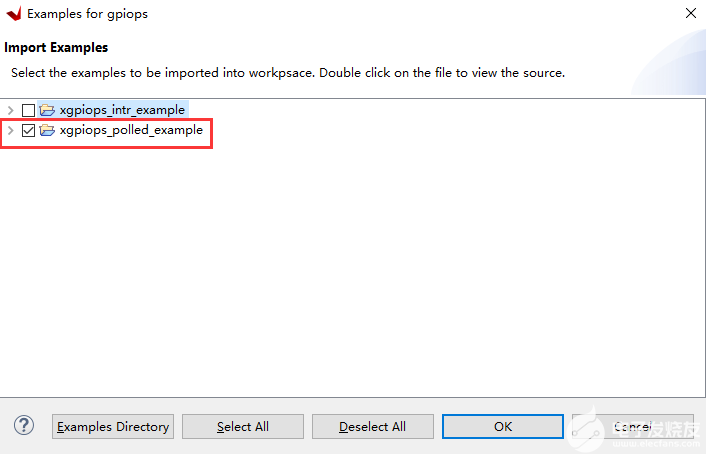

在彈出窗口選擇“xgpiops_polled_example”,點擊OK

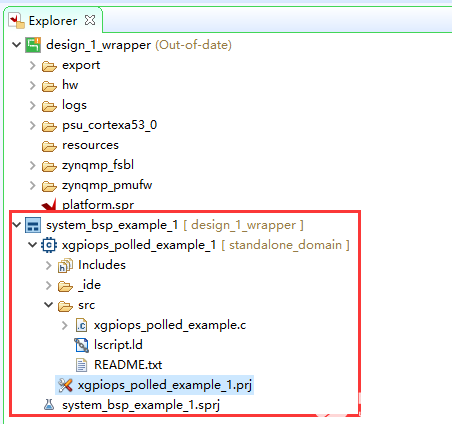

會出現一個新的APP工程

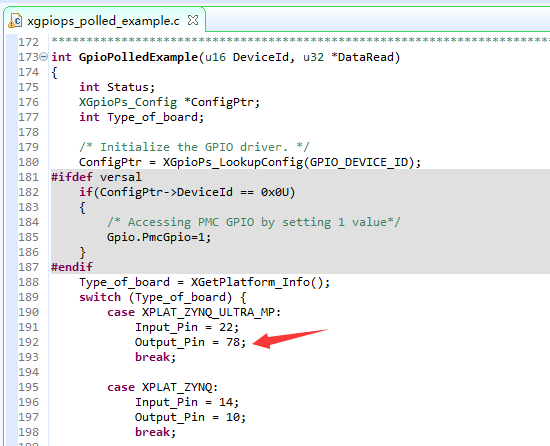

1)這個example工程是測試PS端MIO的輸入輸出的,由于LED是EMIO引出來的,EMIO的MIO號是從78開始的,需要在文件中修改Output_pin為78,測試LED燈。

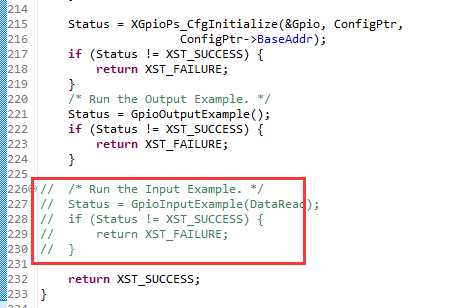

由于只測試LED燈,也就是輸出,我們把輸入功能注釋掉。保存文件。

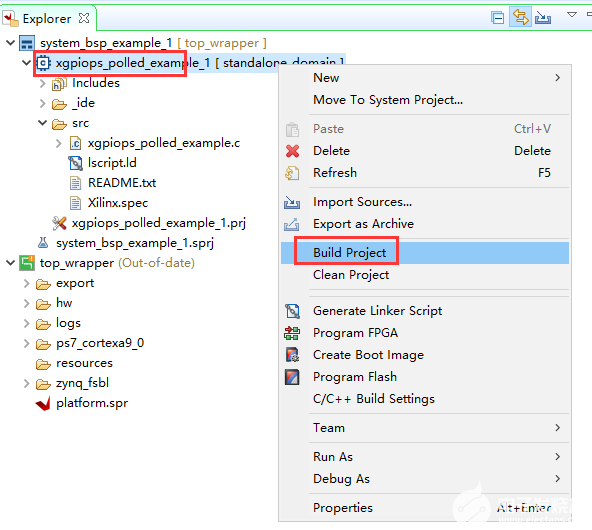

2)編譯工程

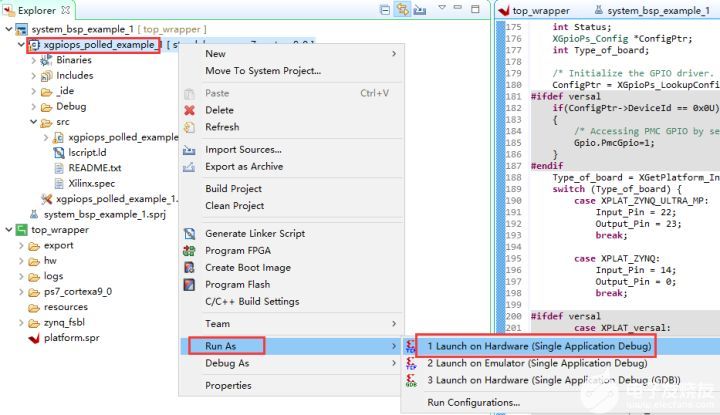

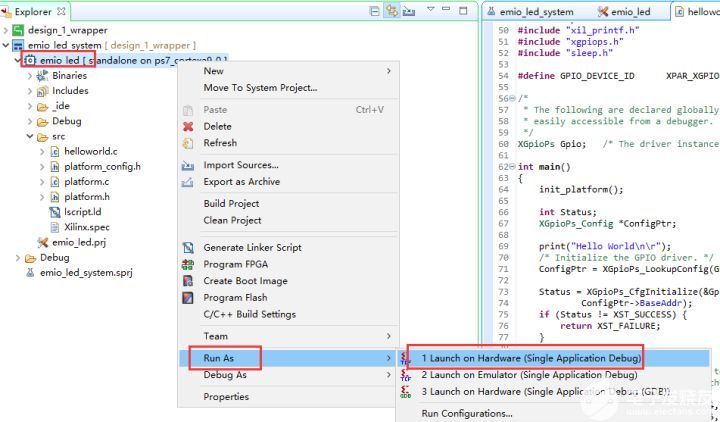

3)Run AsLaunch on Hardware(Single Application Debug),下載結束后,即可看到PS_LED快速閃爍16次

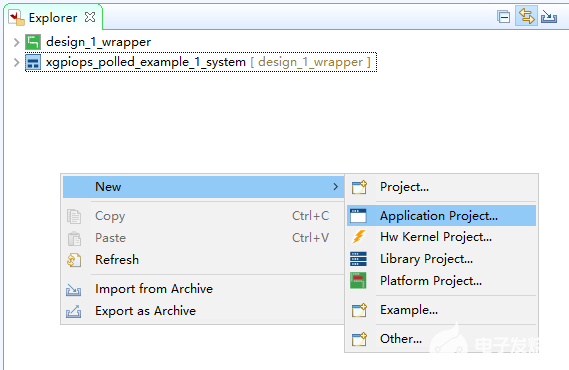

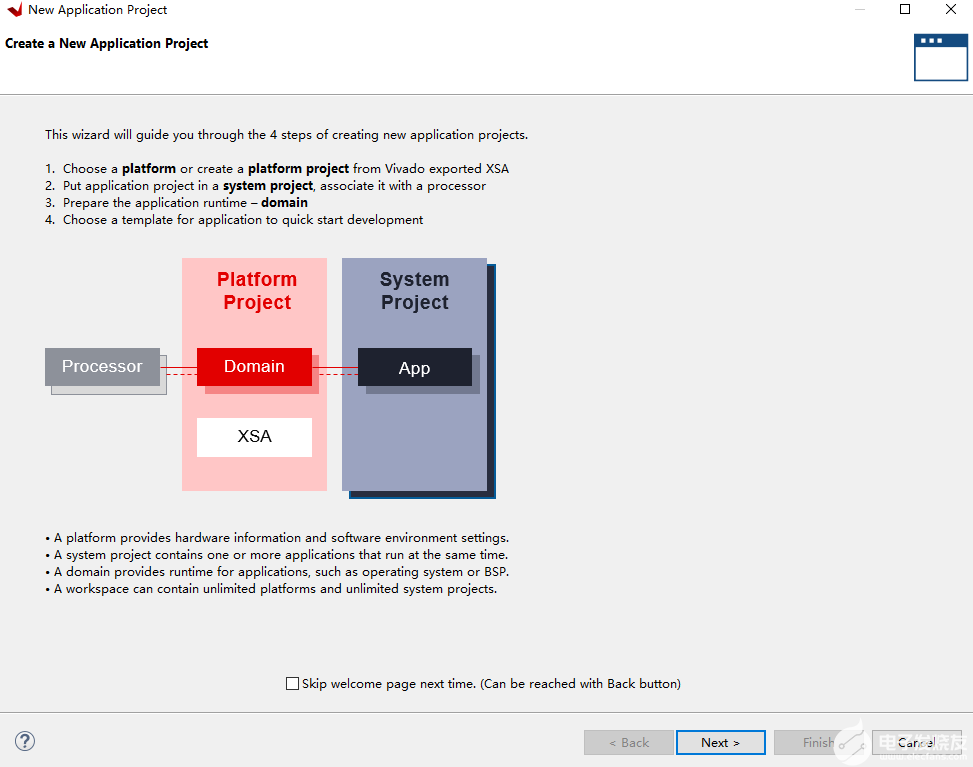

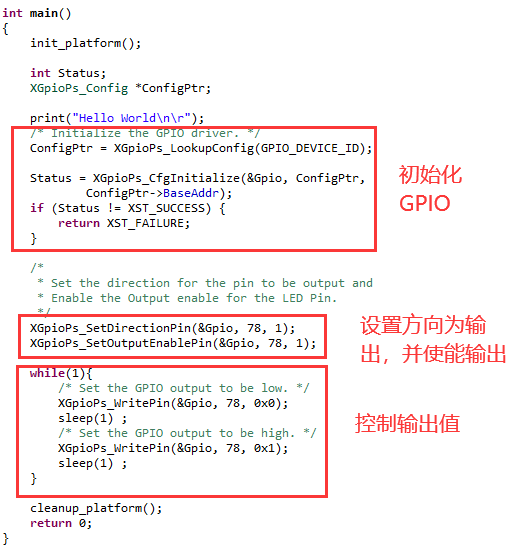

4)雖然用官方的例子比較方便,但是它的代碼看起來比較臃腫,我們可以通過學習它的方法,自己簡化寫一遍。我們新建一個APP工程。可以在空白處右鍵NewApplication Project。在ps_led_test的helloworld.c中修改。其實程序步驟很簡單,初始化GPIO設置方向輸出使能控制GPIO輸出值。

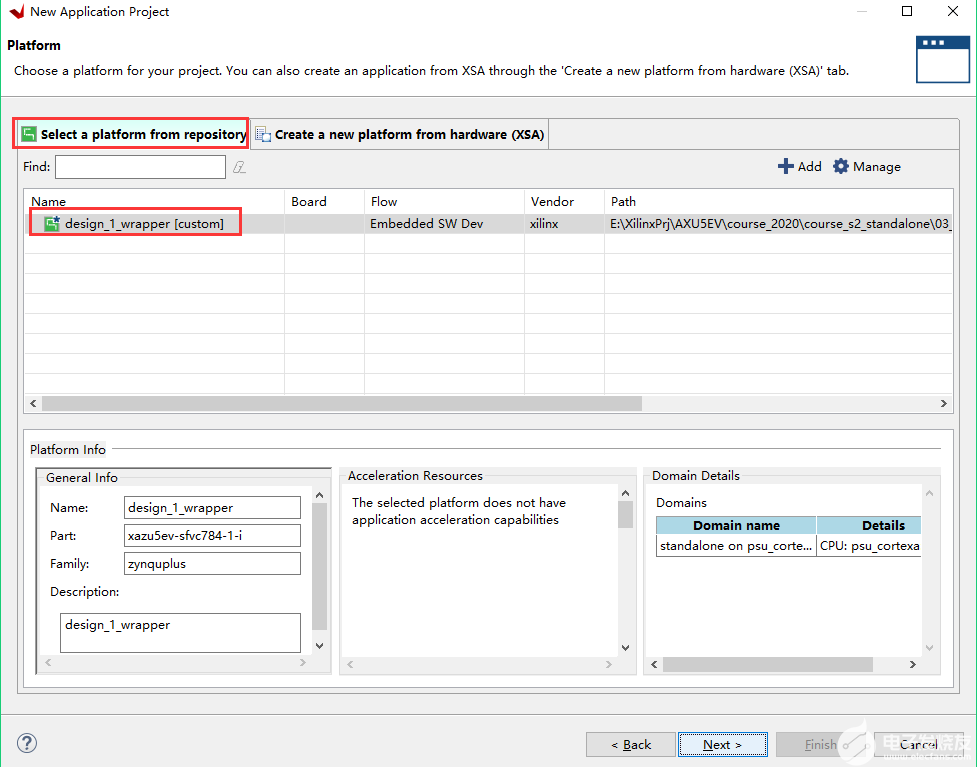

第一頁跳過

選擇硬件描述工程

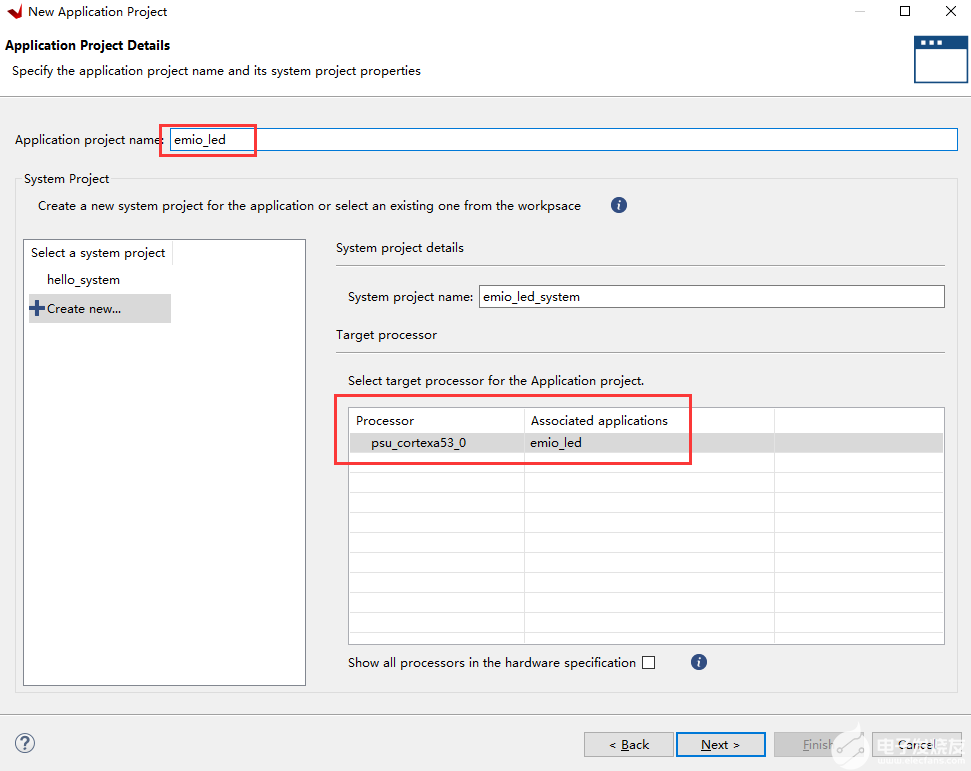

填入工程名稱,并選擇相應的CPU

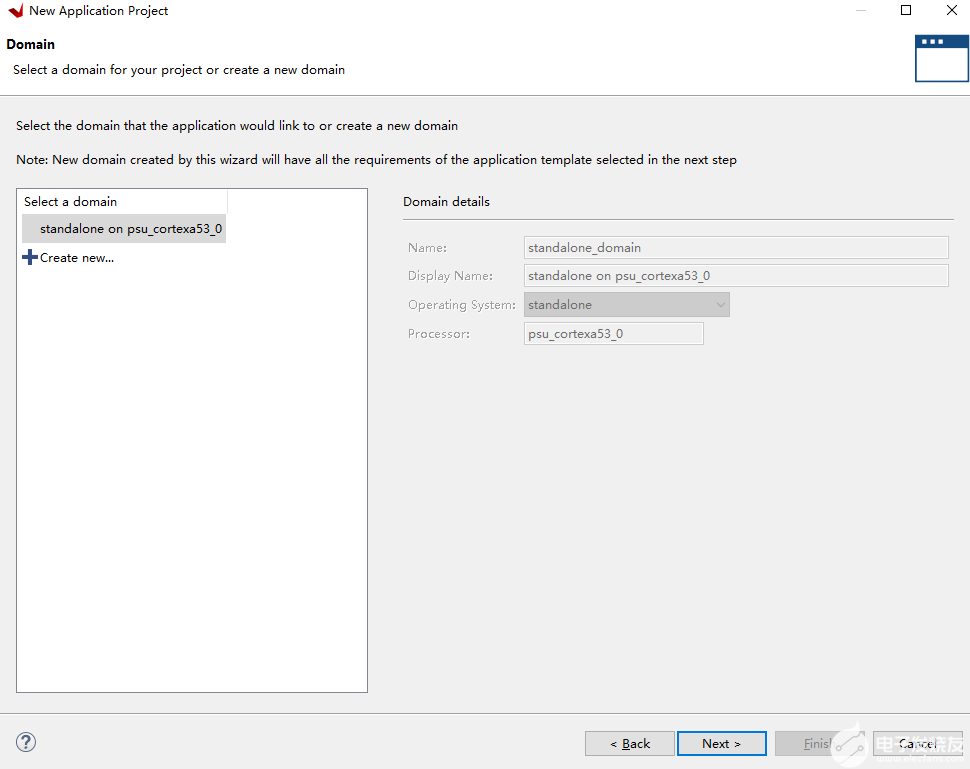

下一步

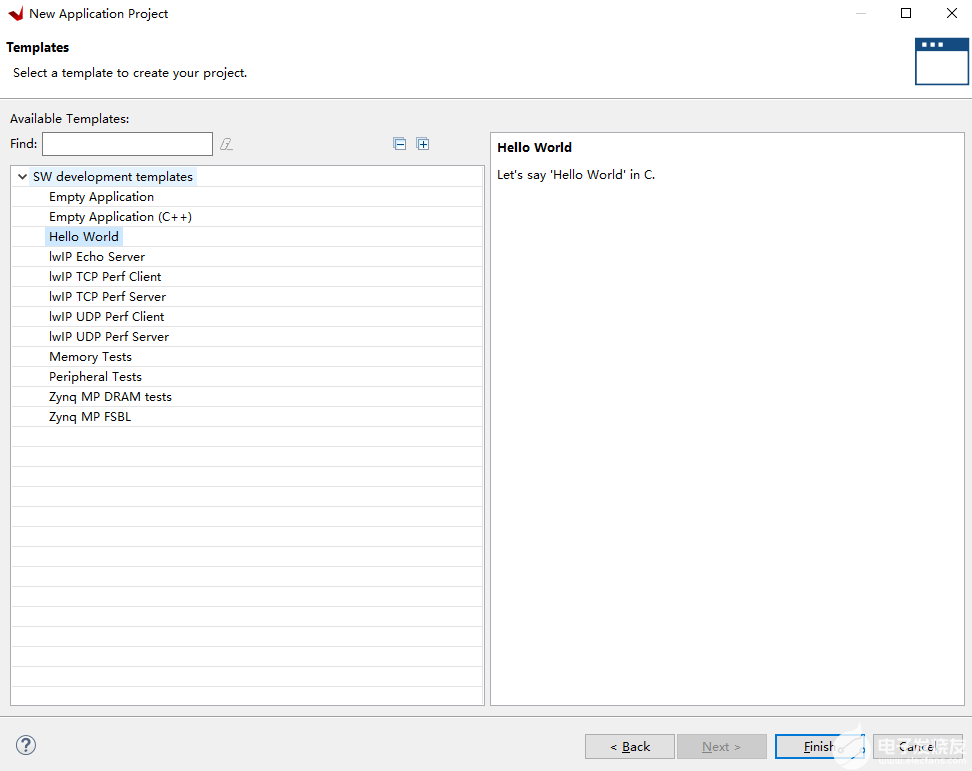

模板選擇Hellow World即可

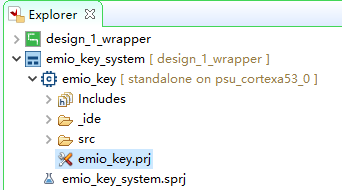

5)可以看到多了一個APP工程,仍然是基于名為standalone on psu_cortexa53_0的BSP,也就是一個Domain,與前面的example工程共用一個BSP

6)可以將例程的代碼復制到helloworld.c中,保存并Build Project

7)編譯并下載

即可看到LED1閃爍。

4.2 EMIO實現PL端按鍵中斷

前面介紹了EMIO作為輸出控制LED燈,這里講一下利用EMIO作為按鍵輸入控制LED燈。

1)通過ug1085文檔看下GPIO的結構圖,中斷的寄存器:

INT_MASK:中斷掩碼

INT_DIS: 中斷關閉

INT_EN: 中斷使能

INT_TYPE: 中斷類型,設置電平敏感還是邊沿敏感

INT_POLARITY: 中斷極性,設置低電平或下降沿還是高電平或上升沿

INT_ANY: 邊沿觸發方式,需要INT_TYPE設置為邊沿敏感才能使用

設置中斷產生方式時需要INT_TYPE、INT_POLARITY、INT_ANY配合使用。具體寄存器含義請參考ug1085部分。

2)本實驗設計為按下按鍵LED燈亮,再按下LED滅。

主程序設計流程如下:

GPIO初始化設置按鍵和LED方向設置產生中斷方式設置中斷打開中斷控制器打開中斷異常打開GPIO中斷判斷KEY_FLAG值,是1,寫LED

中斷處理流程:

查詢中斷狀態寄存器判斷狀態清除中斷設置KEY_FLAG值

3)新建名為emio_key的工程,模板為hello world,拷貝例程的程序

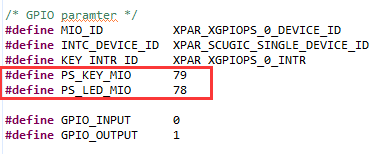

4)定義PS按鍵編號為79,PS LED為78

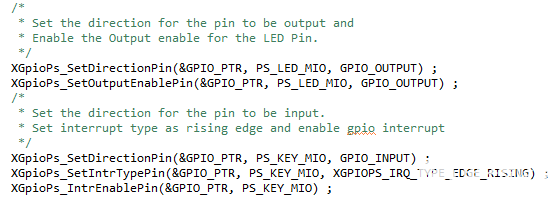

5)在main函數中,設置LED和按鍵,將按鍵中斷類型設置為上升沿產生中斷。在本實驗中,即按鍵信號的上升沿產生中斷。

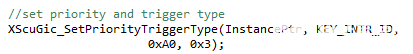

6)中斷控制器設置函數IntrInitFuntions是參考PS定時器中斷實驗所做,而下面的語句是設置中斷優先級和觸發方式。即操作ICDIPR和ICDICFR寄存器。

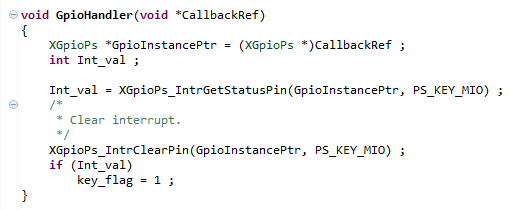

7)在中斷服務程序GpioHandler中,判斷中斷狀態寄存器,清除中斷,并將按鍵標志置1。

8)在main函數中,判斷按鍵標志key_flag,向LED寫入數據。

9)編譯工程并下載程序,觀察實驗現象,按下KEY1,就可以控制LED1燈亮滅。

5. 固化程序

前面介紹過沒有FPGA加載文件情況下如何生成固化程序(詳情參考“體驗ARM,裸機輸出”Hello World”一章)。本章內容生成了FPGA的加載文件,在這里演示一下如何生成固化程序。

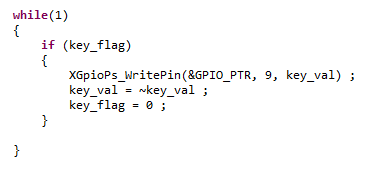

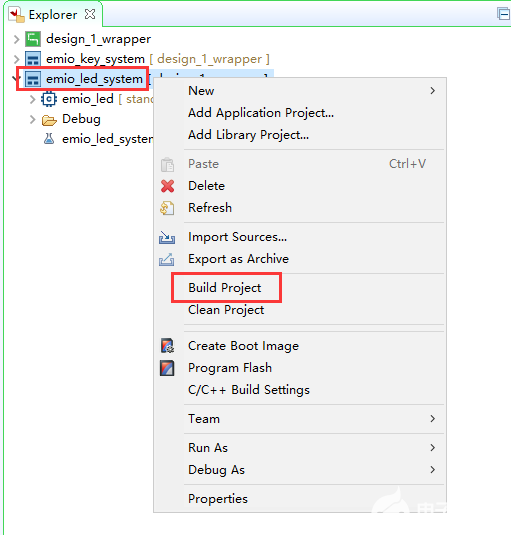

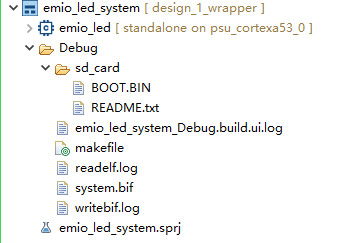

與前面一樣,也是點擊system,右鍵Build Project即可

軟件會自動添加三個文件,第一個引導程序fsbl.elf,第二個為FPGA的bitstream,第三個為應用程序xx.elf,下載方法與前面一樣,不再贅述。

6. 引腳綁定常見錯誤

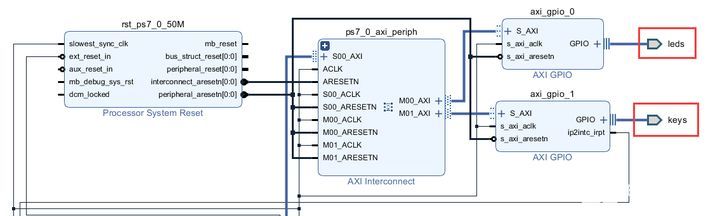

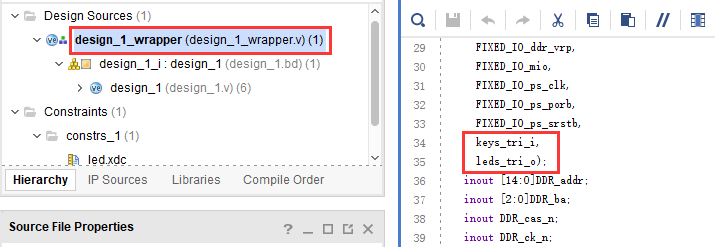

1)在block design設計中,比如下圖,GPIO模塊的引腳名設置為了leds和keys,很多人想當然的在XDC里按照這樣的名稱綁定引腳。

如果打開頂層文件就會發現引腳名稱是不一樣的,一定要仔細檢查,以頂層文件里的引腳名稱為準。

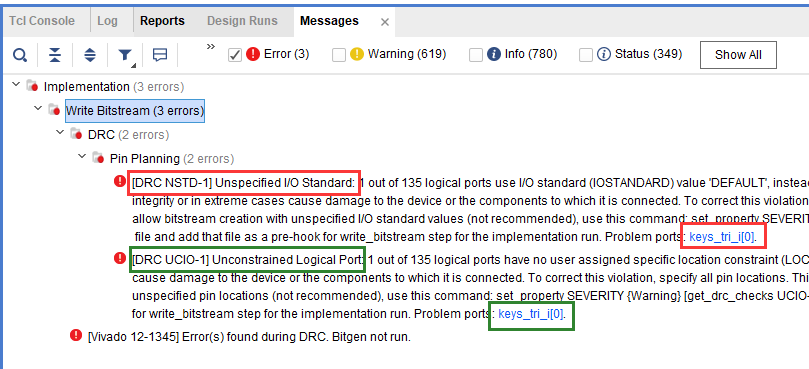

否則就會出現以下引腳未綁定的錯誤

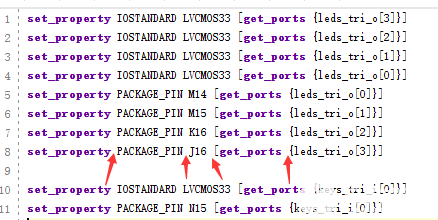

2)如果是手寫XDC文件,切記注意空格,這也是非常常見的錯誤

7. 本章小節

本章進一步學習了PS端的EMIO的使用,雖然將EMIO連接到了PL端的引腳上,但Vitis中的用法還是一樣的,從這個例子我們也可以看出,一旦與PL端發生了聯系,就需要生成bitstream,雖然幾乎沒有產生邏輯。

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601872 -

按鍵

+關注

關注

4文章

223瀏覽量

57572 -

GPIO

+關注

關注

16文章

1196瀏覽量

51919 -

Zynq

+關注

關注

9文章

608瀏覽量

47128 -

MPSoC

+關注

關注

0文章

198瀏覽量

24252

發布評論請先 登錄

相關推薦

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

閑話Zynq UltraScale+ MPSoC(連載1)

閑話Zynq UltraScale+ MPSoC(連載5)

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+ MPSoC驗證數據手冊

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十八章PS端EMIO的使用

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十八章PS端EMIO的使用

評論