本文轉(zhuǎn)載自:VagueCheung的博客

賽靈思公司(Xilinx)推出Vitis——這是一款統(tǒng)一軟件平臺(tái),可以讓包括軟件工程師和AI科學(xué)家在內(nèi)的廣大開發(fā)者都能受益于硬件靈活應(yīng)變的優(yōu)勢(shì)。歷經(jīng)5年、投入總計(jì)1000人打造而成,Vitis統(tǒng)一軟件平臺(tái)無(wú)需用戶深入掌握硬件專業(yè)知識(shí),即可根據(jù)軟件或算法代碼自動(dòng)適配和使用賽靈思硬件架構(gòu)。此外,Vitis 平臺(tái)不限制使用專有開發(fā)環(huán)境,而是可以插入到通用的軟件開發(fā)工具中,并利用豐富的優(yōu)化過(guò)的開源庫(kù),使開發(fā)者能夠?qū)W⒂谒惴ǖ拈_發(fā)。Vitis獨(dú)立于Vivado設(shè)計(jì)套件,后者仍然繼續(xù)為希望使用硬件代碼進(jìn)行編程的用戶提供支持。但是,Vitis也能夠通過(guò)將硬件模塊封裝成軟件可調(diào)用的函數(shù), 從而提高硬件開發(fā)者的工作效率。

Vitis統(tǒng)一軟件平臺(tái)的四層架構(gòu)

Vitis構(gòu)建在基于堆棧的架構(gòu)之上,共有四層。

第一層是基礎(chǔ)層,是Vitis目標(biāo)平臺(tái)。該平臺(tái)由電路板和預(yù)編程I/O構(gòu)成;

第二層是Vitis 核心開發(fā)套件,覆蓋開源賽靈思運(yùn)行時(shí)庫(kù),以管理不同域間的數(shù)據(jù)移動(dòng), 包括子系統(tǒng)、即將發(fā)布的Versal ACAP內(nèi)的AI 引擎和必要的外部主機(jī)。此外,該層也提供編譯器、分析器和調(diào)試器等核心開發(fā)工具。這些工具均能與業(yè)界標(biāo)準(zhǔn)的構(gòu)建系統(tǒng)與開發(fā)環(huán)境無(wú)縫集成;

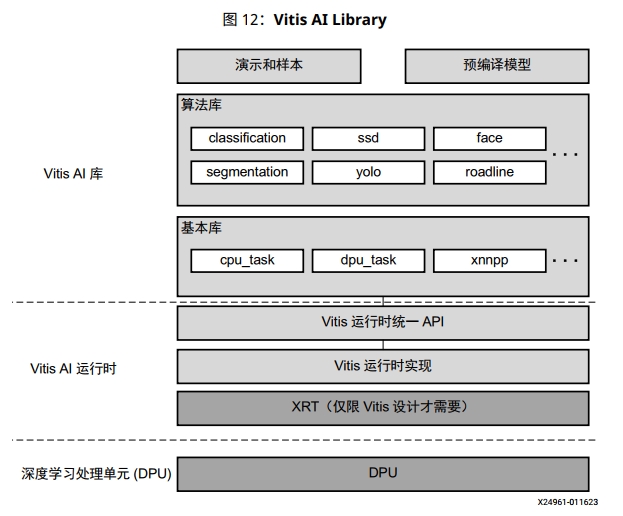

在第三層,8個(gè)Vitis 庫(kù)提供400余種優(yōu)化的開源應(yīng)用。這8個(gè)庫(kù)分別是:Vitis 基本線性代數(shù)子程序(B LAS)庫(kù)、Vitis 求解器庫(kù)、Vitis安全庫(kù)、Vitis視覺庫(kù)、Vitis數(shù)據(jù)壓縮庫(kù)、Vitis計(jì)量金融庫(kù)、Vitis數(shù)據(jù)庫(kù)集和Vitis AI 庫(kù)。借助這些庫(kù),軟件開發(fā)者可以使用標(biāo)準(zhǔn)的應(yīng)用編程接口(API)來(lái)實(shí)現(xiàn)硬件加速;

Vitis AI是Vitis 平臺(tái)的第四層,也是最具有變革意義的一層。它集成了特定領(lǐng)域架構(gòu)(DSA)。 DSA 提供了針對(duì)AI模型的硬件實(shí)現(xiàn),開發(fā)者可以使用包括TensorFlow和Caffe等業(yè)界領(lǐng)先框架對(duì)其進(jìn)行配置與編程。Vitis AI提供的工具鏈能在數(shù)分鐘內(nèi)完成優(yōu)化、量化和編譯操作,在賽靈思器件上高效地運(yùn)行預(yù)先訓(xùn)練好的AI模型。此外,它也為從邊緣到云端的部署提供了專用API,實(shí)現(xiàn)業(yè)界一流的推斷性能與效率。賽靈思陸續(xù)還將推出另一個(gè)DSA(Vitis Video),支持從FFmpeg直接進(jìn)行編碼并提供同樣超級(jí)簡(jiǎn)單且功能極強(qiáng)大的端到端視頻解決方案。目前,由合作伙伴公司提供的DSA包括:與GATK 集成用于基因分析的Illumina,與ElasticSearch 集成用于大數(shù)據(jù)分析的BlackLynx, 以及當(dāng)前我們客戶正在使用的專有DSA。

Vitis擁有三大特點(diǎn):第一是開放,第二是標(biāo)準(zhǔn),第三是免費(fèi)。首先,Vitis統(tǒng)一軟件平臺(tái)支持在賽靈思異構(gòu)平臺(tái)上開發(fā)嵌入式軟件和加速應(yīng)用,包括FPGA、SoC和Versal ACAP,為邊緣、云和混合計(jì)算應(yīng)用 加速提供了統(tǒng)一編程模型。其次,Vitis可與高層次框架進(jìn)行集成,可以通過(guò)加速庫(kù)采用C、C++或Python進(jìn)行開發(fā),也可以使用基于RTL的加速器和低層次運(yùn)行是API對(duì)實(shí)現(xiàn)方案進(jìn)行粒度更精確的控制。

硬件加速應(yīng)用程序開發(fā)流程:

對(duì)于基于FPGA的加速,Vitis核心開發(fā)套件支持用戶通過(guò)API函數(shù)創(chuàng)建軟件應(yīng)用程序,例如OpenCL函數(shù),在Alveo加速卡上運(yùn)行加速硬核。Vitis核心開發(fā)套件也支持將軟件程序運(yùn)行在基于Linux的嵌入式處理器平臺(tái)上,例如ZYNQ的UltraScale+MPSOC設(shè)備。對(duì)于嵌入式處理器平臺(tái)Vitis開發(fā)套件執(zhí)行模型也通過(guò)OpenCL API和基于Linux的Xilinx運(yùn)行庫(kù)(XRT)來(lái)調(diào)度硬核和控制數(shù)據(jù)的搬移。(加速庫(kù)和xilinx運(yùn)行庫(kù)在GitHub上可下載)

Vitis核心開發(fā)套件可支持Alveo U50、U200、U250、U280加速卡,也支持zcu102、zcu104、zc702、zc706嵌入式處理器平臺(tái)。除了以上比較流行的平臺(tái)外,同時(shí)也支持自定義平臺(tái)。

Vitis軟件平臺(tái)允許用戶將數(shù)據(jù)中心應(yīng)用程序移植到嵌入式平臺(tái)上。Vitis核心開發(fā)套件不僅具有適用于硬核的V++編譯器。也具有運(yùn)行在X86主機(jī)的g++編譯器和運(yùn)行在Xilinx設(shè)備的嵌入式處理器的Arm編譯器

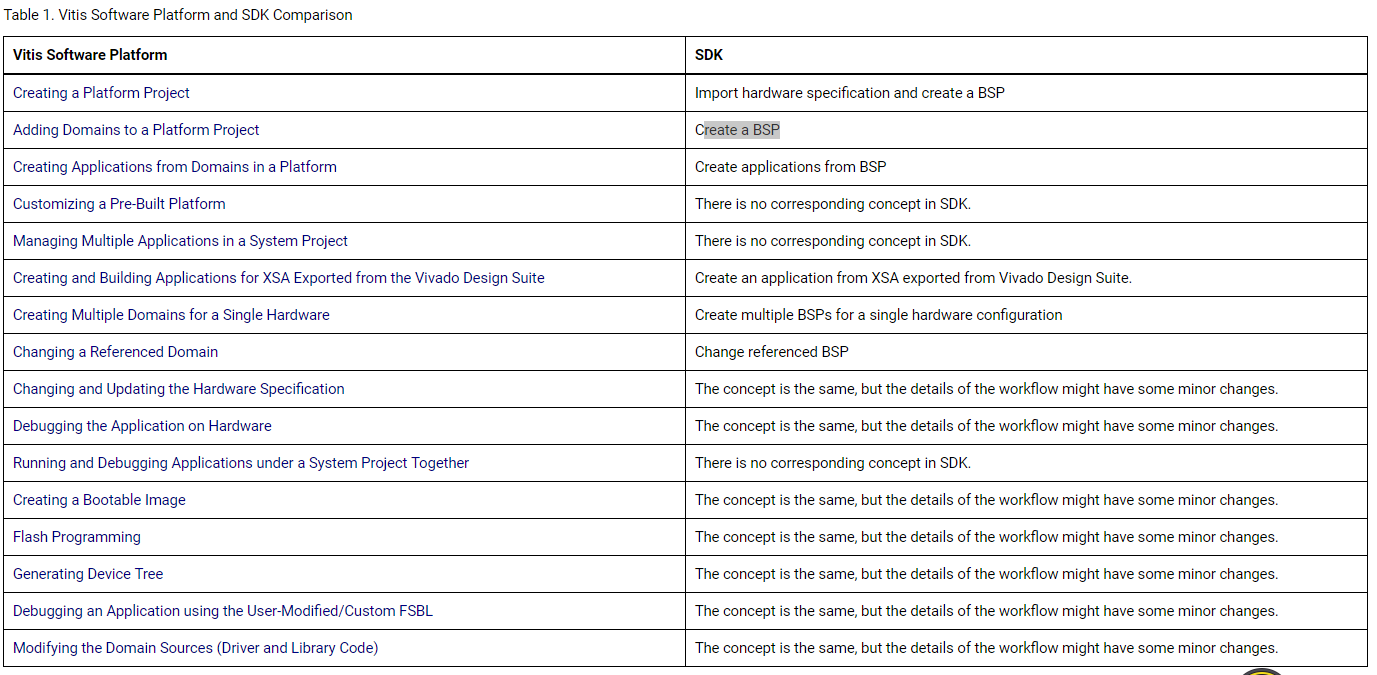

Vitis與SDK對(duì)比:

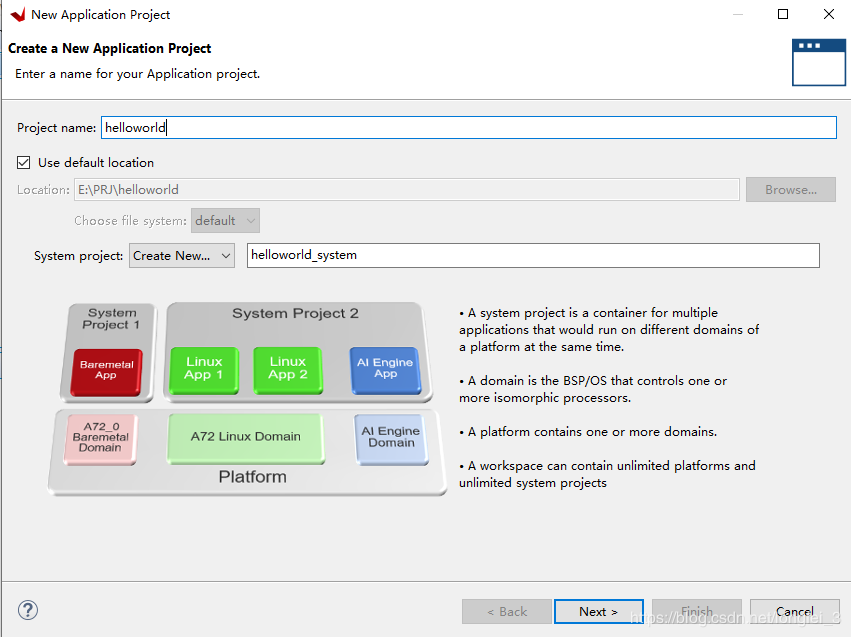

系統(tǒng)項(xiàng)目指的是什么?域domain可以理解成SDK中的BSP么?

系統(tǒng)項(xiàng)目就是指在Vitis中創(chuàng)建的application。

| Vitis軟件平臺(tái) | SDK |

| 可在Vitis中直接創(chuàng)建一個(gè)平臺(tái)項(xiàng)目(需要添加vivado生成的XSA文件或者從平臺(tái)庫(kù)中添加任意平臺(tái)作為基礎(chǔ)例如vck190.xsa、zc702.xsa、zc706.xsa、zcu102.xsa、zed.xsa) | SDK是從vivado工程中導(dǎo)出硬件平臺(tái)項(xiàng)目 |

| 為平臺(tái)添加域 | 創(chuàng)建BSP |

| 創(chuàng)建應(yīng)用程序(通過(guò)平臺(tái)的域) | 創(chuàng)建應(yīng)用程序(通過(guò)BSP) |

| 改制一個(gè)預(yù)置平臺(tái) | 無(wú)提及 |

| 可在一個(gè)系統(tǒng)項(xiàng)目中管理多個(gè)應(yīng)用程序 | 無(wú)提及 |

| 修改并且更新硬件 | 基本相同,工作流程可能有細(xì)微改變 |

| 在硬件上調(diào)試應(yīng)用程序 | 基本相同,工作流程可能有細(xì)微改變 |

| 在一個(gè)系統(tǒng)項(xiàng)目下運(yùn)行和調(diào)試應(yīng)用程序 | 無(wú)提及 |

| 創(chuàng)建boot image | 基本相同,工作流程可能有細(xì)微改變 |

| Flash 編程 | 基本相同,工作流程可能有細(xì)微改變 |

| 生成設(shè)備樹 | 基本相同,工作流程可能有細(xì)微改變 |

| 通過(guò)User-Modify/Custom FSBL測(cè)試應(yīng)用程序 | 基本相同,工作流程可能有細(xì)微改變 |

| 修改域源文件 | 基本相同,工作流程可能有細(xì)微改變 |

實(shí)測(cè)Vitis編譯時(shí)間要比SDK編譯時(shí)間略長(zhǎng);

Vitis實(shí)現(xiàn)簡(jiǎn)單的HelloWord

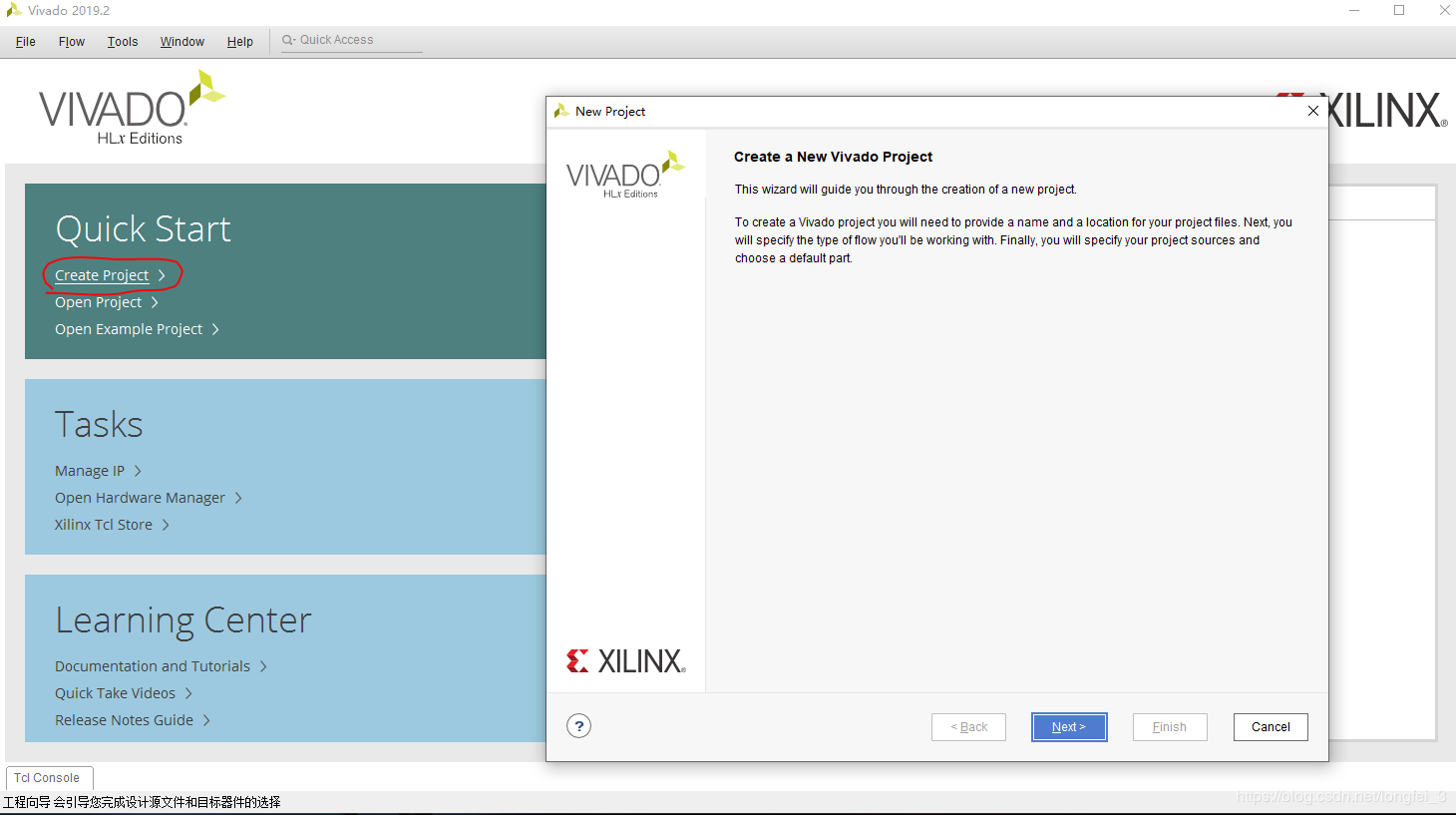

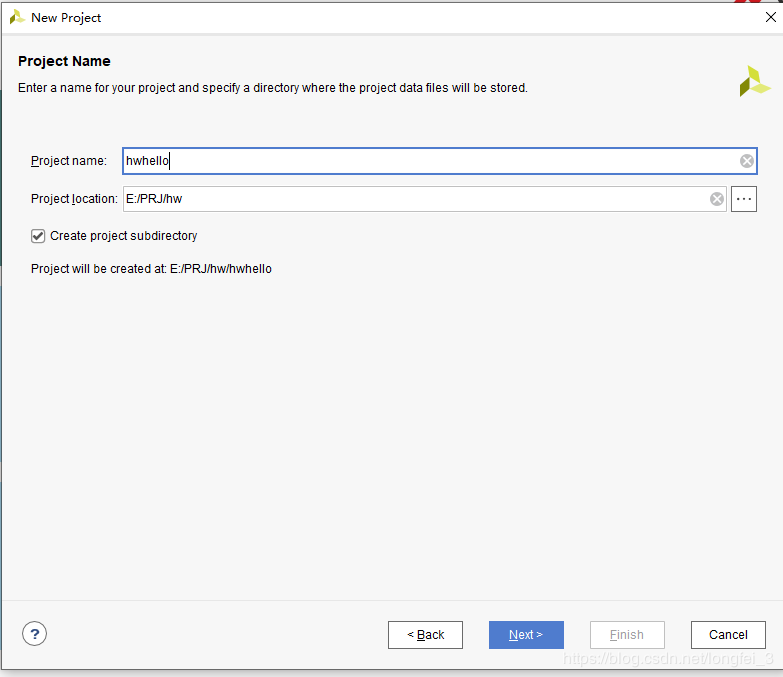

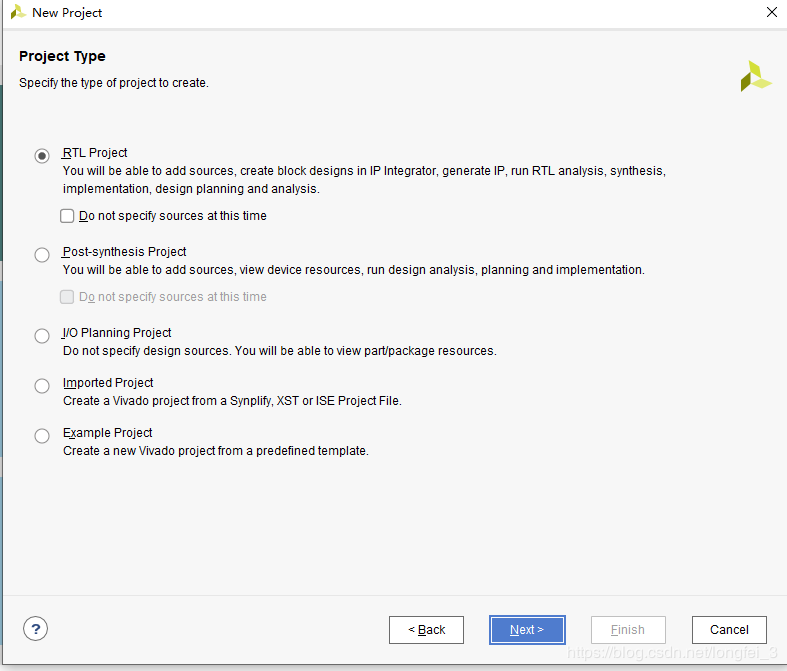

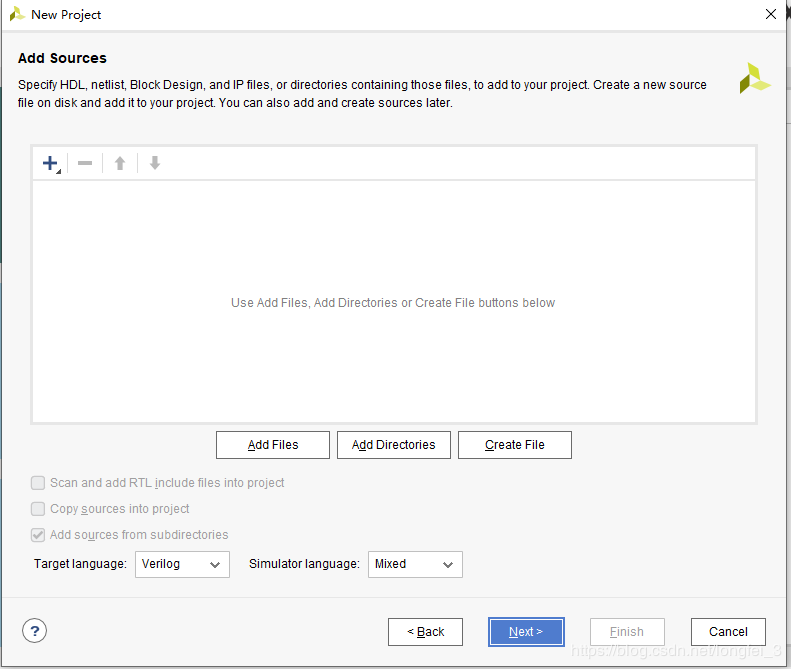

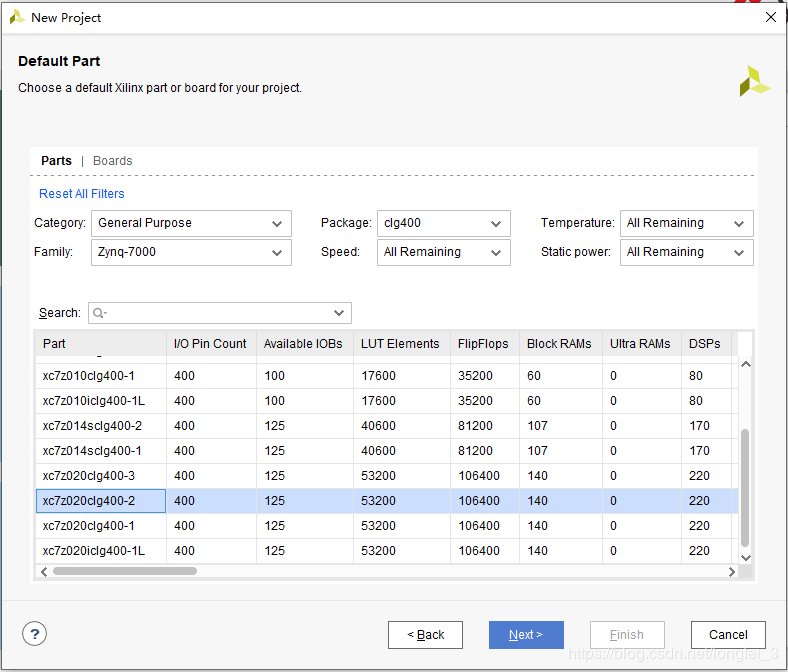

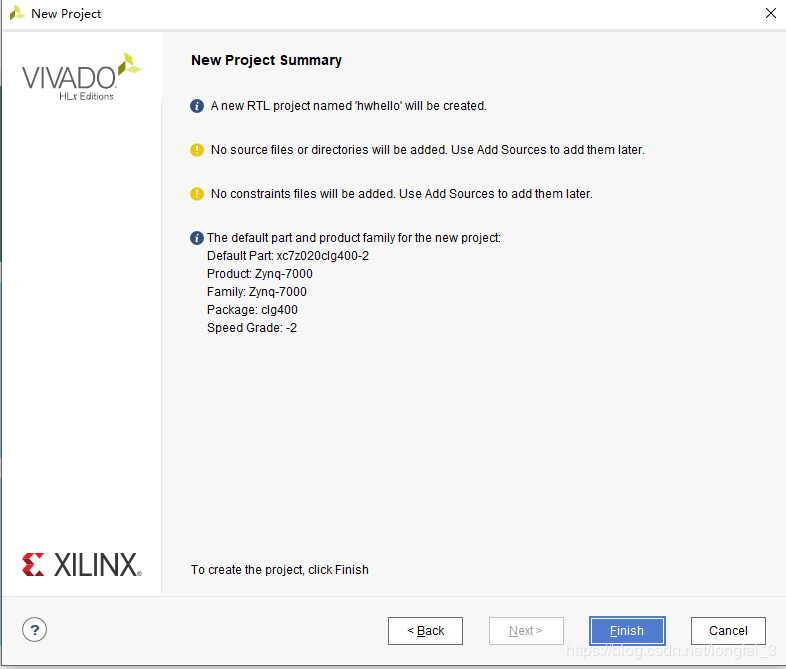

基于黑金ZYNQ 7020開發(fā)板創(chuàng)建工程,打開vivado2019.2一步步創(chuàng)建工程,vivado部分還是與之前一模一樣沒有任何改變。

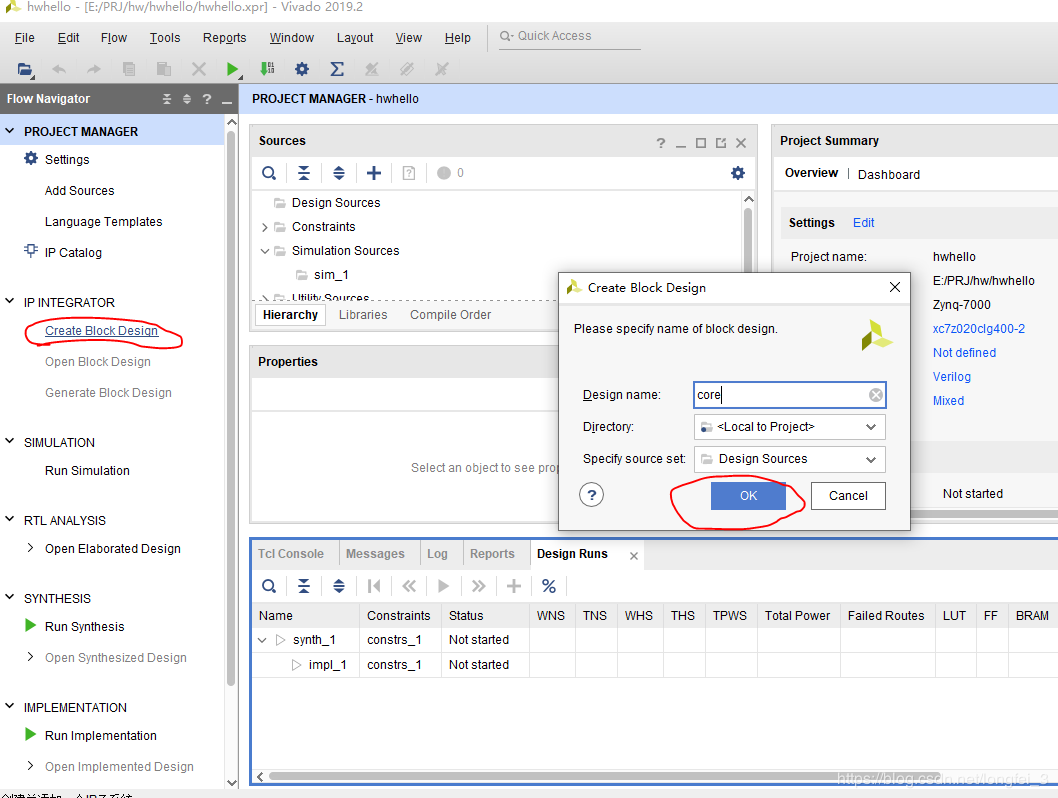

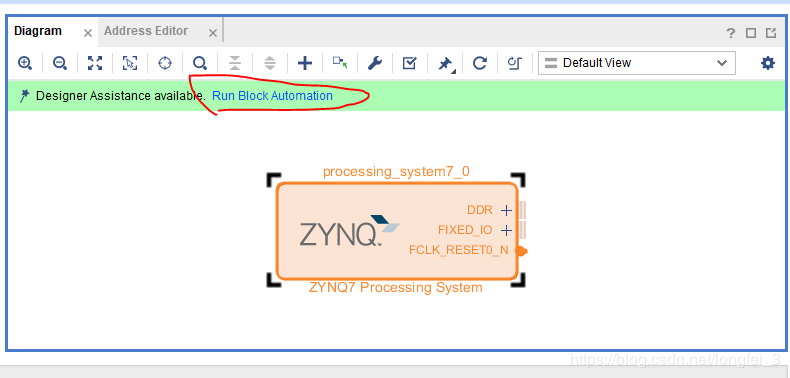

創(chuàng)建完工程,創(chuàng)建同一個(gè) Block Design工程

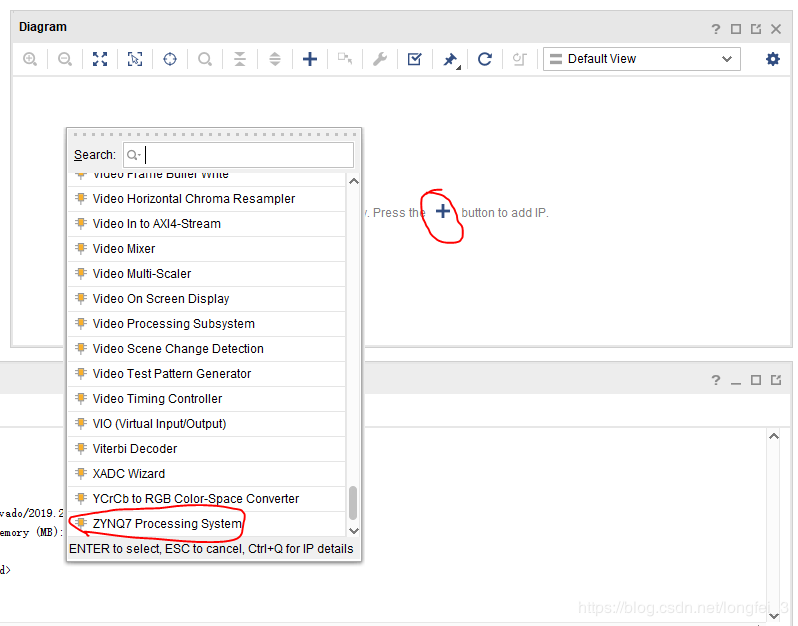

添加ZYNQ 核

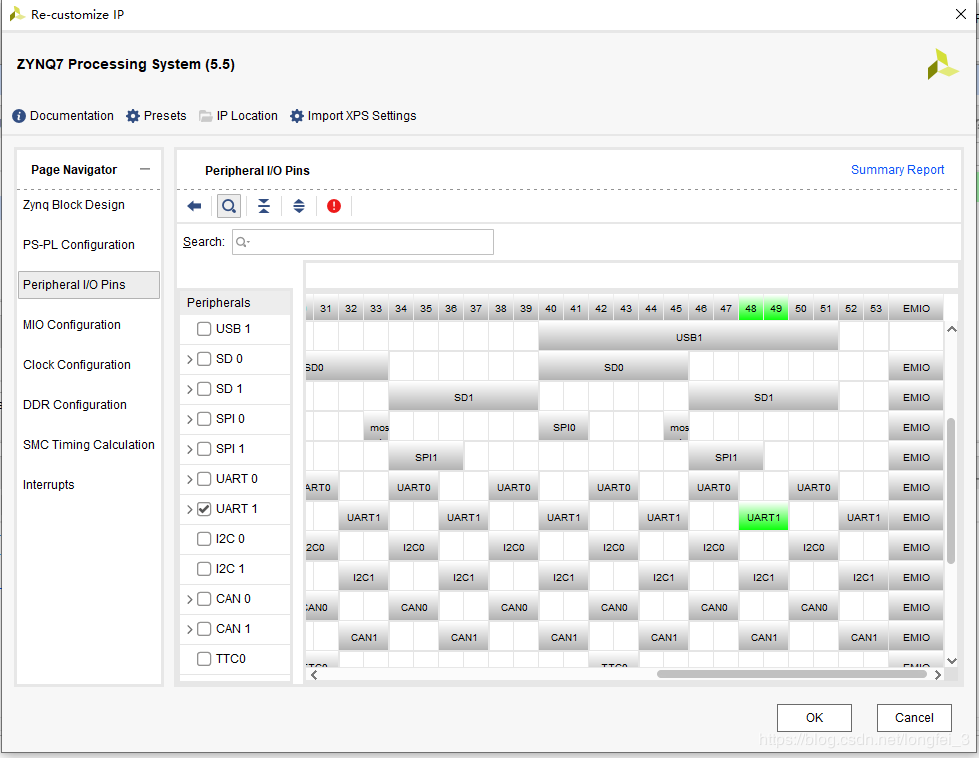

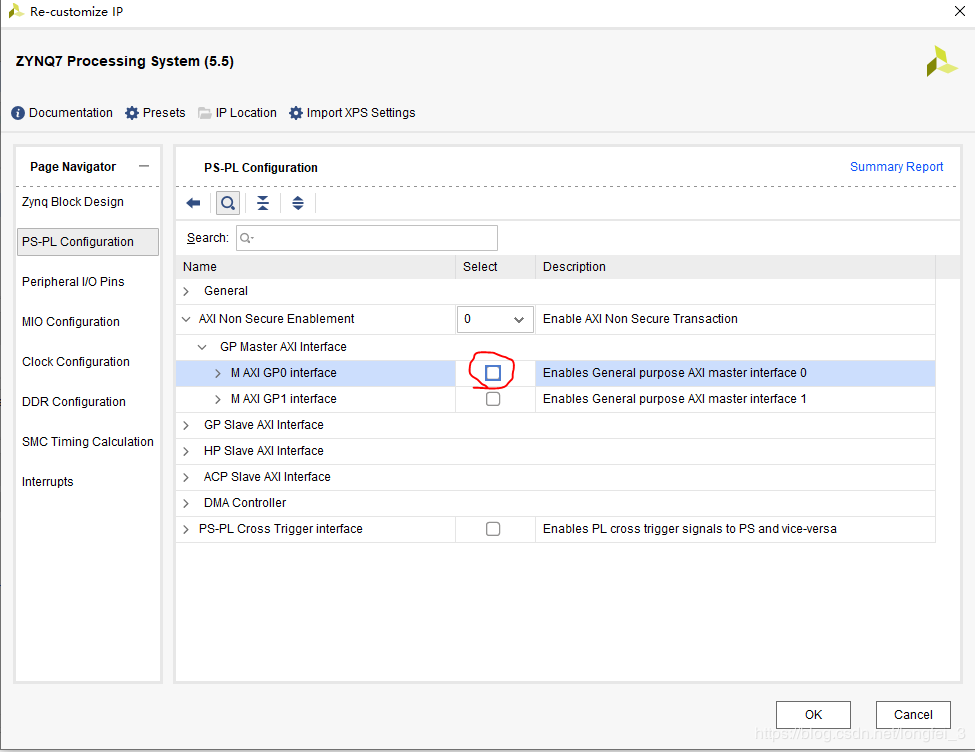

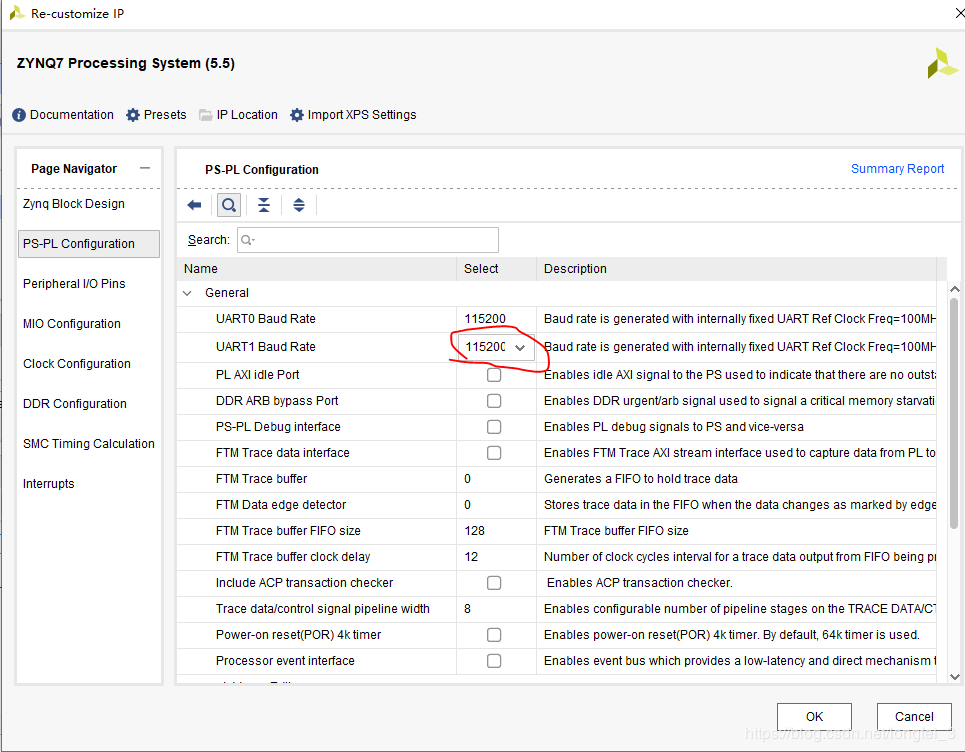

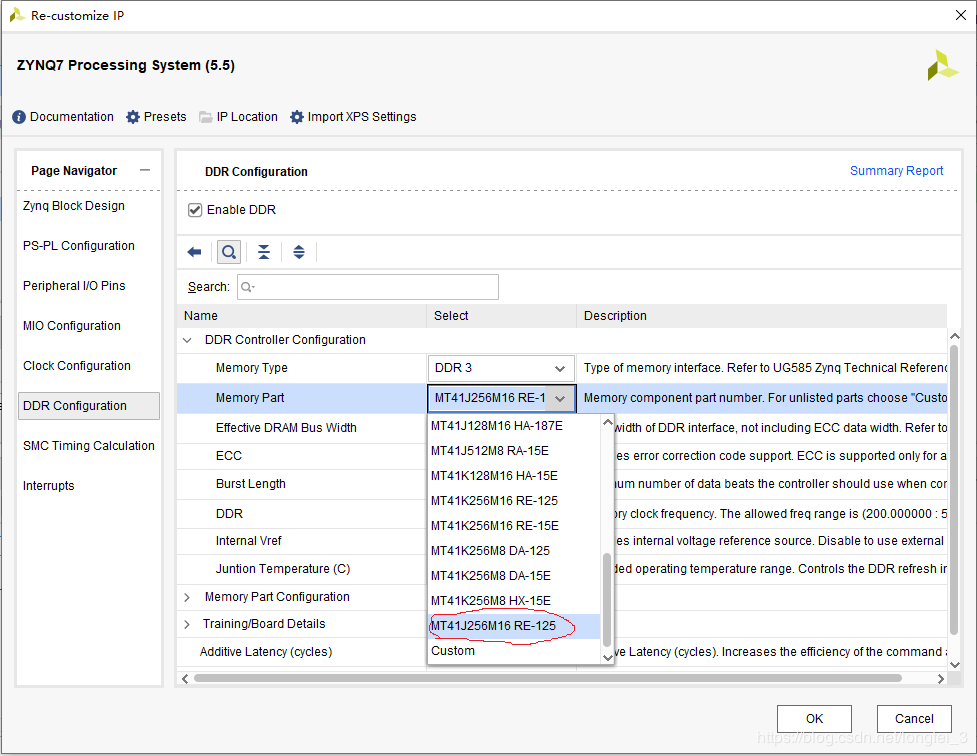

雙擊ZYNQ核設(shè)置一下,這里設(shè)置跟板子一致UART1,波特率選擇115200,沒有用到PL,AXI也沒使用。

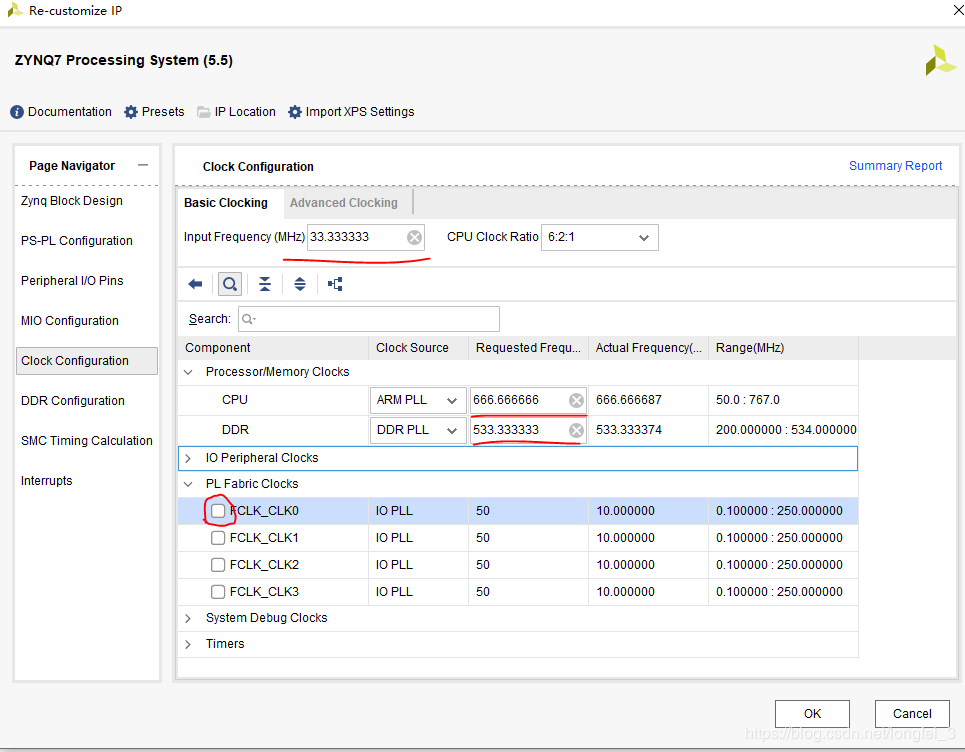

時(shí)鐘默認(rèn)即可,黑金的7020最高可以跑到767Mhz。

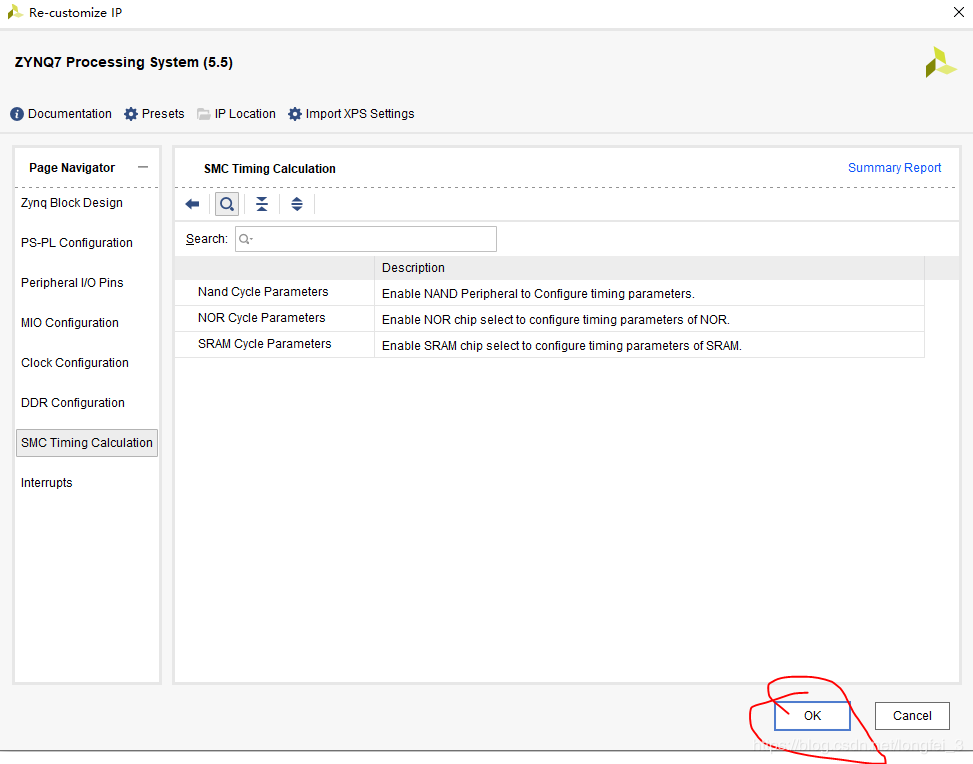

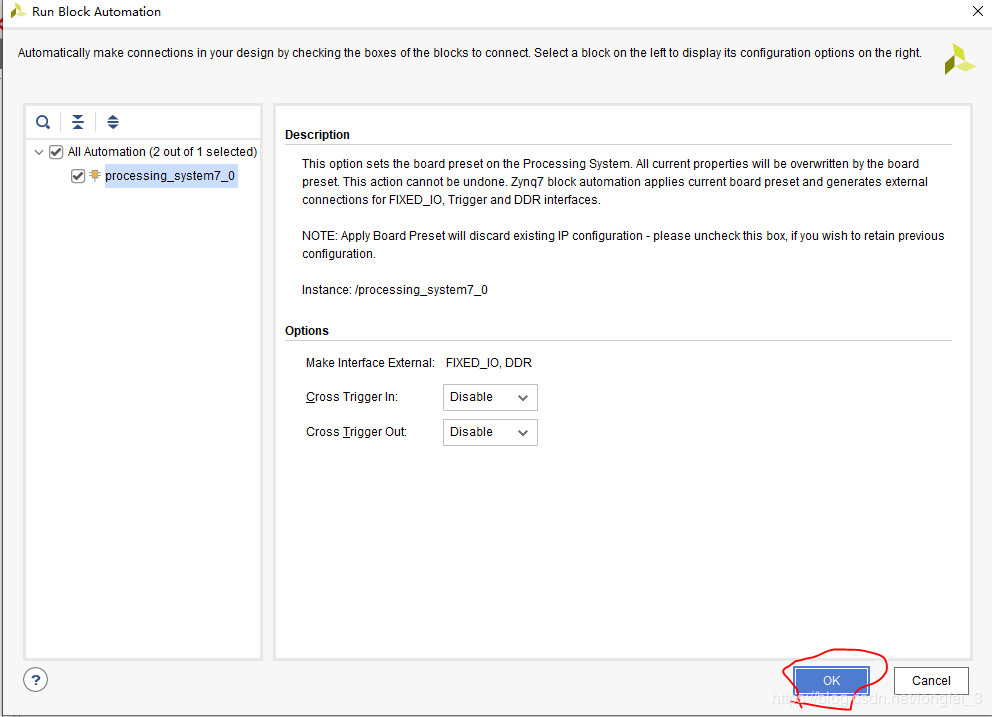

設(shè)置完成。自動(dòng)連線。

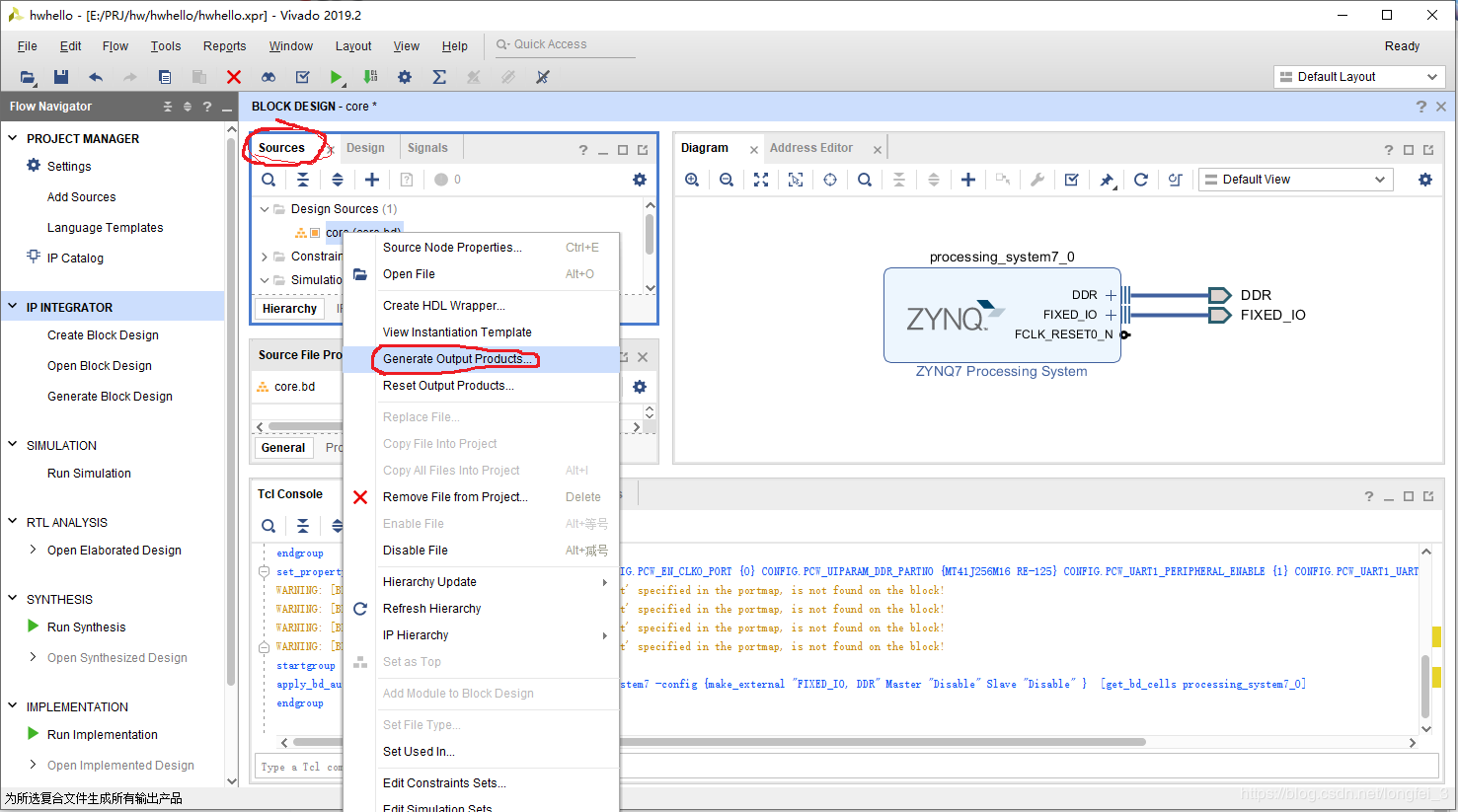

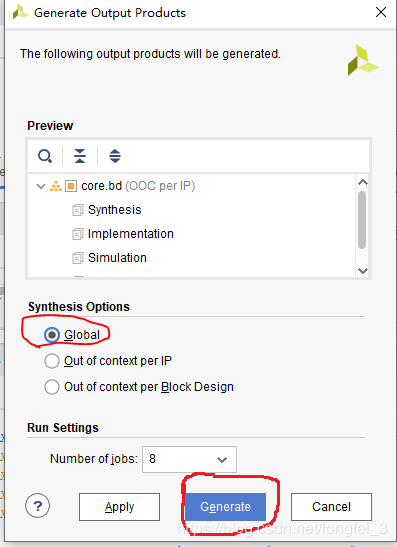

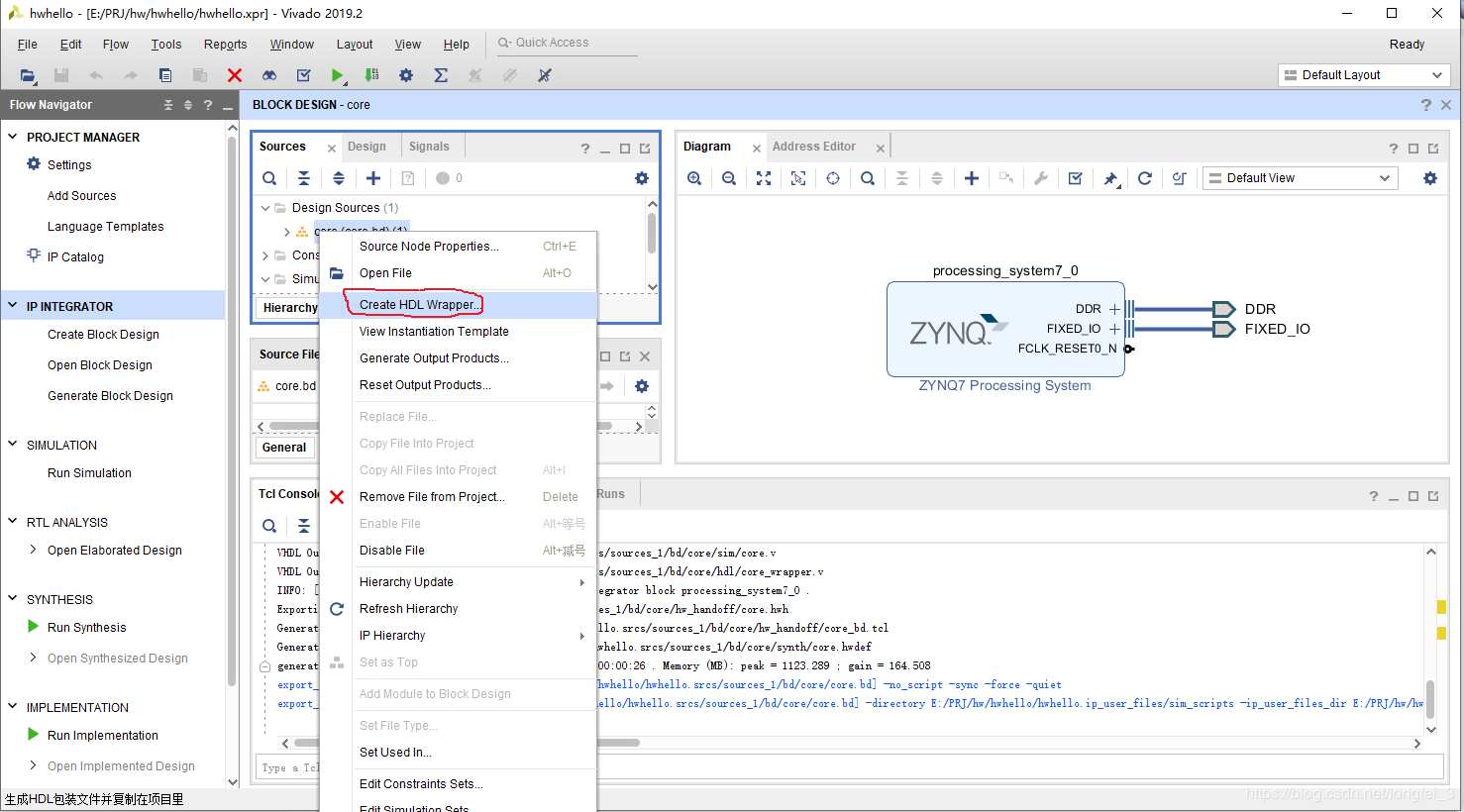

生成文件:

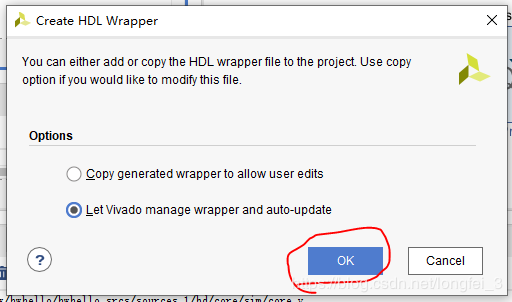

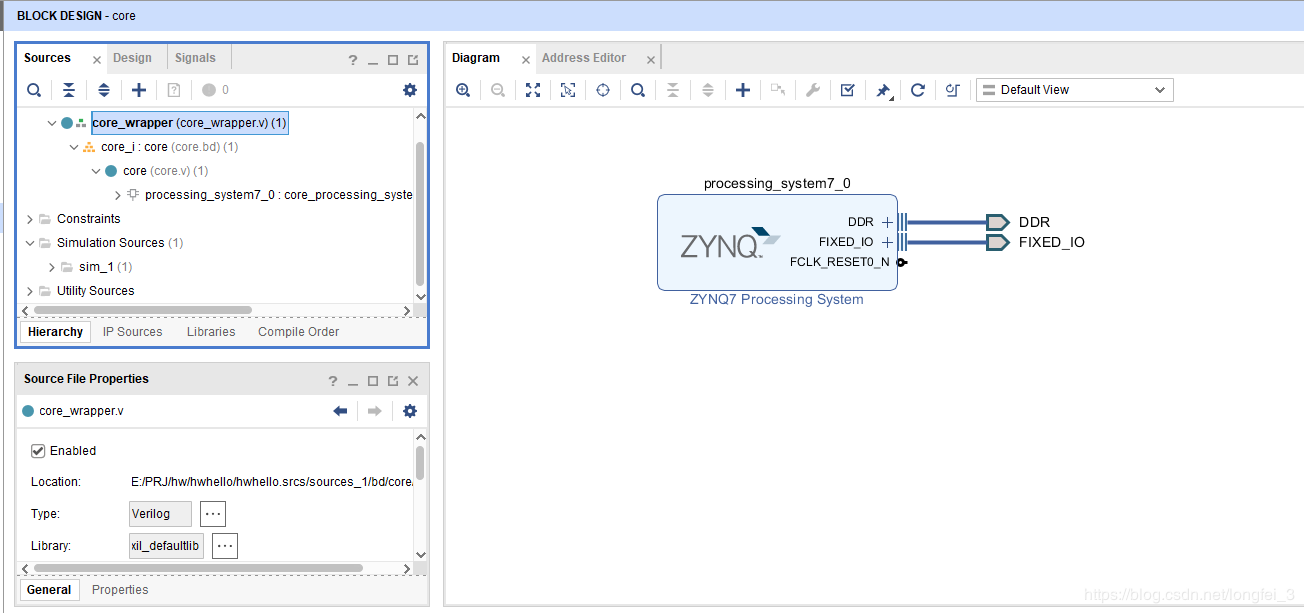

生成頂層文件:

至此PL部分完成了。

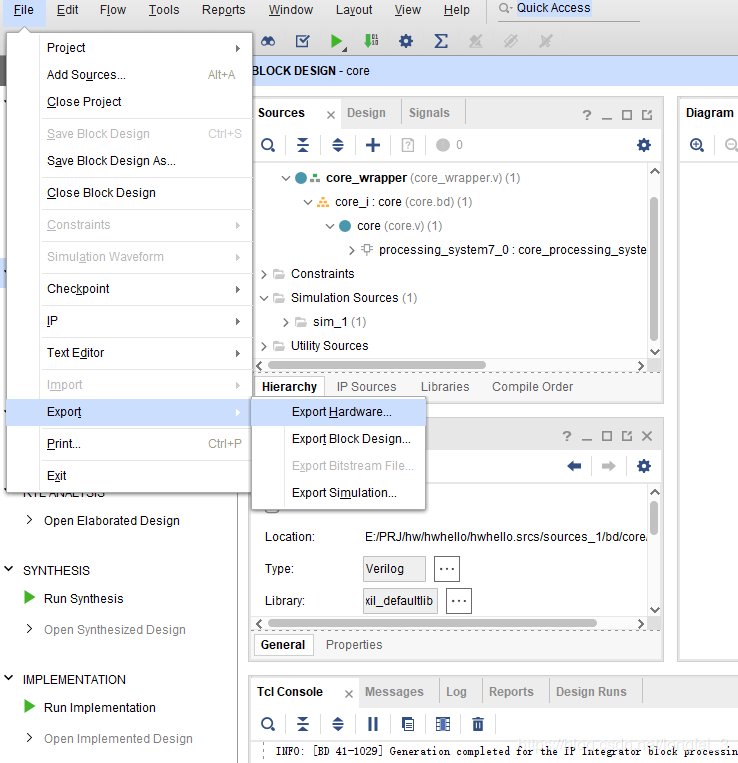

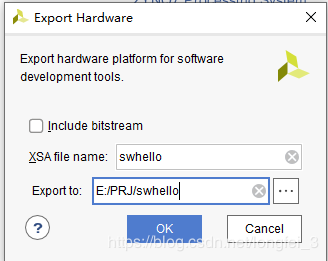

導(dǎo)出設(shè)計(jì)到軟件,沒有用到PL,所以不用綜合生成bit文件了,這里直接導(dǎo)出

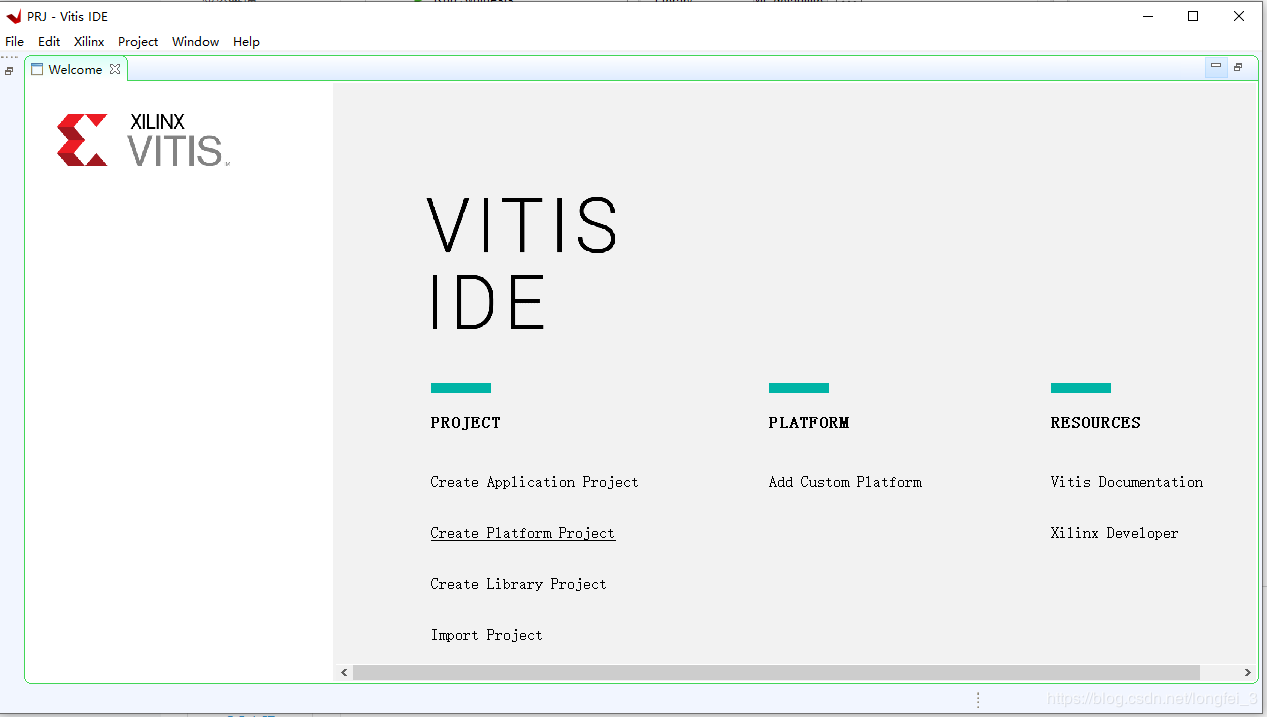

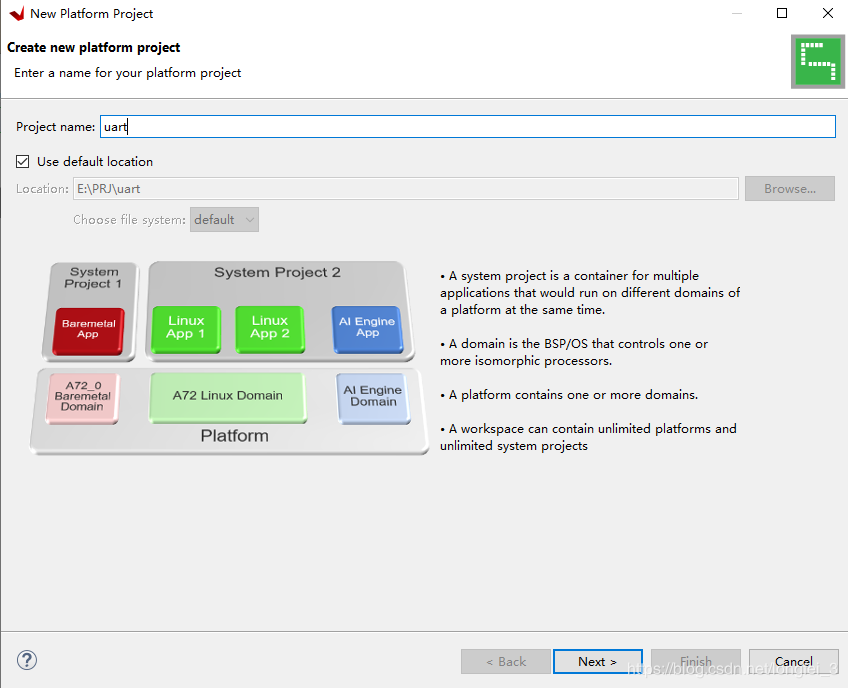

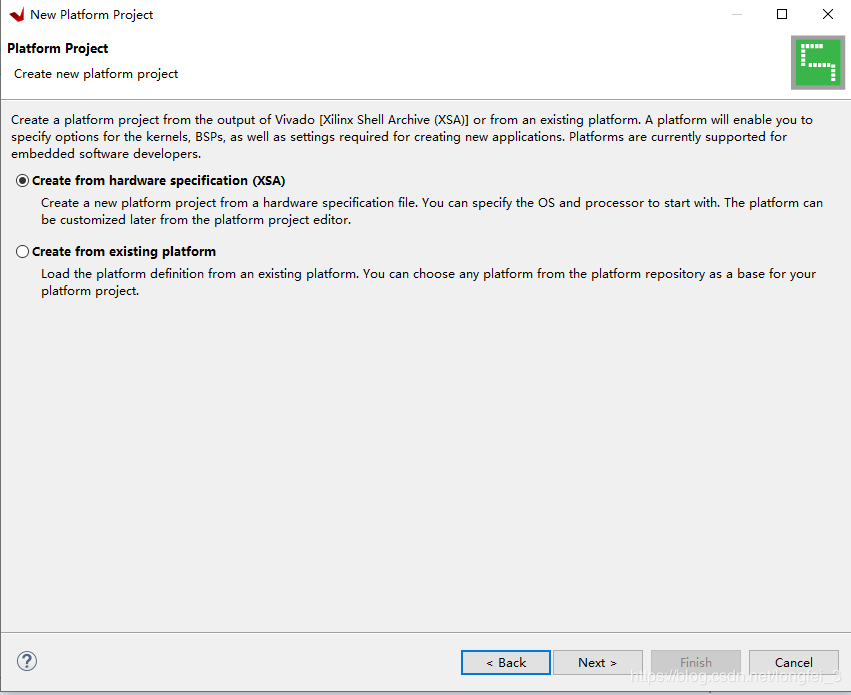

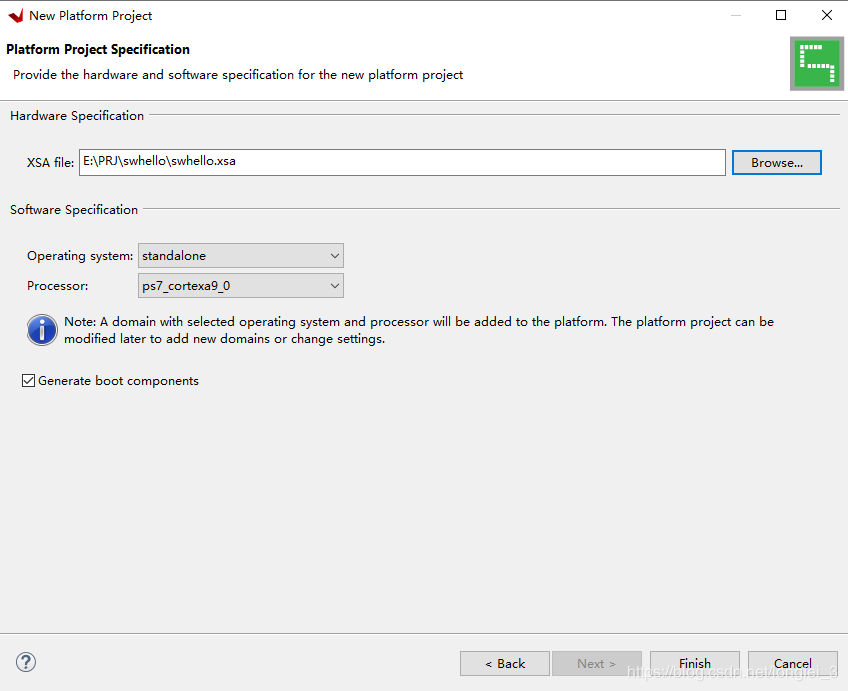

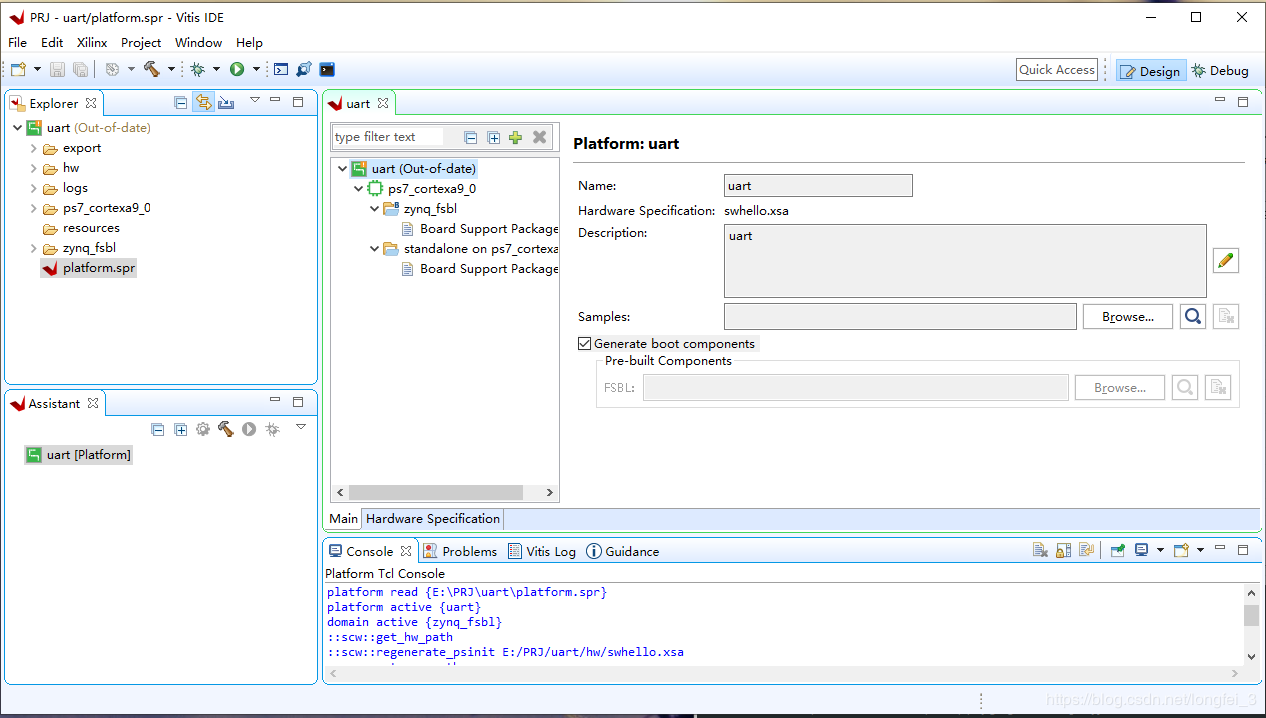

導(dǎo)出完成,這里開始軟件操作,打開vitis先創(chuàng)建一個(gè) platform project導(dǎo)入剛才的設(shè)計(jì)xsa文件。

這里與SDK不同,SDK是從vivado直接Launch打開,而Vitis是獨(dú)立與vivado IDE的開發(fā)工具。

選擇Vivado導(dǎo)出的設(shè)計(jì),點(diǎn)擊 finish完成

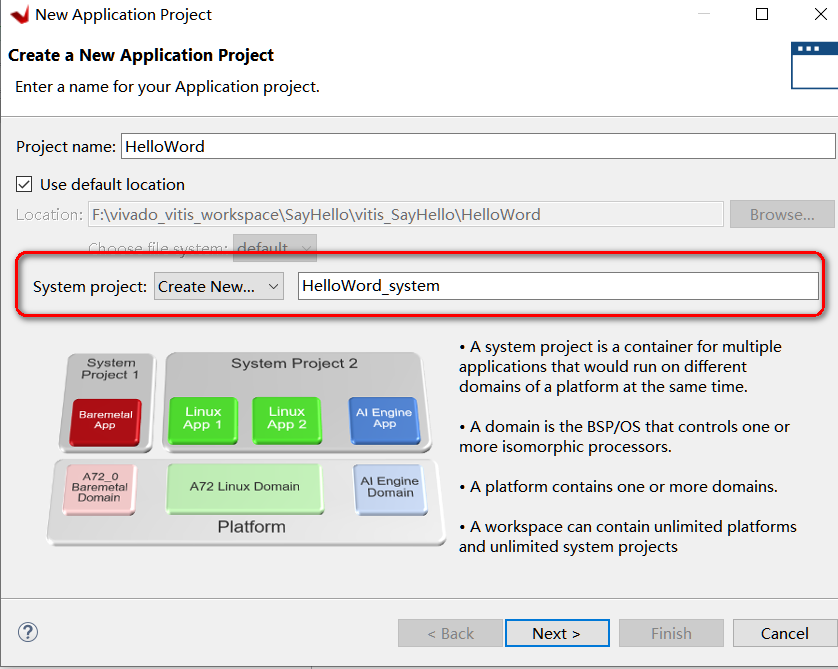

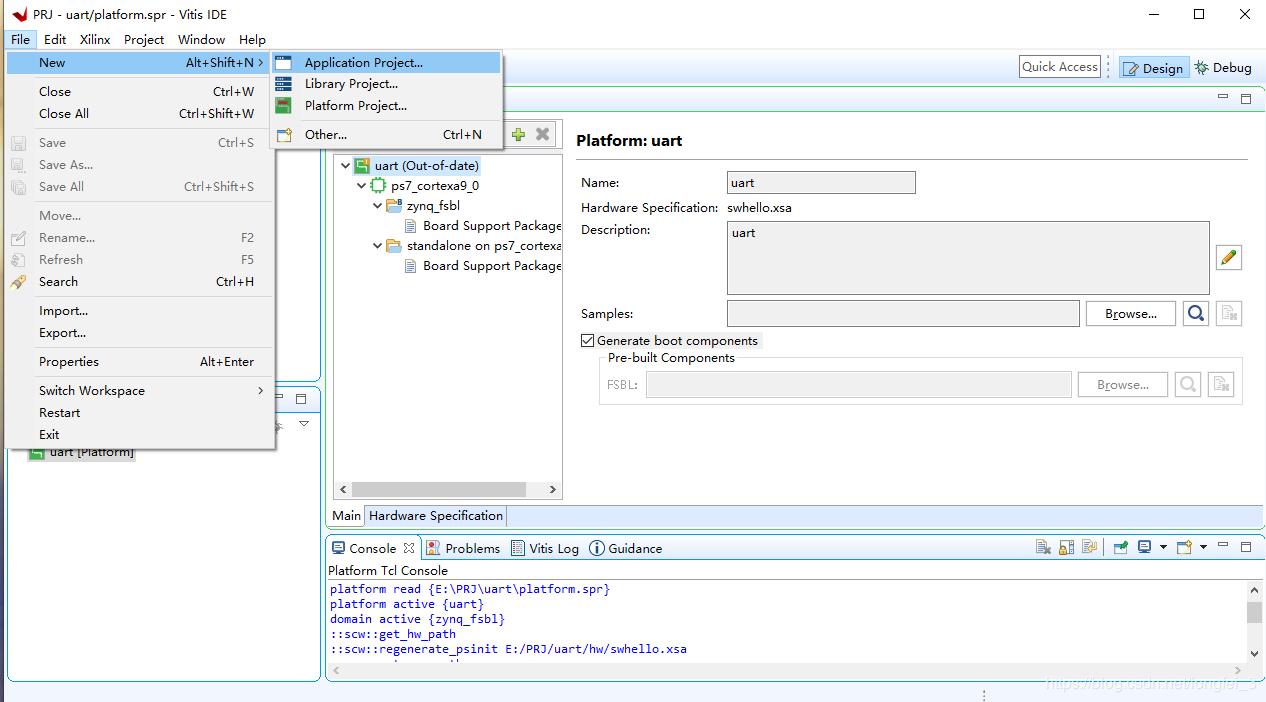

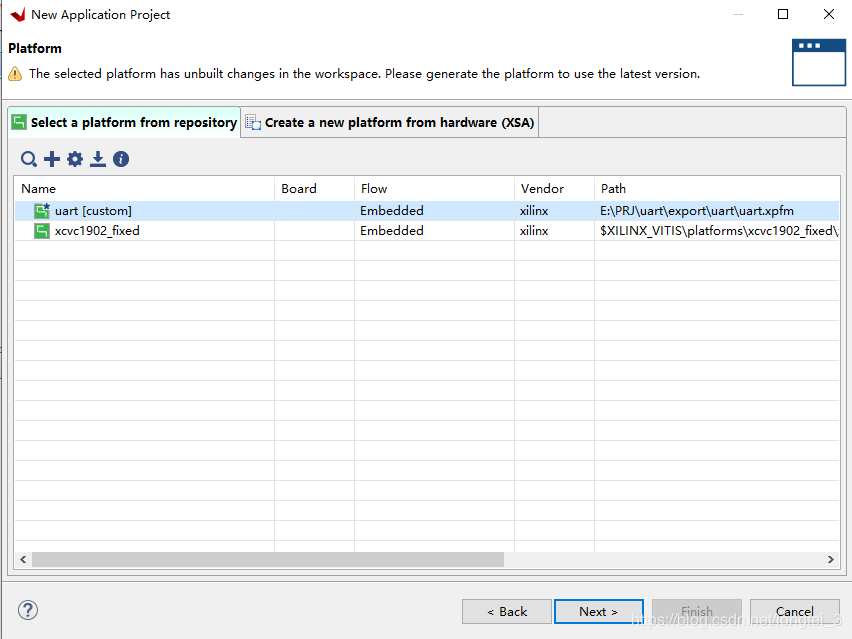

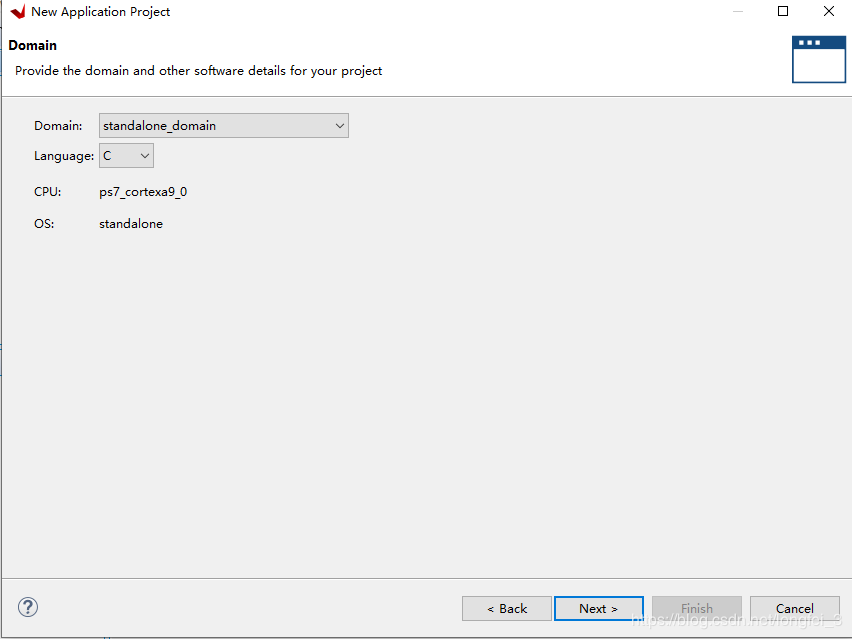

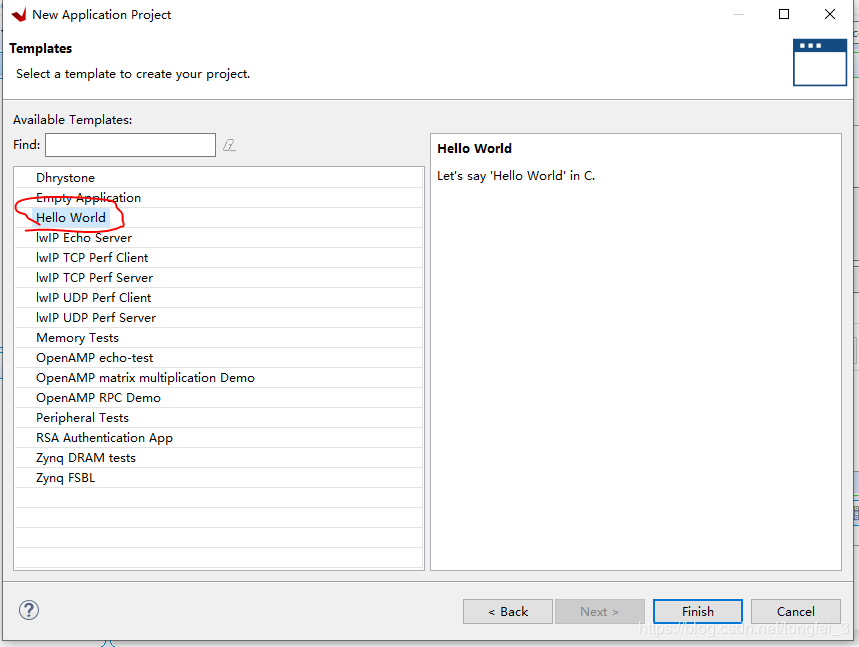

創(chuàng)建一個(gè)Application project:

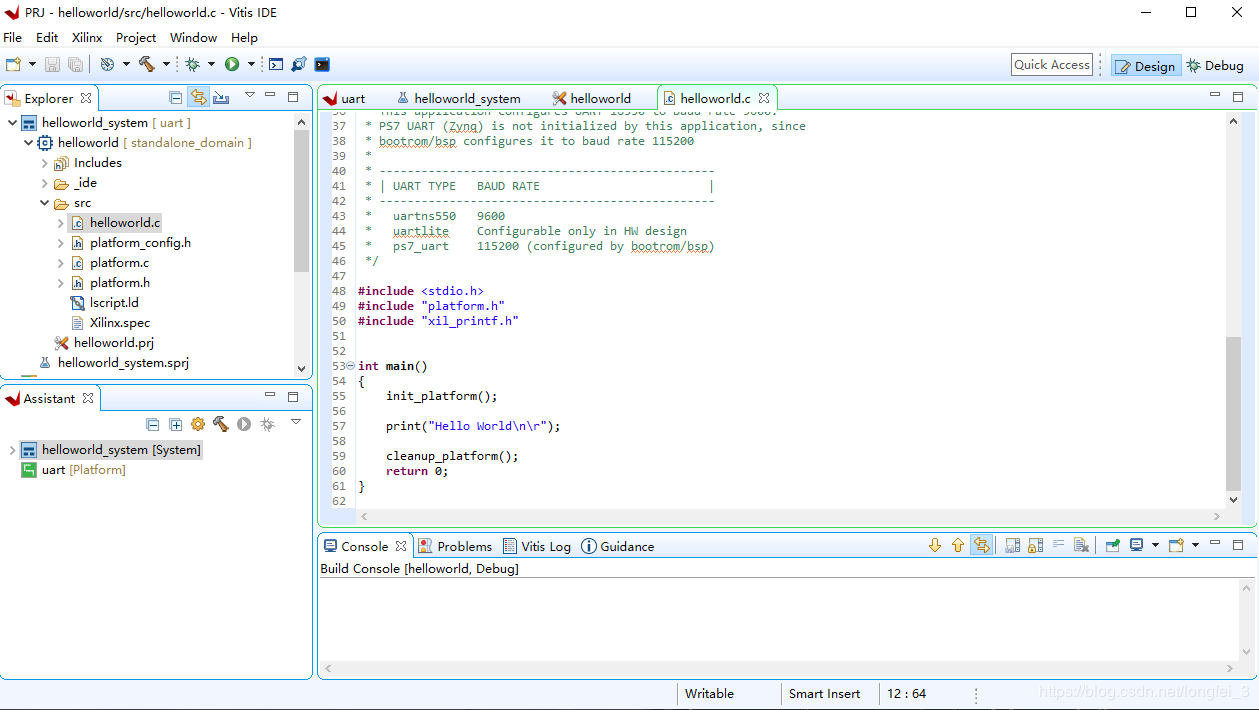

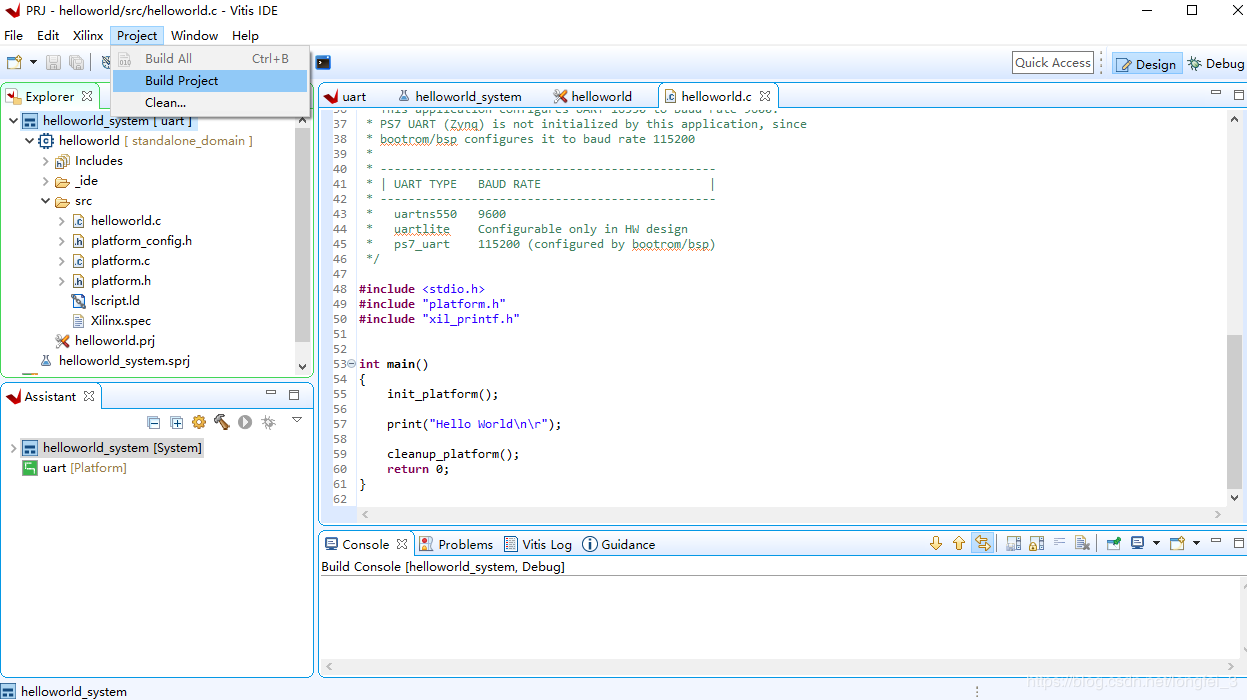

編譯helloworld工程

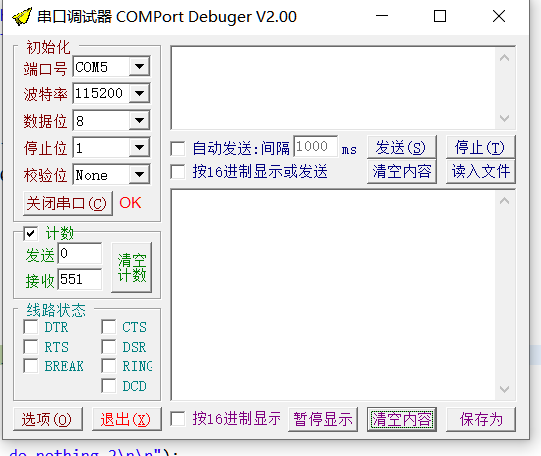

給板子接好上電,連接串口助手軟件,打開串口設(shè)置如下,com口根據(jù)實(shí)際而定。

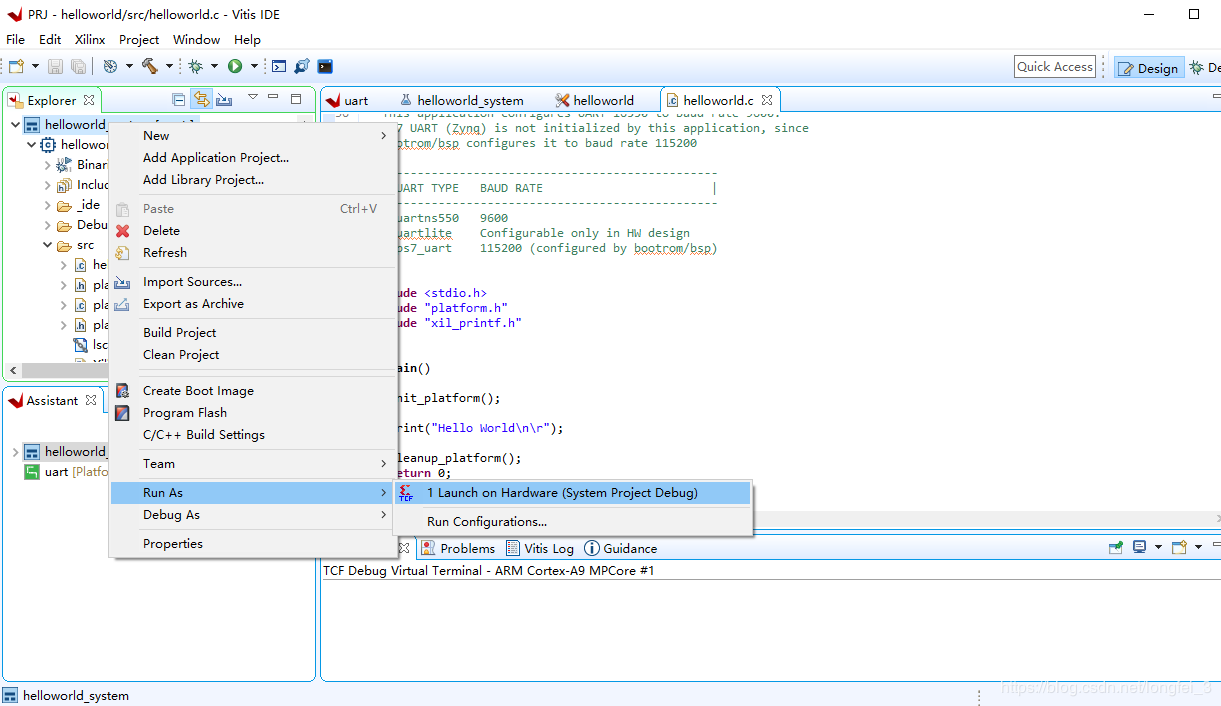

下載運(yùn)行

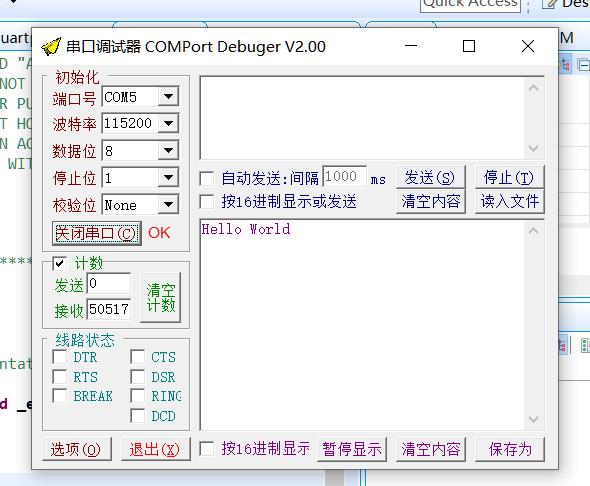

已經(jīng)輸出了“hello world”

移植vivado2019.2之前版本的SOC工程:

1)Vivado部分:

使用Vivado 2019.2打開之前版本的vivado工程項(xiàng)目 ,重新綜合生成bit流文件,如果工程中不設(shè)計(jì)PL部分則不需要生成bit文件。綜合通過(guò)之后導(dǎo)出硬件

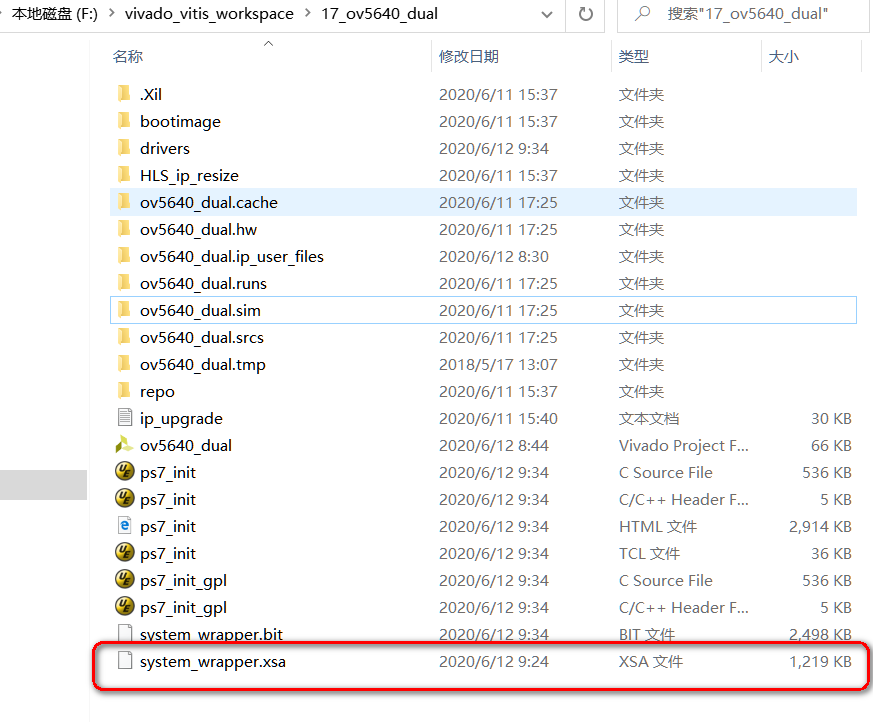

File——Export——Export HardWare,導(dǎo)出成功后會(huì)發(fā)現(xiàn)在vivado工程路徑中會(huì)多出一個(gè).XSA文件(個(gè)人理解與SDK導(dǎo)出的Hdf文件大同小異);

2)Vitis部分:

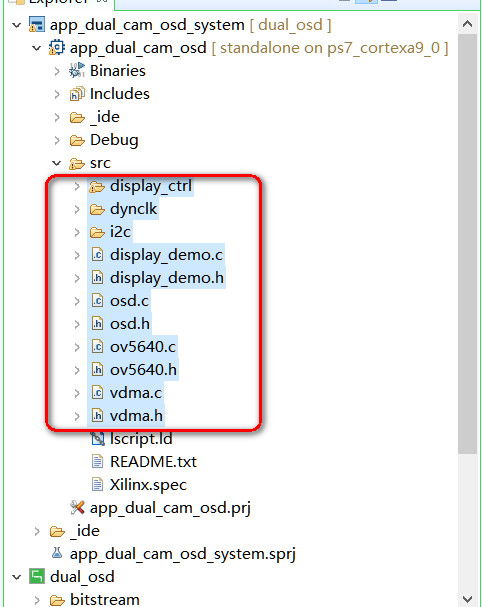

打開Vitis工具,創(chuàng)建一個(gè)Platform,設(shè)置項(xiàng)目名,添加vivado工程路徑中的.XSA文件。創(chuàng)建完P(guān)latform之后接下來(lái)創(chuàng)建一個(gè)Application項(xiàng)目,復(fù)制原工程SDK中的相應(yīng)文件(.c和.h),粘貼到Vitis Apllication。

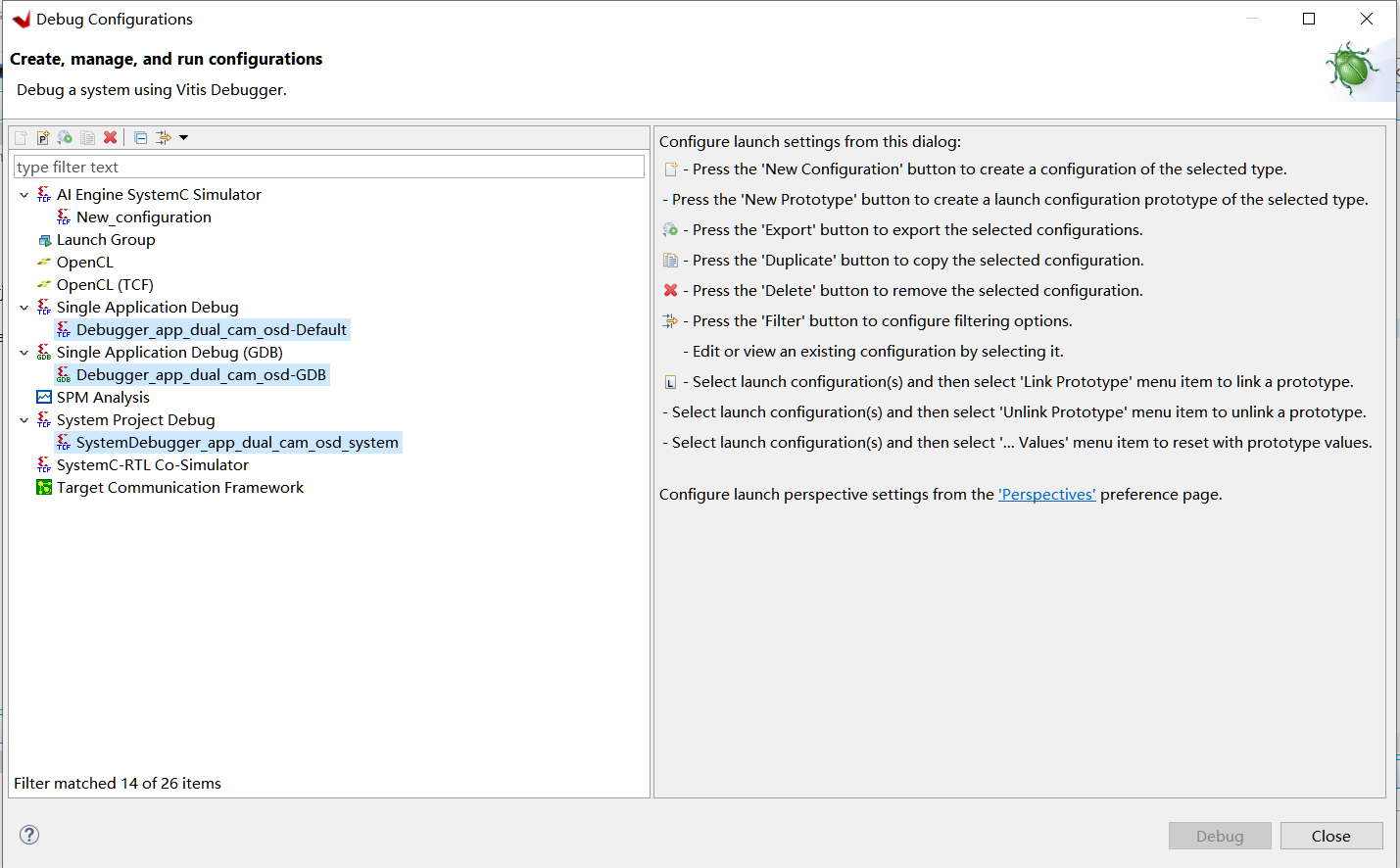

點(diǎn)擊編譯。右鍵app——DebugAs——DebugConfigurations

嘗試分別選擇上圖中3個(gè)Debug Configuration,運(yùn)行均能正確實(shí)現(xiàn)原SDK工程的功能;

還不清楚這三個(gè)配置有什么區(qū)別。

總結(jié):SDK工程的移植基本沒什么太大的變化,Vitis只是將SDK從Vivado中抽離出來(lái)單獨(dú)運(yùn)行而已;

審核編輯 黃昊宇

-

SDK

+關(guān)注

關(guān)注

3文章

1003瀏覽量

45404 -

Vitis

+關(guān)注

關(guān)注

0文章

145瀏覽量

7310

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD Vitis?設(shè)計(jì)工具中的Libraries新功能介紹

在Windows 10上創(chuàng)建并運(yùn)行AMD Vitis?視覺庫(kù)示例

Vitis2023.2使用之—— updata to Vitis Unified IDE

Vitis2023.2使用之—— classic Vitis IDE

Vitis2023.2全新GUI的功能特性介紹

Vitis 統(tǒng)一軟件平臺(tái)文檔

Vitis加速庫(kù):廣泛且性能優(yōu)化的開源庫(kù)

Vitis AI Library體驗(yàn)之OCR識(shí)別

【KV260視覺入門套件試用體驗(yàn)】Vitis AI 構(gòu)建開發(fā)環(huán)境,并使用inspector檢查模型

【KV260視覺入門套件試用體驗(yàn)】Vitis-AI加速的YOLOX視頻目標(biāo)檢測(cè)示例體驗(yàn)和原理解析

基于Vitis AI的ADAS目標(biāo)識(shí)別

Vitis軟件平臺(tái)、vitis實(shí)例、裸機(jī)SOC(SDK)程序移植教程

Vitis軟件平臺(tái)、vitis實(shí)例、裸機(jī)SOC(SDK)程序移植教程

評(píng)論