原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處(http://www.alinx.com)。

適用于板卡型號:

PGL22G/PGL12G

1. 實驗簡介

HDMI做為視頻輸出輸入接口已經(jīng)廣泛使用很長時間,主要通過TMDS差分編碼傳輸。本實驗通過在HDMI屏幕上顯示彩條,來練習(xí)視頻的時序和視頻顏色的表示,為后面視頻處理實驗做個基礎(chǔ)。

2. 實驗原理

2.1 硬件介紹

開發(fā)板使用4對TMDS差分顯示, 其中一對是時鐘,其他三對是數(shù)據(jù)。

HDMI采用和DVI相同的傳輸原理——TMDS(Transition Minimized Differential signal),最小化傳輸差分信號。

TMDS傳輸系統(tǒng)分為分為兩個部分:發(fā)送端和接收端。TMDS發(fā)送端收到HDMI接口傳來的表示RGB信號的24位并行數(shù)據(jù)(TMDS對每個像素的RGB三原色分別按8bit編碼,即R信號有8位,G信號有8位,B信號有8位),然后對這些數(shù)據(jù)進行編碼和并/串轉(zhuǎn)換,再將表示3個RGB信號的數(shù)據(jù)分別分配到獨立的傳輸通道發(fā)送出去。接收端接收來自發(fā)送端的串行信號,對其進行解碼和串/并轉(zhuǎn)換,然后發(fā)送到顯示器的控制端。與此同時也接收時鐘信號,以實現(xiàn)同步。

TMDS的原理

每一個TMDS鏈路都包括3個傳輸RGB信號的數(shù)據(jù)通道和1個傳輸時鐘信號的通道。每一個數(shù)據(jù)通道都通過編碼算法,將8位的視、音頻數(shù)據(jù)轉(zhuǎn)換成最小化傳輸、直流平衡的10位數(shù)據(jù)。這使得數(shù)據(jù)的傳輸和恢復(fù)更加可靠。最小化傳輸差分信號是通過異或及異或非等邏輯算法將原始8位信號數(shù)據(jù)轉(zhuǎn)換成10位,前8為數(shù)據(jù)由原始信號經(jīng)運算后獲得,第9位指示運算的方式,第10位用來對應(yīng)直流平衡。

一般來說,HDMI傳輸?shù)木幋a格式中要包含視頻數(shù)據(jù)、控制數(shù)據(jù)和數(shù)據(jù)包(數(shù)據(jù)包中包含音頻數(shù)據(jù)和附加信息數(shù)據(jù),例如糾錯碼等)。TMDS每個通道在傳輸時要包含一個2bit的控制數(shù)據(jù)、8bit的視頻數(shù)據(jù)或者4bit的數(shù)據(jù)包即可。在HDMI信息傳輸過程中,可以分為三個階段:視頻數(shù)據(jù)傳輸周期、控制數(shù)據(jù)傳輸周期和數(shù)據(jù)島傳輸周期,分別對應(yīng)上述的三種數(shù)據(jù)類型。

下面介紹TMDS中采用的技術(shù):

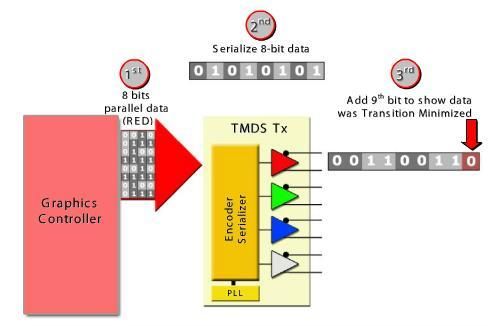

1.傳輸最小化

8位數(shù)據(jù)經(jīng)過編碼和直流平衡得到10位最小化數(shù)據(jù),這仿佛增加了冗余位,對傳輸鏈路的帶寬要求更高,但事實上,通過這種算法得到的10位數(shù)據(jù)在更長的同軸電纜中傳輸?shù)目煽啃栽鰪娏恕O聢D是一個例子,說明對一個8位的并行RED數(shù)據(jù)編碼、并/串轉(zhuǎn)換。

第一步:將8位并行RED數(shù)據(jù)發(fā)送到TMDS發(fā)送端。

第二步:并/串轉(zhuǎn)換.

第三步:進行最小化傳輸處理,加上第9位,即編碼過程。第9位數(shù)據(jù)稱為編碼位。

2.直流平衡

直流平衡(DC-balanced)就是指在編碼過程中保證信道中直流偏移為零。方法是在原來的9位數(shù)據(jù)的后面加上第10位數(shù)據(jù),這樣,傳輸?shù)臄?shù)據(jù)趨于直流平衡,使信號對傳輸線的電磁干擾減少,提高信號傳輸?shù)目煽啃浴?/p>

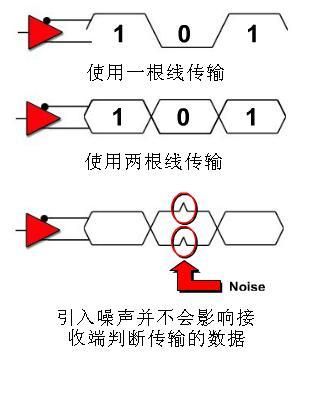

3.差分信號

TMDS差分傳動技術(shù)是一種利用2個引腳間電壓差來傳送信號的技術(shù)。傳輸數(shù)據(jù)的數(shù)值(“0”或者“1”)由兩腳間電壓正負極性和大小決定。即,采用2根線來傳輸信號,一根線上傳輸原來的信號,另一根線上傳輸與原來信號相反的信號。這樣接收端就可以通過讓一根線上的信號減去另一根線上的信號的方式來屏蔽電磁干擾,從而得到正確的信號。

如下圖所示:

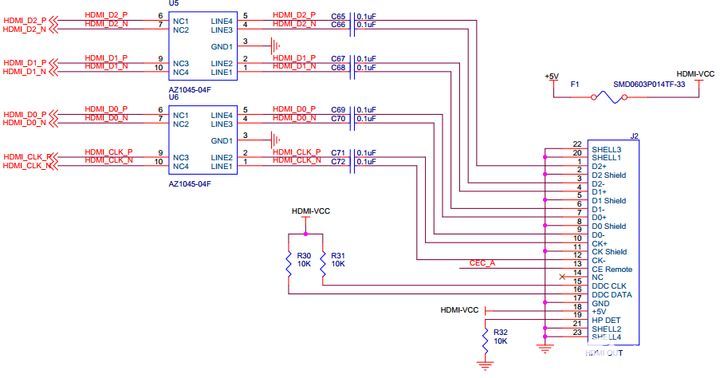

另外,還有一個顯示數(shù)據(jù)通道(DDC),是用于讀取表示接收端顯示器的清晰度等顯示能力的擴展顯示標識數(shù)據(jù)(EDID)的信號線。搭載HDCP(High-bandwidth Digital Content Protection,高帶寬數(shù)字內(nèi)容保護技術(shù))的發(fā)送、接收設(shè)備之間也利用DDC線進行密碼鍵的認證。

HDMI輸出部分電路

2.2 視頻時序標準

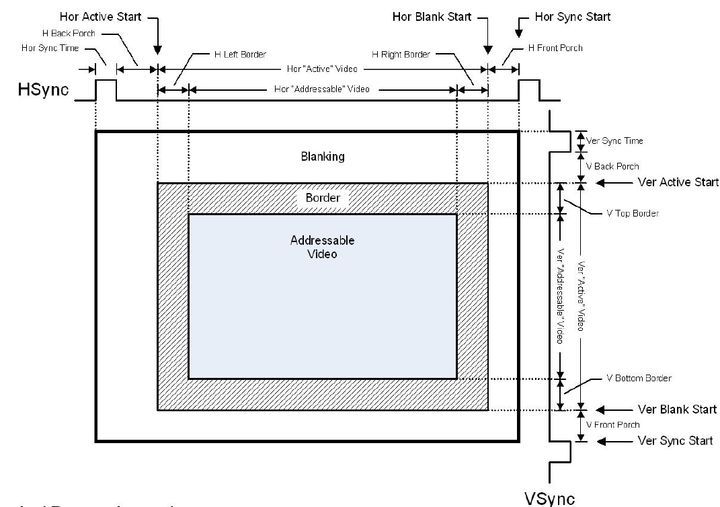

HDMI顯示器掃描方式從屏幕左上角一點開始,從左向右逐點掃描,每掃描完一行,電子束回到屏幕的左邊下一行的起始位置,在這期間,CRT對電子束進行消隱,每行結(jié)束時,用行同步信號進行同步;當掃描完所有的行,形成一幀,用場同步信號進行場同步,并使掃描回到屏幕左上方,同時進行場消隱,開始下一幀。

完成一行掃描的時間稱為水平掃描時間,其倒數(shù)稱為行頻率;完成一幀(整屏)掃描的時間稱為垂直掃描時間,其倒數(shù)稱為場頻率,即刷新一屏的頻率,常見的有60Hz,75Hz等等。標準的顯示的場頻60Hz。

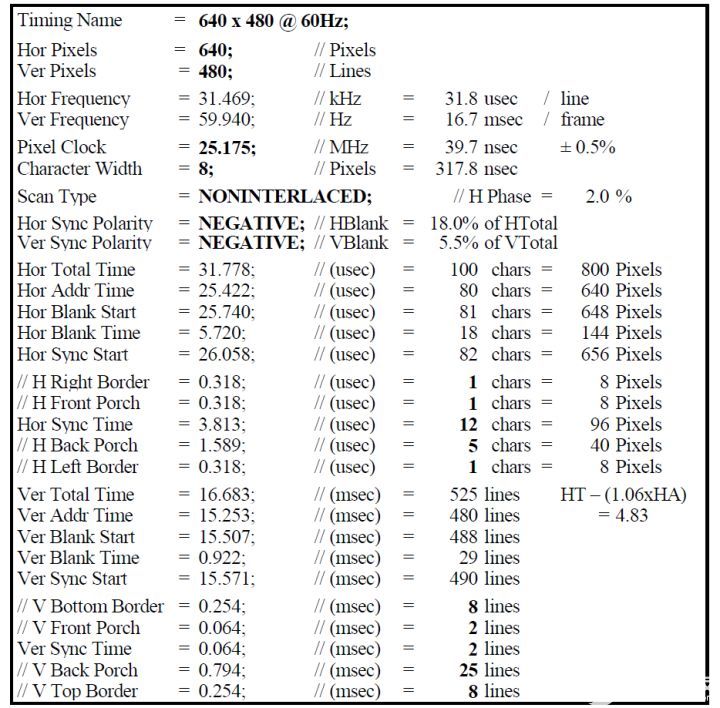

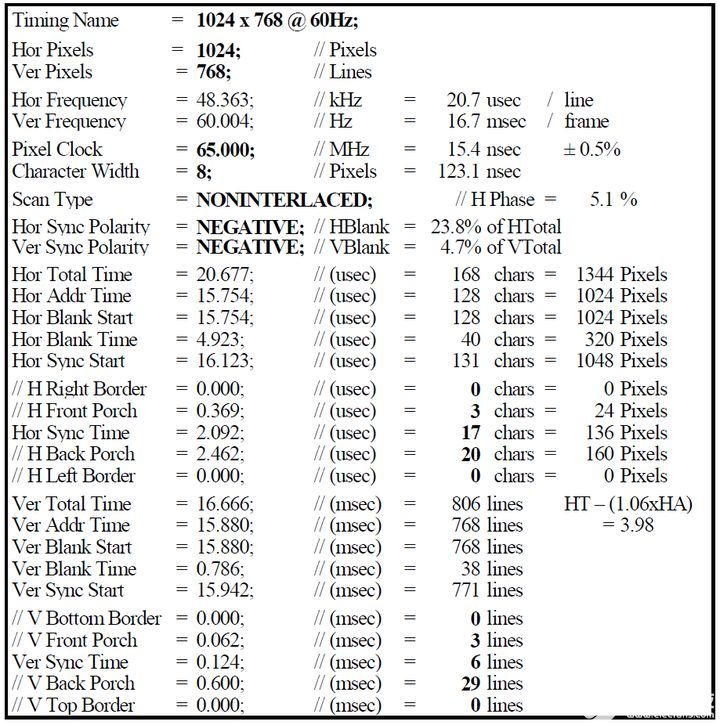

時鐘頻率:以1024x768@59.94Hz(60Hz)為例,每場對應(yīng)806個行周期,其中768為顯示行。每顯示行包括1344點時鐘,其中1024點為有效顯示區(qū)。由此可知:需要點時鐘頻率:806*1344*60約65MHz。

視頻時序

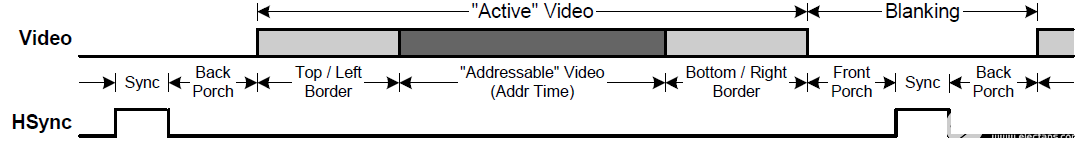

VGA掃描,基本元素是行掃描,多行組成一幀,下圖顯示一行的時序,其中“Active”Video是一行視頻的有效像素,大部分分辨率時鐘中Top/Left Border 和 Bottom / Right Border都是0。“Blanking”是一行的同步時間,“Blanking”時間加上Active”Video時間就是一行的時間。“Blanking”又分為“Front Porch”、“Sync”、“Back Porch”三段。

行同步時序

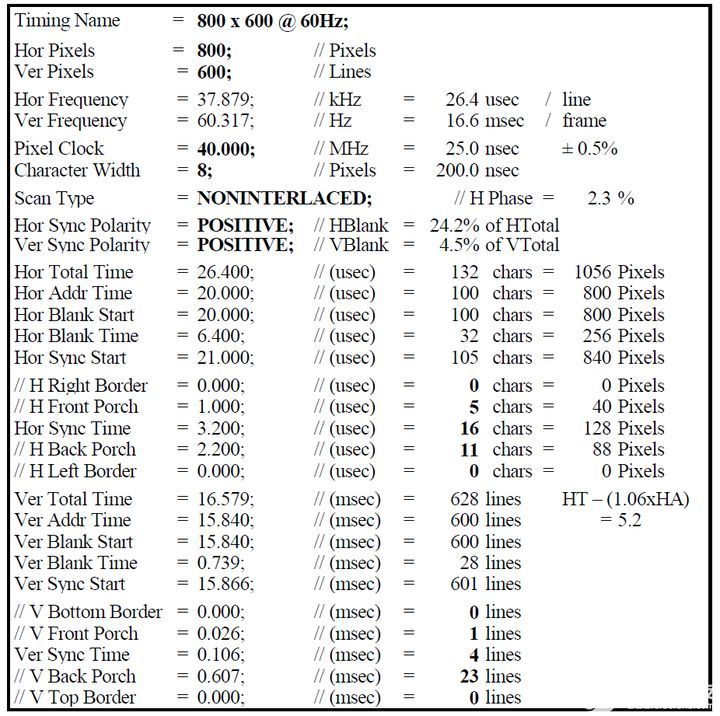

常見分辨率時序

640x480@60Hz時序參數(shù)

800x600@60Hz時序參數(shù)

1024x768@60Hz時序參數(shù)

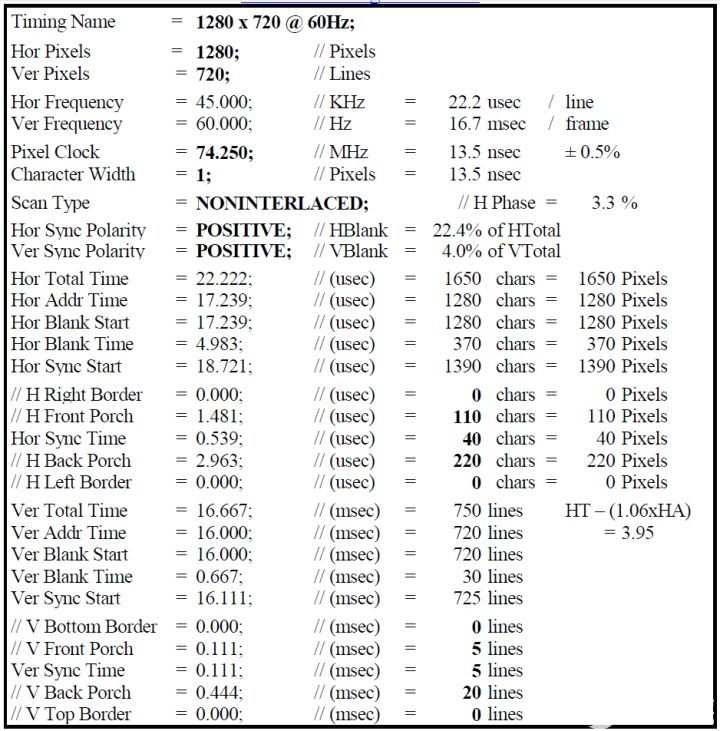

1280x720@60Hz時序參數(shù)

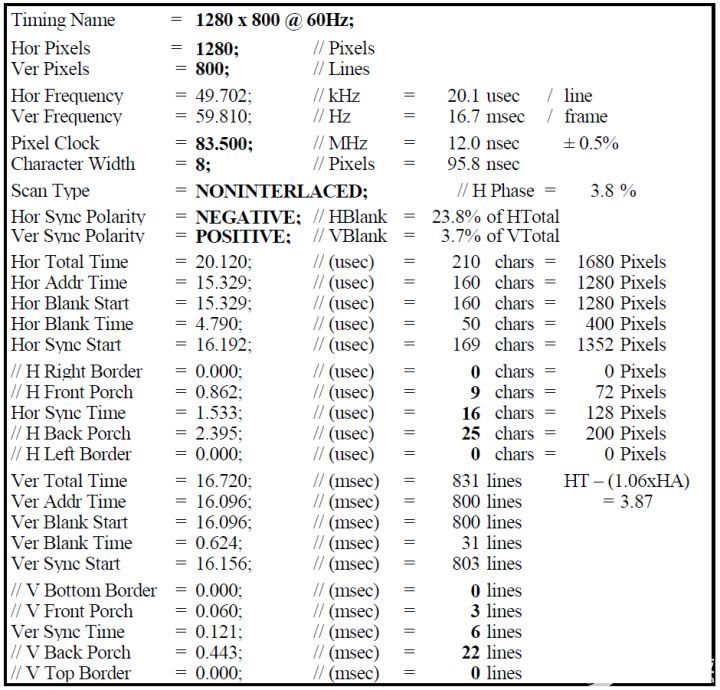

1280x800@60Hz時序參數(shù)

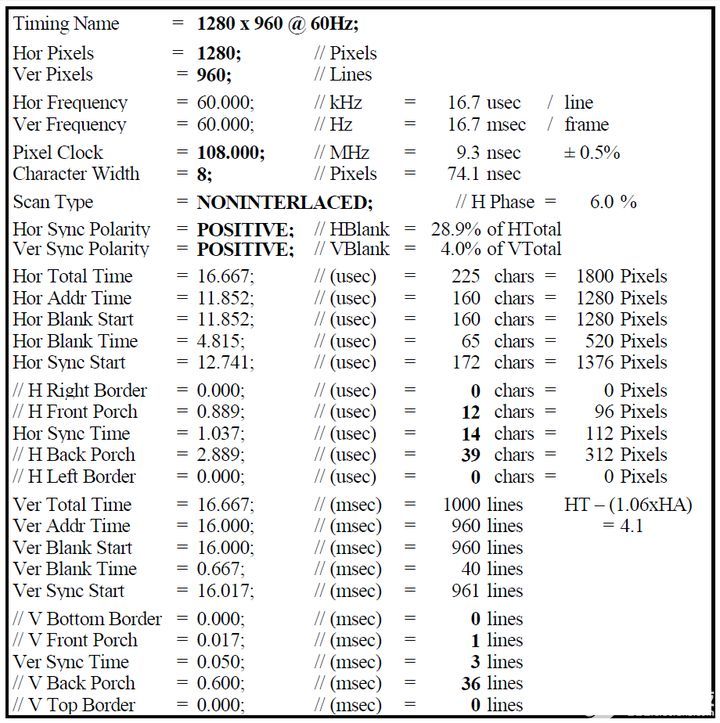

1280x960@60Hz時序參數(shù)

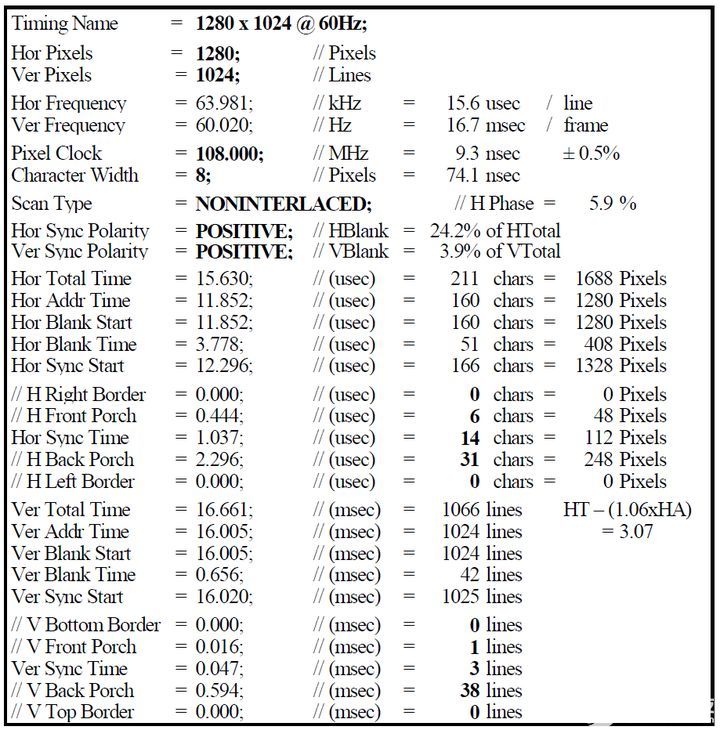

1280x1024@60Hz時序參數(shù)

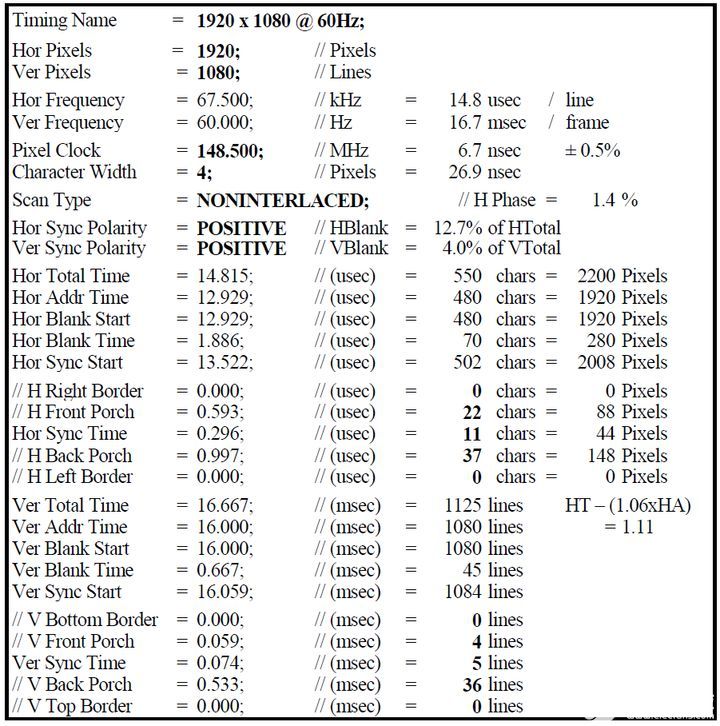

1920x1080@60Hz時序參數(shù)

3. HDMI輸出程序設(shè)計

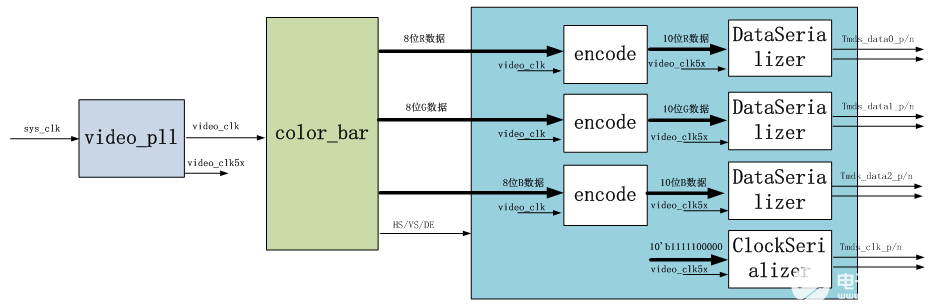

本實驗將實現(xiàn)HDMI輸出顯示,verilog實現(xiàn)編程驅(qū)動HDMI輸出,在HDMI顯示器里顯示測試圖像彩條。HDMI輸出顯示模塊分成3個模塊實現(xiàn),分別是時鐘模塊vidio_pll, 彩條生成模塊color_bar和VGA轉(zhuǎn)DVI模塊dvi_encoder。實現(xiàn)的邏輯框圖如下:

1. 彩條產(chǎn)生模塊color_bar.v

color_bar.v是產(chǎn)生8種顏色的VGA格式的彩條,彩條分別為白、黃、青、綠、紫、紅、藍和黑。針對VGA的時序,行同步和場同步各使用一個計數(shù)器,行同步計數(shù)器用于產(chǎn)生行同步,行有效像素,場同步計數(shù)器用于產(chǎn)生場同步,場有效像素。同時根據(jù)計數(shù)器的值可以產(chǎn)生水平(X)和垂直(Y)坐標,通過坐標信息,可以實時顯示一些圖形。程序中預(yù)設(shè)了幾種分辨率的時序參數(shù),包括2款LCD液晶屏的,為后續(xù)的LCD驗證試驗做準備。

2. VGA轉(zhuǎn)DVI模塊dvi_encoder

dvi_encoder模塊中包含兩個模塊encode和serdes_4b_10to1模塊,實現(xiàn)RGB格式的圖像轉(zhuǎn)化成TMDS差分輸出,來驅(qū)動HDMI顯示。

1). encode: 紅,綠,藍的8位視頻數(shù)據(jù)及時鐘編碼成10位的TMDS視頻數(shù)據(jù)。關(guān)于編碼的原因和方法我們已經(jīng)在前面介紹過,具體如何實現(xiàn),有興趣的同學(xué)可以參考文檔"08_其它學(xué)習(xí)資料\TMDS視頻數(shù)據(jù)編碼.doc"

2). serdes_4b_10to1:方法是通過兩個OSERDESE2的串聯(lián)把10比特的并行數(shù)據(jù)轉(zhuǎn)換成串行發(fā)送出去。

4. HMDI輸出試驗現(xiàn)象

連接好開發(fā)板和顯示器,需要注意,開發(fā)板的各個連接器不要帶電熱插拔,下載好試驗程序,可以看到顯示器顯示8條彩條。開發(fā)板做為HDMI輸出設(shè)備,只能通過HDMI顯示設(shè)備來顯示,不要試圖通過筆記本電腦的HDMI接口來顯示,因為筆記本的HDMI接口也是輸出設(shè)備。

HDMI顯示器連接

彩條顯示

在用開發(fā)板做4.3寸LCD、7寸LCD屏顯示實驗時,LCD模塊接開發(fā)板的J8擴展口,注意管腳不要接錯。

如下圖所示:

開發(fā)板與LCD屏連接

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601858 -

HDMI

+關(guān)注

關(guān)注

32文章

1664瀏覽量

151660 -

編程

+關(guān)注

關(guān)注

88文章

3592瀏覽量

93596 -

TMDS

+關(guān)注

關(guān)注

1文章

21瀏覽量

15497 -

紫光同創(chuàng)

+關(guān)注

關(guān)注

5文章

82瀏覽量

27487

發(fā)布評論請先 登錄

相關(guān)推薦

國產(chǎn)FPGA介紹-紫光同創(chuàng)

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板,接口豐富,高性價比

Sklearn與TensorFlow機器學(xué)習(xí)實用指南——第九章習(xí)題答案

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板,接口豐富,高性價比

紫光同創(chuàng)FPGA開發(fā)套件,高性能國產(chǎn)FPGA方案

功率放大電路問答第九章

振幅調(diào)制與解調(diào) 第九章

單片機c語言教程第九章--C51運算符和表達式(指針和地址運

【正點原子FPGA連載】第九章按鍵控制LED燈實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

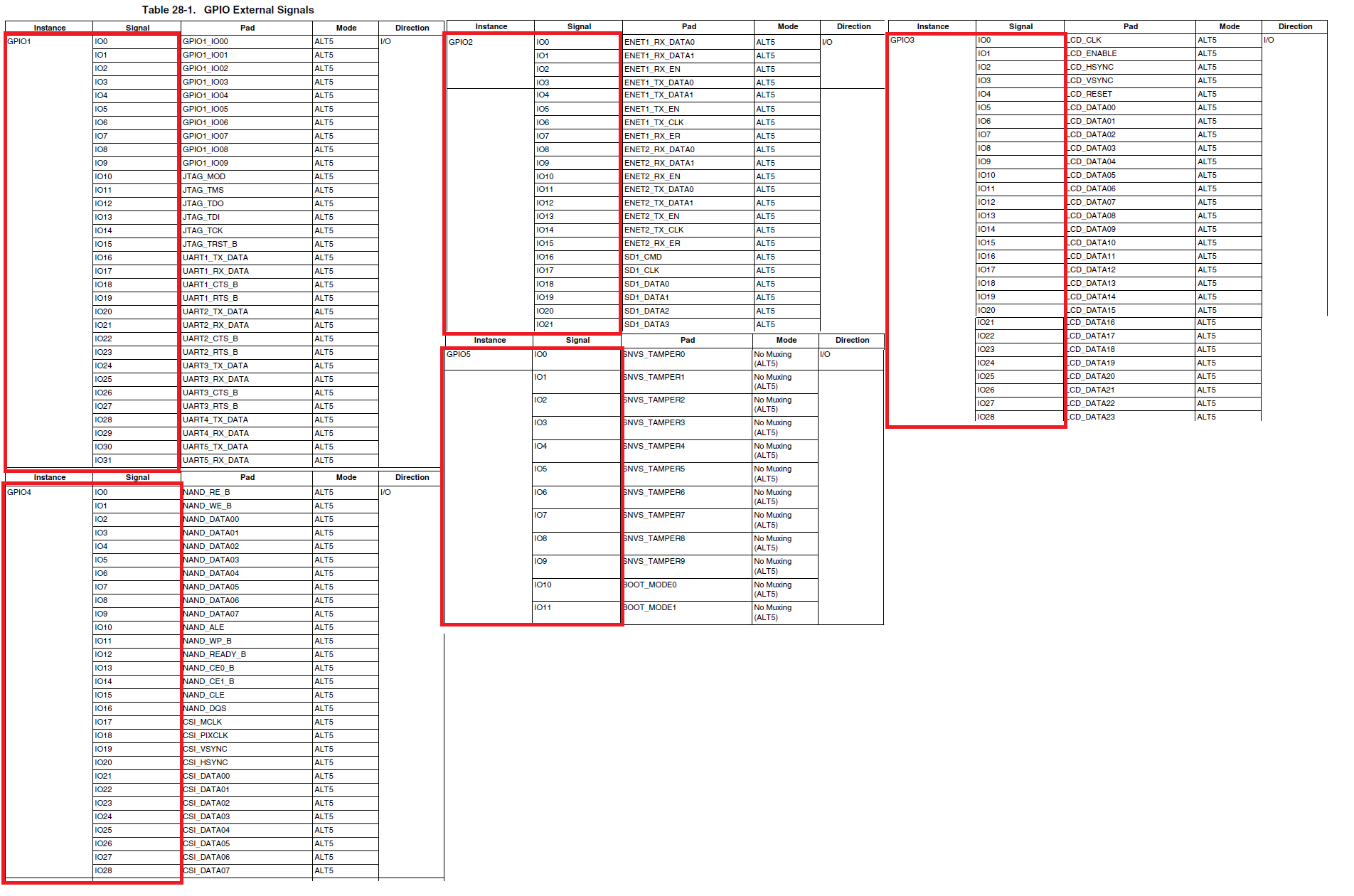

Linux應(yīng)用開發(fā)【第九章】GPIO編程應(yīng)用開發(fā)

第九章 數(shù)模和模數(shù)轉(zhuǎn)換

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第九章】HDMI編程測試實驗

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第九章】HDMI編程測試實驗

評論