量子計算是未來信息技術發展的重要方向,在一些特定領域具有較大應用潛力。基于硅量子點的量子比特是實現通用量子計算最有前景的方案之一,具有較長的退相干時間和出色的CMOS制造工藝兼容性。目前,硅量子點量子計算正處在采用集成電路先進制造工藝實現量子點規模集成并進行量子比特擴展驗證的關鍵研究階段。

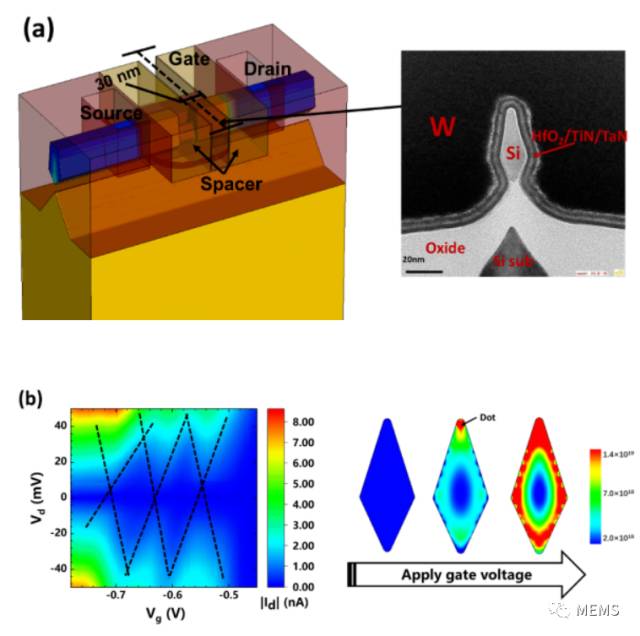

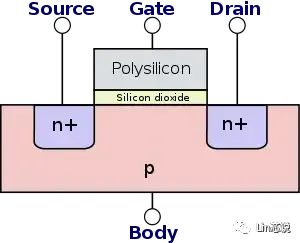

近期,中國科學院微電子研究所集成電路先導工藝研發中心研究員殷華湘帶領的科研團隊基于主流的體硅高κ/金屬柵FinFET工藝,提出了一種利用拐角效應,在鉆石形Fin溝道頂部尖端實現載流子局域化,并借助柵極兩邊側墻的電勢限制,構建量子點器件結構的方案。該器件在先導中心8吋工藝線研制成功,集成方案完全兼容主流通用的先進CMOS工藝。在制備過程中,研究人員先后優化了Fin刻蝕、淺槽隔離等關鍵工藝,;在高κ/金屬柵后柵工藝中,利用氧化腐蝕的方法完成了襯底隔離的鉆石形硅Fin溝道形貌修飾。在20 K低溫電學測試中,該器件展示出明顯的庫倫振蕩電流。研究人員通過分析庫倫菱形穩定圖,證明了該器件擁有較大的量子點充電能,具備在傳統CMOS FinFET工藝中實現量子點規模化集成的潛力。

(a)器件結構示意圖及溝道截面TEM分析;(b)庫倫菱形穩定圖及部分仿真分析

?

相關研究成果發表在《電氣和電子工程師協會電子器件學報》(IEEE Transactions on Electron Devices,DOI: 10.1109/TED.2020.3039734)上,微電子所博士生顧杰為論文第一作者。殷華湘、微電子所副研究員張青竹為論文的通訊作者。研究工作得到科學技術部、國家自然科學基金委、中科院的支持。

責任編輯:lq

-

CMOS

+關注

關注

58文章

5689瀏覽量

235171 -

微電子

+關注

關注

18文章

377瀏覽量

41175 -

FinFET

+關注

關注

12文章

247瀏覽量

90156 -

量子計算

+關注

關注

4文章

1081瀏覽量

34910

原文標題:微電子所在基于先進FinFET工藝的硅量子器件研究中獲進展

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高K金屬柵極的結構、材料、優勢以及工藝流程

當前主流的大模型對于底層推理芯片提出了哪些挑戰

場效應管柵源極電壓的影響因素

結型場效應管和金屬氧化物場效應管的分類

高k金屬柵(HKMG)工藝詳解

場效應管放大電路的原理

FinFET工藝之self-heating概念介紹

基于主流的體硅高κ/金屬柵FinFET工藝,提出了一種利用拐角效應

基于主流的體硅高κ/金屬柵FinFET工藝,提出了一種利用拐角效應

評論