本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處(http://www.alinx.com)。

適用于板卡型號:

PGL22G/PGL12G

1. 實驗簡介

本實驗練習(xí)使用ADC,實驗中使用的ADC模塊型號為AN706,最大采樣率200Khz,精度為16位。實驗中把AN706的2路輸入以波形方式在HDMI上顯示出來,我們可以用更加直觀的方式觀察波形,是一個數(shù)字示波器雛形。

8路200K采樣16位ADC模塊實驗預(yù)期結(jié)果

2. 實驗原理

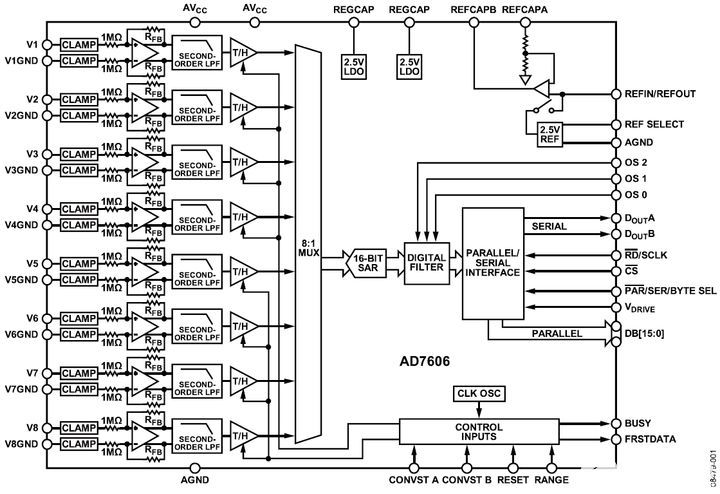

AD7606是一款集成式8通道同步采樣數(shù)據(jù)采集系統(tǒng),片內(nèi)集成輸入放大器、過壓保護(hù)電路、二階模擬抗混疊濾波器、模擬多路復(fù)用器、16位200 kSPS SAR ADC和一個數(shù)字濾波器, 2.5 V基準(zhǔn)電壓源、基準(zhǔn)電壓緩沖以及高速串行和并行接口。

AD7606采用+5V單電源供電, 可以處理±10V和±5V真雙極性輸入信號, 同時所有通道均以高達(dá)200KSPS的吞吐速率采樣。輸入鉗位保護(hù)電路可以耐受最高達(dá)±16.5V的電壓。

無論以何種采樣頻率工作, AD7606的模擬輸入阻抗均為1M歐姆。它采用單電源工作方式, 具有片內(nèi)濾波和高輸入阻抗, 因此無需驅(qū)動運算放大器和外部雙極性電源。

AD7606抗混疊濾波器的3dB截至頻率為22kHz; 當(dāng)采樣速率為200kSPS時, 它具有40dB抗混疊抑制特性。靈活的數(shù)字濾波器采用引腳驅(qū)動, 可以改善信噪比(SNR), 并降低3dB帶寬。

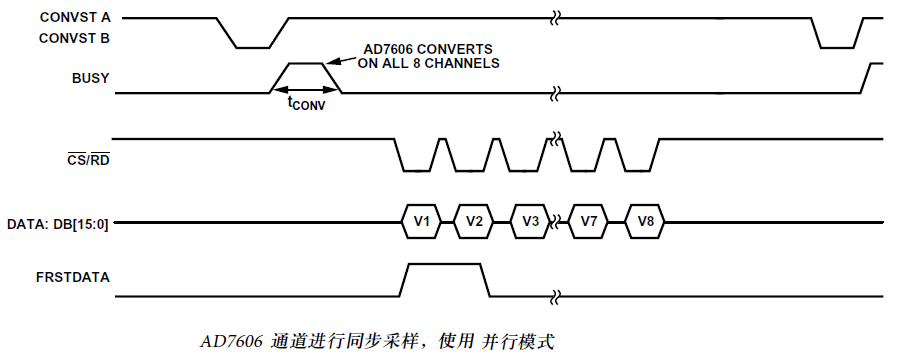

2.1 AD7606時序

AD7606可以對所有8路的模擬輸入通道進(jìn)行同步采樣。當(dāng)兩個CONVST引腳(CONVSTA和CONVSTB)連在一起時, 所有通道同步采樣。此共用CONVST信號的上升沿啟動對所有模擬輸入通道的同步采樣(V1至V8)。

AD7606內(nèi)置一個片內(nèi)振蕩器用于轉(zhuǎn)換。所有ADC通道的轉(zhuǎn)換時間為tCONV。BUSY信號告知用戶正在進(jìn)行轉(zhuǎn)換, 因此當(dāng)施加CONVST上升沿時,BUSY變?yōu)檫壿嫺唠娖剑?在整個轉(zhuǎn)換過程結(jié)束時變成低電平。BUSY信號下降沿用來使所有八個采樣保持放大器返回跟蹤模式。BUSY下降沿還表示,現(xiàn)在可以從并行總線DB[15:0]讀取8個通道的數(shù)據(jù)。

2.2 AD7606配置

在AN706 8通道的AD模塊硬件電路設(shè)計中,我們對AD7606的3個配置Pin腳通過加上拉或下拉電阻來設(shè)置AD7606的工作模式。

AD7606這款芯片支持外部基準(zhǔn)電壓輸入或內(nèi)部基準(zhǔn)電壓。如果使用外部基準(zhǔn)電壓,芯片的REFIN/REFOUT需要外接一個2.5V的基準(zhǔn)源。如果使用內(nèi)部的基準(zhǔn)電壓。REFIN/REFOUT引腳為2.5V的內(nèi)部基準(zhǔn)電壓輸出。REF SELECT引腳用于選擇內(nèi)部基準(zhǔn)電壓或外部基準(zhǔn)電壓。在本模塊中,因為考慮到AD7606的內(nèi)部基準(zhǔn)電壓的精度也非常高(2.49V~2.505V),所以電路設(shè)計選擇使用了內(nèi)部的基準(zhǔn)電壓。

| Pin腳名 | 設(shè)置電平 | 說明 |

| REF SELECT | 高電平 | 使用內(nèi)部的基準(zhǔn)電壓2.5V |

AD7606的AD轉(zhuǎn)換數(shù)據(jù)采集可以采用并行模式或者串行模式, 用戶可以通過設(shè)置PAR/SER/BYTE SEL引腳電平來設(shè)置通信的模式。我們在設(shè)計的時候,選擇并行模式讀取AD7606的AD數(shù)據(jù)。

| Pin腳名 | 設(shè)置電平 | 說明 |

| PAR/SER/BYTE SEL | 低電平 | 選擇并行接口 |

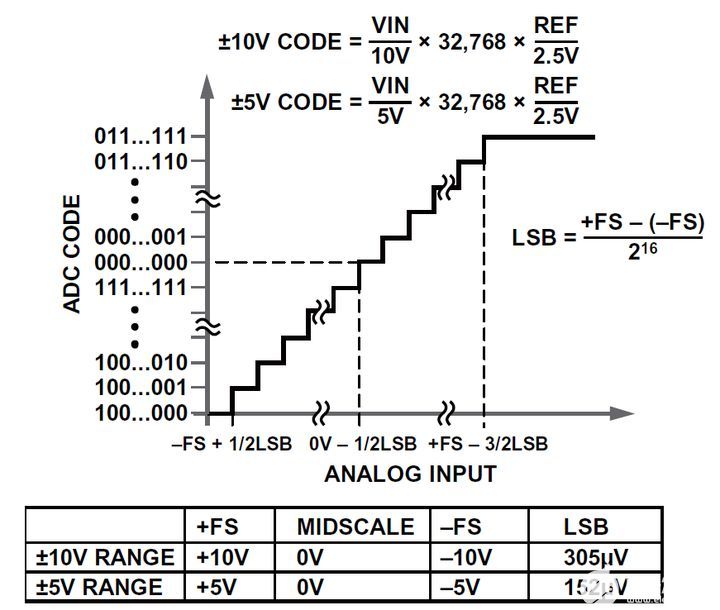

AD7606的AD模擬信號的輸入范圍可以設(shè)置為±5V或者是±10V,當(dāng)設(shè)置±5V輸入范圍時,1LSB=152.58uV;當(dāng)設(shè)置±10V輸入范圍時,1LSB=305.175uV 。用戶可以通過設(shè)置RANGE引腳電平來設(shè)置模擬輸入電壓的范圍。我們在設(shè)計的時候,選擇±5V的模擬電壓輸入范圍。

| Pin腳名 | 設(shè)置電平 | 說明 |

| RANGE | 低電平 | 模擬信號輸入范圍選擇:±5V |

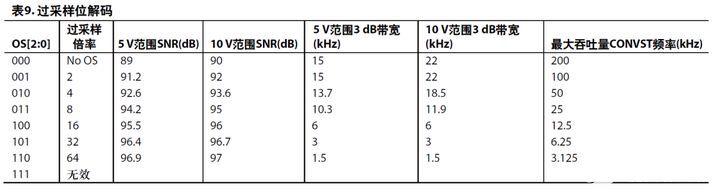

AD7606內(nèi)置一個可選的數(shù)字一階sinc濾波器,在使用較低吞吐率或需要更高信噪比的應(yīng)用中,應(yīng)使用濾波器。數(shù)字濾波器的過采樣倍率由過采樣引腳OS[2:0]控制。下表提供了用來選擇不同過采樣倍率的過采樣位解碼。

在AN706模塊的硬件設(shè)計中, OS[2:0] 已經(jīng)引到外部的接口中,FPGA或CPU可以通過控制OS[2:0]的管腳電平來選擇是否使用濾波器,以達(dá)到更高的測量精度。

2.3 AD7606 AD轉(zhuǎn)換

AD7606的輸出編碼方式為二進(jìn)制補(bǔ)碼。所設(shè)計的碼轉(zhuǎn)換在連續(xù)LSB整數(shù)的中間(既1/2LSB和3/2LSB)進(jìn)行。AD7606的LSB大小為FSR/65536。AD7606的理想傳遞特性如下圖所示:

2.4 程序設(shè)計

本實驗顯示部分是基于前面的已有的實驗,在彩條上疊加網(wǎng)格線和波形。

timing_gen_xy模塊完成視頻圖像的坐標(biāo)生成,x坐標(biāo),從左到右增大,y坐標(biāo)從上到下增大。

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| clk | in | 1 | 系統(tǒng)時鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 視頻行同步輸出 |

| o_vs | out | 1 | 視頻場同步輸出 |

| o_de | out | 1 | 視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 視頻數(shù)據(jù)輸出 |

| x | out | 12 | 坐標(biāo)x輸出 |

| y | out | 12 | 坐標(biāo)y輸出 |

timing_gen_xy模塊端口

grid_display模塊主要完成視頻的網(wǎng)格線疊加,本實驗將彩條視頻輸入,然后疊加一個網(wǎng)格后輸出,提供給后面的波形顯示模塊使用。

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| pclk | in | 1 | 像素時鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 帶網(wǎng)格視頻行同步輸出 |

| o_vs | out | 1 | 帶網(wǎng)格視頻場同步輸出 |

| o_de | out | 1 | 帶網(wǎng)格視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 帶網(wǎng)格視頻數(shù)據(jù)輸出 |

grid_display模塊端口

wav_display顯示模塊主要是完成波形數(shù)據(jù)的疊加顯示,模塊內(nèi)含有一個雙口ram,寫端口是由ADC采集模塊寫入,讀端口是顯示模塊。

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| pclk | in | 1 | 像素時鐘 |

| rst_n | in | 1 | 異步復(fù)位,低電平復(fù)位 |

| wave_color | in | 24 | 波形顏色,rgb |

| adc_clk | in | 1 | adc模塊時鐘 |

| adc_buf_wr | in | 1 | adc數(shù)據(jù)寫使能 |

| adc_buf_addr | in | 12 | adc數(shù)據(jù)寫地址 |

| adc_buf_data | in | 8 | adc數(shù)據(jù),無符號數(shù) |

| i_hs | in | 1 | 視頻行同步輸入 |

| i_vs | in | 1 | 視頻場同步輸入 |

| i_de | in | 1 | 視頻數(shù)據(jù)有效輸入 |

| i_data | in | 24 | 視頻數(shù)據(jù)輸入 |

| o_hs | out | 1 | 帶網(wǎng)格視頻行同步輸出 |

| o_vs | out | 1 | 帶網(wǎng)格視頻場同步輸出 |

| o_de | out | 1 | 帶網(wǎng)格視頻數(shù)據(jù)有效輸出 |

| o_data | out | 24 | 帶網(wǎng)格視頻數(shù)據(jù)輸出 |

wav_display模塊端口

ad7606_sample模塊有符號數(shù)轉(zhuǎn)換為無符號數(shù),最后位寬轉(zhuǎn)換到8bit。

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| adc_clk | in | 1 | adc系統(tǒng)時鐘 |

| rst | in | 1 | 異步復(fù)位,高復(fù)位 |

| adc_data | in | 16 | ADC數(shù)據(jù)輸入 |

| adc_data_valid | in | 1 | adc數(shù)據(jù)有效 |

| adc_buf_wr | out | 1 | ADC數(shù)據(jù)寫使能 |

| adc_buf_addr | out | 12 | ADC數(shù)據(jù)寫地址 |

| adc_buf_data | out | 8 | 無符號8位ADC數(shù)據(jù) |

ad7606_sample模塊端口

3. 實驗現(xiàn)象

-

將AN706模塊插入開發(fā)板的擴(kuò)展口 J8,注意1腳對齊,不要插錯、插偏,不能帶電操作。

-

連接AN706的輸入到信號發(fā)生器的輸出,AN706模塊本身沒有焊接SMA插頭,本實驗為了方便,自行焊接了一個SMA插頭。

AN706連接信號源示意圖

1)連接HDMI顯示器,注意:連接的是顯示器,不是筆記本電腦HDMI接口

HDMI接口連接示意圖

2)下載程序,調(diào)節(jié)信號發(fā)生的頻率和幅度,AN706輸入范圍-5V-5V,為了便于觀察波形數(shù)據(jù),建議信號輸入頻率200hz到2Khz。觀察顯示器輸出,紅色波形為CH1輸入、藍(lán)色為CH2輸入、黃色網(wǎng)格最上面橫線代表5V,最下面橫線代表-5V,中間橫線代表0V,每個豎線間隔是10個采樣點。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601914 -

示波器

+關(guān)注

關(guān)注

113文章

6194瀏覽量

184527 -

AD

+關(guān)注

關(guān)注

27文章

868瀏覽量

150171 -

AD7606

+關(guān)注

關(guān)注

6文章

48瀏覽量

23289 -

紫光同創(chuàng)

+關(guān)注

關(guān)注

5文章

82瀏覽量

27488

發(fā)布評論請先 登錄

相關(guān)推薦

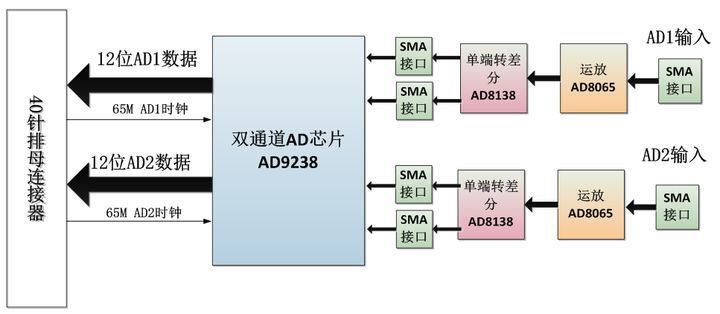

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第十七章】AD實驗之AD9238波形顯示

2024新品|紫光同創(chuàng)盤古系列FPGA開發(fā)板套件,100%國產(chǎn)化方案

國產(chǎn)FPGA介紹-紫光同創(chuàng)

模數(shù)轉(zhuǎn)換器設(shè)計指南第十八版

紫光同創(chuàng)簡介

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板,接口豐富,高性價比

紫光同創(chuàng)FPGA開發(fā)套件,高性能國產(chǎn)FPGA方案

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章Hello World(下)

AD7606應(yīng)用筆記

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第十八章】AD實驗之AD7606波形顯示

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第十八章】AD實驗之AD7606波形顯示

評論